The back to back converter control and design

Anders Carlsson

$\mathrm{May}\ 22,\ 1998$

## The Back-to-back converter control and design

Copyright © 1998 Anders Carlsson

Published by: Department of Industrial Electrical Engineering and Automation Lund Institute of Technology Box 118 S-221 00 Lund Sweden

http://www.iea.lth.se/

Printed in Sweden by Reprocentralen, Lund

ISBN: 91-88934-08-X

## Contents

| 1  | Intr | roduction                                    | 5         |

|----|------|----------------------------------------------|-----------|

|    | 1.1  | History                                      | 5         |

|    | 1.2  | Converter harmonics                          | 7         |

|    | 1.3  | The back-to-back converter                   | 10        |

|    | 1.4  | The controller hardware                      | 12        |

|    | 1.5  | Thesis outline                               | 14        |

| Ι  | Ba   | ack-to-back converters                       | 15        |

| 2  | Mo   | delling                                      | 17        |

|    | 2.1  | The three-phase converter                    | 18        |

|    | 2.2  | The equivalent four-quadrant DC/DC-converter | 27        |

| 3  | Ana  | alysis                                       | 31        |

|    | 3.1  | Controller loop                              | 31        |

|    | 3.2  | Transient response                           | 38        |

|    | 3.3  | Energy transients                            | 45        |

| 4  | Des  | 9                                            | <b>51</b> |

|    | 4.1  | Line filter                                  | 51        |

|    | 4.2  | DC-link capacitor limit                      | 53        |

|    | 4.3  | Brake chopper                                | 57        |

|    | 4.4  | Conclusion                                   | 58        |

| II | C    | ontroller hardware                           | 61        |

| 5  | A N  | MIMO control computer                        | 63        |

## CONTENTS

|   | 5.1                     | Overview                       | 63 |

|---|-------------------------|--------------------------------|----|

|   | 5.2                     | Functional description         | 69 |

|   | 5.3                     | Physical implementation        | 85 |

|   | 5.4                     | Future versions                | 86 |

| 6 | $\mathbf{A} \mathbf{s}$ | ix-phase pulse-width modulator | 89 |

|   | 6.1                     | Functional description         | 89 |

|   | 6.2                     | Hardware and Firmware          | 94 |

|   | 6.3                     | Conclusion                     | 98 |

## List of Figures

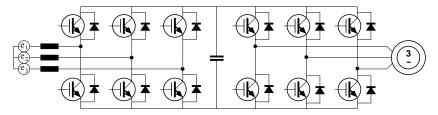

| 1.1 | Back-to-back converter                                                 | 10 |

|-----|------------------------------------------------------------------------|----|

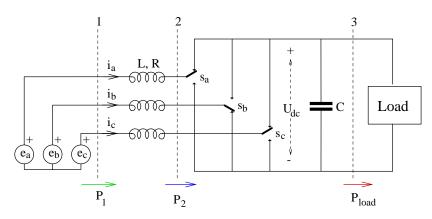

| 2.1 | Three-phase converter with general load                                | 18 |

| 2.2 | Averaging of a two-quadrant switch                                     | 19 |

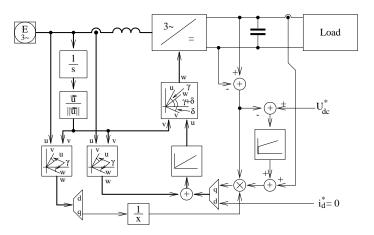

| 2.3 | Simplified diagram of the controller structure                         | 23 |

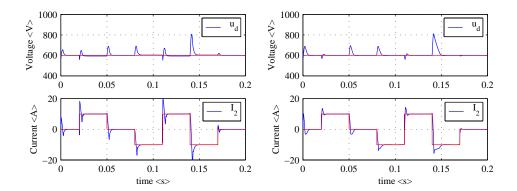

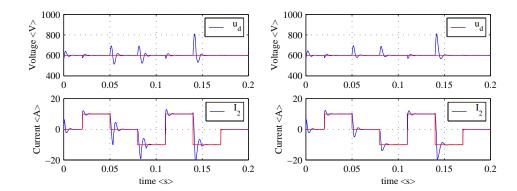

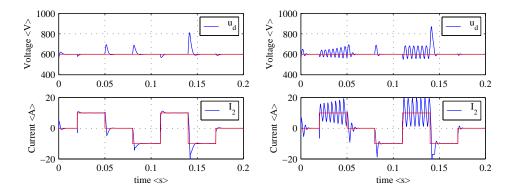

| 2.4 | Performance of cascaded PE+PI (left) versus cascaded                   |    |

|     | PIE+P (right) controllers                                              | 25 |

| 2.5 | Simple saturation (left) versus proposed saturation (right)            | 26 |

| 2.6 | Limited (left) versus unlimited voltage controller output.             | 27 |

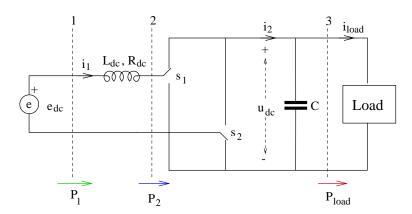

| 2.7 | Four-quadrant $DC/DC$ boost converter with general load .              | 28 |

| 3.1 | Stability depending on $k_u$                                           | 36 |

| 3.2 | Stability depending on $Ti$                                            | 36 |

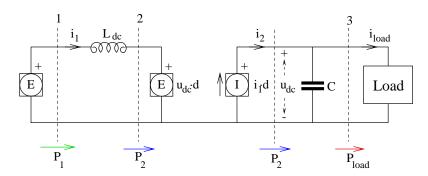

| 3.3 | Time-averaged model of the circuit in figure 2.7                       | 39 |

| 3.4 | Time-averaged model of the circuit used for analysis of                |    |

|     | energy transients                                                      | 45 |

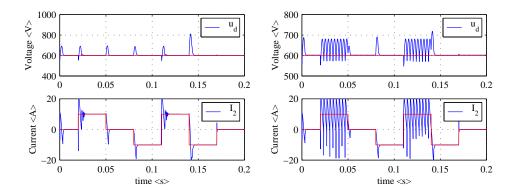

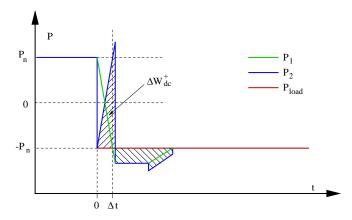

| 3.5 | Input power and load power consumption during trans-                   |    |

|     | ition from full generation to full motoring, for $d=0.5.$              | 46 |

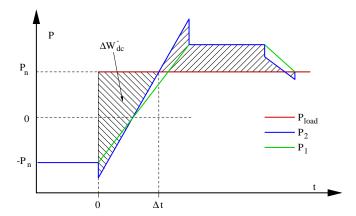

| 3.6 | Input power and load power consumption during trans-                   |    |

|     | ition from full generation to full motoring, for $d = -1$              | 46 |

| 3.7 | Input power and load power consumption during trans-                   |    |

|     | ition from full motoring to full generation for $d = 1$                | 47 |

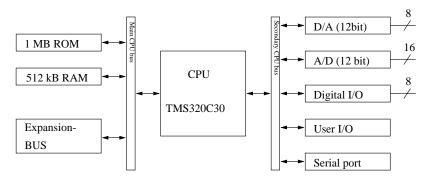

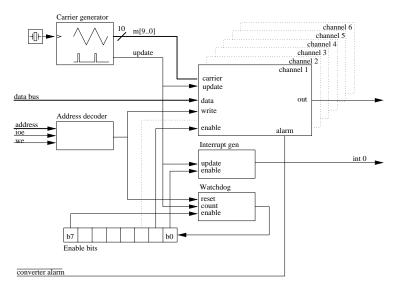

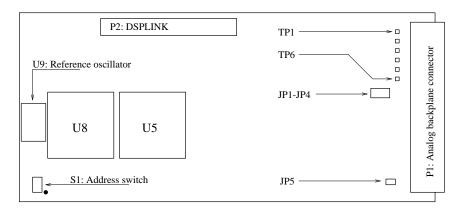

| 5.1 | IEA-MIMO block diagram                                                 | 70 |

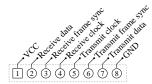

| 5.2 | Pinout for $\ensuremath{TMS320c30}$ serial port connectors P7 and P8 . | 73 |

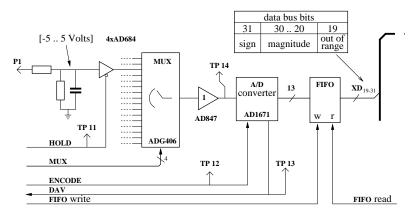

| 5.3 | Analog input signal path of IEA-MIMO                                   | 76 |

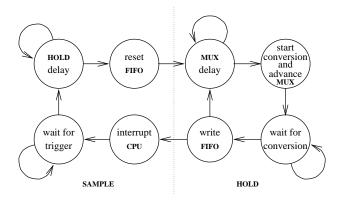

| 5.4 | State machine controlling A/D-conversion on IEA-MIMO                   | 77 |

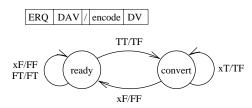

| 5.5 | Asynchronous adapter machine for the A/D-converter                     | 78 |

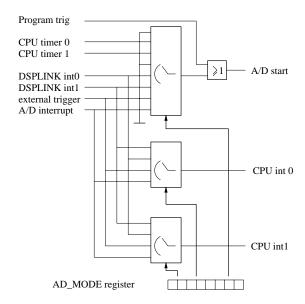

| 5.6 | A/D trigger and CPU interrupt logic                                    | 78 |

## LIST OF FIGURES

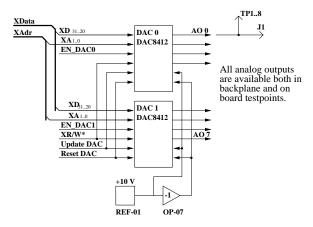

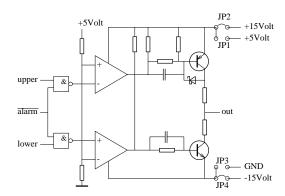

| 5.7  | IEA-MIMO analog output circuit                                 | 79 |

|------|----------------------------------------------------------------|----|

| 5.8  | IEA-MIMO backplane connector P1                                | 81 |

| 5.9  | IEA-MIMO on-board (internal) i/o connector P4                  | 82 |

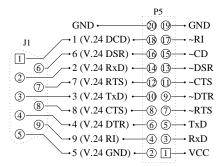

| 5.10 | IEA-MIMO communication port interface connectors P5            |    |

|      | and J1                                                         | 82 |

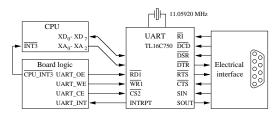

| 5.11 | IEA-MIMO communication port circuit diagram                    | 83 |

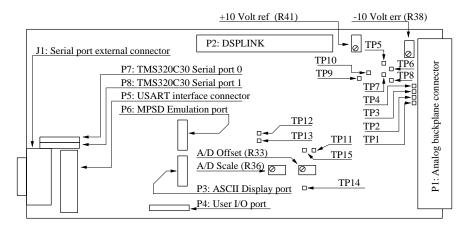

|      | IEA-MIMO connectors, test points and trim points               | 85 |

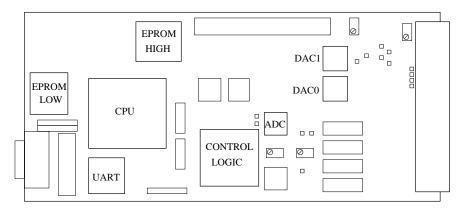

| 5.13 | IEA-MIMO main components                                       | 86 |

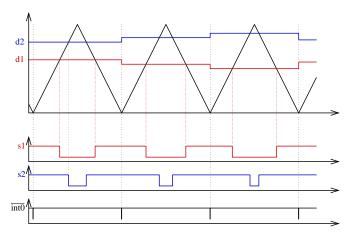

| 6.1  | Example on pulse-width modulation with a triangle-wave carrier | 90 |

| 6.2  | Block diagram for the complete IEA-PWM6 modulator              |    |

|      | board                                                          | 91 |

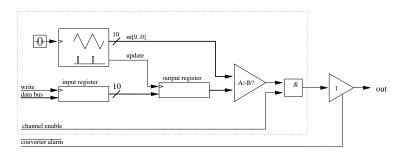

| 6.3  | Block diagram for one channel of the IEA-PWM6 modulator        | 91 |

| 6.4  | Placement of main components on IEA-PWM6                       | 94 |

| 6.5  | IEA-PWM6 backplane connector                                   | 95 |

| 6.6  | IEA-PWM6 output stage                                          | 96 |

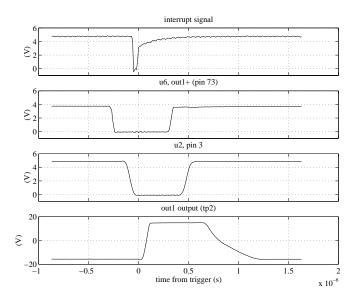

| 6.7  | Signal delays in the IEA-PWM6 modulator                        | 99 |

|      |                                                                |    |

## List of Tables

| 1.1        | Allowed harmonic voltage distortion in general (IEC 1000-2-2) and industrial (IEC 1000-2-4) distribution networks . | 8        |

|------------|---------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | Allowed current harmonic emissions for equipment connected to common distribution networks                          | 8        |

| 2.1<br>2.2 | Simulation parameters                                                                                               | 18<br>30 |

| 3.1<br>3.2 | Voltage deviations for the simulation example Energy taken up by the DC-link                                        | 44<br>50 |

| 4.1        | Line inductance-power product for $E_h = 400, T_{sw} = 100 \mu s$                                                   | 53       |

| 4.2        | Capacitor size per nominal converter power in $\mu F/kW$                                                            | 55       |

| 4.3        | DC-link capacitor size required to limit positive voltage transients.                                               | 56       |

| 4.4        | DC-link capacitor size required to limit negative voltage transients.                                               | 57       |

| 4.5        | Transient energy consumed in brake resistor in Joule per nominal converter power in kW                              | 58       |

| 5.1        | Algorithm complexity                                                                                                | 64       |

| 5.2        | IEA-MIMO memory map                                                                                                 | 72       |

| 5.3        | IEA-MIMO D/A converter register map                                                                                 | 80       |

| 5.4        | 16c750 Uart registers on IEA-MIMO                                                                                   | 83       |

| 6.1        | IEA-PWM6 output voltage jumper settings                                                                             | 92       |

| 6.2        | IEA-PWM6 register set                                                                                               | 93       |

| 6.3        | IEA-PWM6 base address settings                                                                                      | 94       |

## **Preface**

This thesis covers work I have carried out at the department of Industrial Electrical engineering and Automation in a project on power-grid friendly power converters. The main subject is the DC-link capacitor in back-to-back converters, but the main part of the work is the design of a control computer for power conversion.

My interest for power converter control started in late 1992 while I was completing my masters thesis. I was looking for an application for the real-time kernel I had designed, and controlling a power converter was suggested by Dr Mats Alaküla. The experience from this work inspired thoughts on the ideal controller hardware for electrical drive research. However, at that time there was no financial support for the development of such hardware. In 1994 an opportunity arose to design this computer when a project on power-grid friendly converters was initiated by Dr Alaküla.

It is a great pleasure to complete this thesis. If, at some point in the future, back-to-back power converters become economically feasible I hope the analysis and the design ideas presented in this thesis will be of good use.

## Acknowledgements

First of all, I would like to thank my supervisor, Prof. Mats Alaküla. Without his work on financial support, this project would never have started. He has also raised prudent questions regarding reliability and safety issues.

For discussions and comments I am grateful to Åke Christensson at ADTranz, Västerås, Sweden (previously at ABB Corporate Research, Västerås, Sweden), Prof. Lars Norum at the Norwegian Institute of Technology, Trondheim, Norway, Ole Morten Stangvik at the Norwegian Institute of Technology, Trondheim, Norway, Bengt Bengtsson at the department of Applied Electronics, Lund Institute of Tecnology, Lund, Sweden and Tore Svensson at Högskolan i Skövde, Skövde, Sweden.

I would also like to thank Jonas Forsberg at the Department of LTH-Malmö. His input on programmable logic was invaluable. Bertil Lindvall at the Department of Information Technology has given me access to their circuit programmer, many thanks.

For building and partly designing the wire-wrapped control computer prototype I am indebted to Svante Andersson and Peter Franz. The prototype had over 400 connections and thanks to their expertise, the prototype worked almost immediately. Thanks also to Johan Bengtsson and Anders Stenudd, who designed and built the back-to-back AC/AC converter which I have used for experiments and demonstrations.

The personnel at IEA has been very supportive. In particular Getachew Darge and Mansour Mojtahedi (now at Högskolan i Karlskrona-Ronneby) who assembled the electronics and maintained the workshop. Their demand for perfect drawings improved the quality of my designs. Bengt Simonsson is an outstanding purchaser and always helpful with anything practical.

Finally I would like to thank my fellow graduate students. They

are an important part of the creative research environment at IEA that makes it fun to go to work. Dr Gunnar Lindstedt got me started with the electronics CAD system. Morten Hemmingson maintains the IATEXinstallation and Dr Ulf Jeppsson carefully maintains the UNIX system. Sven-Göran Bergh (now at Industrial Communication) is always ready for a big laugh, or a good hack, or both.

This work has been financially supported by ELFORSK, within the Elektra research programme, together with ABB Corporate Research, whose kind support is gratefully acknowledged.

## Chapter 1

## Introduction

More than half of the electric energy production in Sweden is consumed in electrical drives. An increasing number of them are power electronically controlled variable speed drives. Using variable speed drives is advantageous. In many applications, such as pump drives, a variable speed drive can pay back the purchase in a single year, just from energy savings.

One drawback of conventional variable speed drives, however, is the large content of low frequent line-current harmonics due to the diode rectifier on the line side. For a wide use of variable speed drives, care must be taken to limit these low order harmonics in the utility grid. Passive filters, or other rectifier solutions are available to solve these problems.

One possible solution, studied in this thesis, is the back-to-back converter which has a second transistor bridge on the line side instead of the diode rectifier. This approach eliminates the main drawback of diode rectifiers and introduces a number of advantages like increased dc link voltage and minimized energy storage as well as active filtering and reactive power compensation capabilities.

## 1.1 History

Around the year 1960, static (electronic) power converters were scarce, though not entirely new. Six years earlier, the first commercial HVDC<sup>1</sup>

$<sup>^{1}\</sup>mathrm{HVDC}=\mathrm{High}$  Voltage, Direct Current.

power line in the world, between the Swedish mainland and the island of Gotland, had been completed. The mercury arc valve had for several years been used for high power applications (such as HVDC) but the silicon thyristor was invented and already usable for megawatt power levels. Several companies were working on static power converters for different applications. For instance, ASEA was working on the Rc series engines for the Swedish state railways, which employs thyristor-based power converters and DC machines with separate excitation to improve traction performance.

In the following years, static power converters spread through the industry. Not rapidly though, since the cost of the converter was too high to motivate its use in all but the most demanding applications. Furthermore, most power system engineers questioned the reliability of variable speed drives, a situation that remained unaltered as late as the 1980s.

#### Line-commutated converters

In the 1960s power converters connected to a AC power grid were line commutated; the individual valves in the converter bridge are switched on when the voltage across is positive and a gate pulse is applied, thereafter switched off when the current [flowing through them] changes direction and the voltage across becomes negative.

A drawback with line commutated converters, apart from cycloconverters, is that they cannot be used to feed an induction machine. Furthermore, a synchronous machine must be rotating before the converter can operate. Another problem is the high levels of low-order harmonics in the line current.

#### Force-commutated PWM converters

By the end of the 1960s, it was possible to build power converters in the kilowatt range with bipolar transistors, instead of thyristors. The transistor can be switched on and off regardless of the current flowing through it, so the converter can be made force-commutated, instead of line commutated. A force commutated converter can have much faster control over its input current and output voltage, which gives it better performance. This property is useful in servo applications with high performance requirements.

The availability of force commutated converters opened up new possibilities. For instance, it became possible to build variable speed drives

with induction machines and mastering the control of induction machines has been a major research topic since that time. Other application areas for force commutated power converters are synchronous machine drives, brushless DC drives and uninterruptible power supplies.

Since the early 1970s, solid state switching components suitable for force commutated power converters has developed quite far. Today, bipolar transistors have been replaced by IGBTs and MOSFETs, which simplifies the converter design and enables considerably higher switching frequencies. Transistorized power converters can be readily built for power levels up to a tens of megawatts.

#### 1.2 Converter harmonics

The deficiencies of the line commutated power converters are well known; Rather high low-order harmonics in the line current (depending on the existence of a DC-choke) and high demand for reactive power when the output voltage is low. These deficiencies are taken care of with filters and reactive power compensation. For small converters, though, the problem is mostly ignored. Filtering is applied only to minimize radio-frequency interference (RFI).

The three-phase diode bridge rectifier is only slightly better. Since the output voltage is uncontrolled, the current has the same shape as the line current of a fully saturated thyristor bridge. The fundamental power factor is thus unity, but the harmonics are still there.

Worst of all, single-phase rectifiers without a DC-choke have a line current shape which resembles a pulse-train. When connected between line and neutral, the combined effect of single-phase rectifiers connected to all three phases is large third-harmonic and ninth harmonic currents in the neutral line. The third harmonic in the neutral line can be four times as large as the fundamental line current, causing unwanted losses in the power lines.

### 1.2.1 Harmonics in the power grid

For small to medium sized power converters, the cost of harmonics-elimination is often considered too high compared to the limited influence the single power converter has on the power grid. This was a reasonable assumption fifteen years ago, since linear loads like incandescent lamps, induction machines, electric stoves, electric heaters and so forth dominated the load on the power grid.

|                | Percent of fundamental |              |              |                |

|----------------|------------------------|--------------|--------------|----------------|

| $\overline{k}$ | IEC 1000-2-2           | I            | EC 1000-2-4  |                |

|                |                        | Class 1      | Class 2      | Class 3        |

| 5              | 6                      | 3            | 6            | 8              |

| 7              | 5                      | 3            | 5            | 7              |

| 11             | 3.5                    | 3            | 3.5          | 5              |

| 13             | 3                      | 3            | 3            | 4.5            |

| 17             | 2                      | 2            | 2            | 4              |

| 19             | 1.5                    | 1.5          | 1.5          | 4              |

| 23             | 1.5                    | 1.5          | 1.5          | 3.5            |

| 25             | 1.5                    | 1.5          | 1.5          | 3.5            |

| > 25           | 0.2 + 12.5/k           | 0.2 + 12.5/k | 0.2 + 12.5/k | $5\sqrt{11/k}$ |

| THD            | 8                      | 5            | 8            | 10             |

Table 1.1: Allowed harmonic voltage distortion in general (IEC 1000-2-2) and industrial (IEC 1000-2-4) distribution networks

|         | IEC 1000-3-2      | IEC 1000-3-4  |

|---------|-------------------|---------------|

|         | $I_1 < 16A$       | $I_1 > 16A$   |

| k       | $I_k$ (A)         | $I_k/I_1$ (%) |

| 3       | 2.3               | 21.6          |

| 5       | 1.14              | 10.7          |

| 7       | 0.77              | 7.2           |

| 9       | 0.40              |               |

| 11      | 0.33              |               |

| 13      | 0.21              |               |

| 15 - 39 | $0.15 \cdot 15/k$ |               |

| 31      | _                 | 0.7           |

| > 33    | _                 | $\leq 0.6$    |

Table 1.2: Allowed current harmonic emissions for equipment connected to common distribution networks

Recent years, however, have seen an increased proliferation of relatively small electronic loads. Fixed speed drives for fans and pumps are replaced with variable speed drives. Heavy and repetitive tasks are now performed by industrial robots with servo drives. Pneumatic power tools are replaced by electric power tools with better performance. Rotary converters are replaced with solid-state converters. Inductive ballasts for fluorescent lamps are replaced by electronic ballasts.

Most of these relatively small loads has a diode rectifier connected to the power grid. In many cases the rectifier does not even have a DC-choke to smooth the line current. Each one of these loads is small compared to the total load. Despite this, they dominate the total load because of the large number of them. Further, since diode rectifiers operate synchronously, a large number of small rectifier loads will behave like a single large rectifier load.

The fact that electronic loads will eventually dominate the power consumption has led the EU<sup>2</sup> to implement restrictions on harmonic levels, see table 1.1 and 1.2. These restrictions prohibit the use of simple diode rectifiers, at least in principle. In practice, the rules do not impose any restrictions on normal household appliances, TV-sets, personal computers, power tools, industrial equipment etc.

#### 1.2.2 Elimination of harmonics

The high level of the low-order harmonics generated by line commutated rectifiers has made engineers and scientists develop methods to reduce the influence on the power grid or to eliminate the problem entirely. Some of these methods are:

- Filters, both LCL, and multiple series resonant links

- Third harmonic injection

- Twelve-pulse operation

- Multi-level rectifiers

- Force commutated rectifiers (e.g PWM-rectifiers)

All of these methods imply higher cost for the power converter. Some of the methods also result in a heavier and more voluminous converter.

<sup>&</sup>lt;sup>2</sup>The European Union

For certain applications (e.g. HVDC transmission), elimination of low-order harmonics is required by the utility. Because of the high power levels, these applications are implemented with line commutated rectifiers. Consequently, these plants have large filter yards. The filters increase the cost for the plant, but not so much that the plant cannot be profitable.

In most cases though, elimination of the line current harmonics is not considered economical, or even necessary. In the future, LVDC and MVDC distribution might supersede the three-phase system for feeding individual drives in industrial plants. It is probably cheaper to eliminate line current harmonics from a single large rectifier feeding an entire plant or factory, than having filters and force commutated rectifiers on every single drive throughout the plant.

## 1.3 The back-to-back converter

Figure 1.1: Back-to-back converter

The back-to-back converter is hinted at in the above discussion on line current harmonics. It consists simply of a force-commutated rectifier and a force-commutated inverter connected with a common DC-link, see figure 1.1. The properties of this combination are well known; the line-side converter may be operated to give sinusoidal line currents, for sinusoidal currents, the DC-link voltage must be higher than the peak main voltage, the DC-link voltage is regulated by controlling the power flow to the AC grid and, finally, the inverter operates on the boosted DC-link, making it possible to increase the output power of a connected machine over its rated power. Another advantage in certain applications is that braking energy can be fed back to the power grid instead of just wasting it in a braking resistor.

An important property of the back-to-back converter is the possibility of fast control of the power flow. By controlling the power flow to the grid, the DC-link voltage can be held constant. The presence of a fast control loop for the DC-link voltage makes it possible to reduce the size of the DC-link capacitor, without affecting inverter performance. In fact, the capacitor can be made small enough to be implemented with plastic film capacitors.

## 1.3.1 Issues associated with a small DC-link capacitor

The smallest size of the DC-link capacitor governed by the need to keep switch-frequent ripple at acceptable (i.e. small) levels. Fluctuations in the load cannot be smoothed in the converter, but must be accommodated by other means.

One alternative is to simply transfer such fluctuations to the power grid, but this may re-introduce the line-current harmonics the back-to-back converter is supposed to eliminate. However, load fluctuations will be random and thus relatively harmless compared to the in-phase harmonics generated by diode rectifiers.

Another alternative is to use the load itself. In a typical drive, the mechanical energy stored in the drive is several orders of magnitude larger than the electrical energy stored in the DC-link capacitor in a back-to-back converter. If the application does not need servo-class performance, there is no reason why the rotational speed cannot be allowed to fluctuate slightly. A pump drive, for instance, may be perfectly satisfactory if the speed regulation performance is comparable with a directly connected induction motor. (On the other hand, it may not. If a fixed-speed drive plus control valve is replaced with a variable speed drive, the variable speed drive must, in principle, have the same control performance as the control valve.)

The smallest feasible capacitor, chosen on the basis of switch-frequent voltage ripple, is too small to absorb (within voltage limits) even the [electromagnetic] energy stored in the main flux of a connected electrical drive. This places high demands on the controller which must be absolutely reliable. If the controller fails, the stored energy may raise the voltage of the DC-link beyond acceptable levels (enough to break the rectifier and/or the inverter). This may also result from circuit-breaker tripping.

To avoid DC-link overvoltage resulting from e.g controller failure,

also the back-to-back converter must have a voltage limiting device. This can consist of a traditional brake chopper. However, the *average* power rating needed is much smaller than for a conventional converter, although the peak power rating would probably be more than the rated power of the converter<sup>3</sup>. The chopper must be independent of the converter controller to be operational in event of a controller failure. Preferably, the chopper should operate directly from the DC-link voltage.

#### 1.4 The controller hardware

For almost a decade, the department of Industrial Electrical Engineering and Automation (IEA) has used an analog control system built in generic modules for research and education. A module consists of an 100x220mm curcuit board mounted in a Eurocard box with type F back plane connector. These modules make up a rather flexible system that easily can be arranged to create almost any kind of electric drive control system. A drawback, however, is that the analog system is unwieldy when researching controller structures and algorithms not anticipated in the analog design.

To increase the flexibility, IEA has used a control system built with a Macintosh II as host computer and two standard add-in boards from National Instruments together with the above mentioned analog system. This combination works well, and has been used for measurements in three PhD theses and four Master theses.

An important drawback of systems built into host computers, is the physical inflexibility. It is desirable for the control hardware to work as a "stand alone" unit, e.g in an industrial evaluation of a prototype. This is impractical with systems in host computers.

To be able to design research converters, and try them in practical environments, a programmable digital control unit that fits in the existing analog system is desirable.

#### 1.4.1 Controller demands

A self-contained digital control unit intended for electrical drives must, in terms of performance, be able to meet the requirements of demanding

$<sup>^3</sup>$ Peak power in this case means the power consumed by the resistor when connected to the nominal DC-link voltage.

drives. Control of a back-to-back converter was chosen as the reference application, given its demanding control tasks.

In the back-ti-bake converter case, the controller has to control two AC systems, versus one for frequency converters with diode rectifiers. In addition, the DC link voltage has to be controlled, adding another control loop to the system. The AC systems can be controlled with space-vector controllers, which may require angular transforms in software. In total, there may be seven or eight control loops and a state-space model with six or more states to update.

## 1.4.2 The control computer

The IEA-MIMO<sup>4</sup> control computer presented in this thesis is designed to meet the above mentioned reqirements. The IEA-MIMO is built around a TMS320C30 floating-point signal processor and has:

- sixteen analog inputs that are sampled in parallel and converted in less than sixteen microseconds total,

- eight analog outputs,

- nine digital/logic inputs/outputs,

- a standard serial communication port and

- a 16-bit expansion bus for additional I/O.

The IEA-MIMO can control a back-to-back converter at 10 kHz sampling frequency (this assumes a relatively simple space-vector controller for the load). Achieveing this performance does not require programming in assembly language; the C programming language can be used. Being able to program in high-level language is desirable, since it is easier to focus on algorithms when implementation details are taken care of by a compiler. It should be noted, however, that programming in assembly can result in a significantly faster program.

The IEA-MIMO does not include a pulse-width modulator. This is beacuse a pulse-width modulator may not be needed for a particular application. There is a large number of converter modulation methods and just including one of them would be too inflexible. Furthermore,

$<sup>^4</sup>$ MIMO stands for Multiple-Input, Multiple-Output. This is a property of the processes the IEA-MIMO is designed to control.

some converter types (notably matrix converters) cannot be controlled with a simple multi-channel pulse-width modulator.

To be able to control the back-to-back converter, a separate module with a six-channel pulse-width modulator, the IEA-PWM6 has been designed. This module is connected to the expansion bus of the IEA-MIMO. The IEA-PWM6 is a digital carrier-wave modulator with 10 bits resolution. All six channels use the same carrier which means the output pulses are synchronous and centered. The latter is advantageous for back-to-back converters, since the synchronous switching reduces the DC-link voltage ripple.

## 1.5 Thesis outline

This thesis has two parts. Part I deals with back-to-back power converters, particularly the DC-link capacitor. In chapter 2, models for the source (or line-side) converter and the structure of the control system are presented. Chapter 3 analyses the dynamic behaviour of the controlled (closed-loop) converter in the continuous-time domain. Analytical expressions for transient DC-link voltage deviations and DC-link energy impulses are derived. The implications drawn from the results in chapter 3 for back-to-back converter design are summarized in chapter 4.

Part II is a description of the digital control hardware that has been built in the course of this work. Chapter 5 describes the IEA-MIMO control computer in detail, including design issues, feature set, usage and performance. In chapter 6 the IEA-PWM6 six-phase pulse-width modulator is discussed.

# Part I Back-to-back converters

## Chapter 2

## Modelling

A central subject for this thesis is the DC-link in back-to-back voltage-source converters. A back-to-back converter consists of a line converter and a load converter. Usually, but not necessarily, both the line and load converters are three-phase voltage-source converters. Under certain assumptions the line converter can be viewed and analysed like a 4-quadrant DC/DC boost converter. The results from this analysis can then be applied to the three-phase converter.

In the voltage transient analysis, the load model is a DC current sink with stepwise changes of its power consumption. This model is chosen because it makes the analysis simpler; the current sink has infinite impedance, which makes it invisible in the system dynamics. The use of this model is valid under the assumption of small variations in the DC-link voltage.

The impedance of real loads is of course not infinity, not even necessarily positive. A load consisting of a four-quadrant converter driving a DC servo actually has negative impedance, or rather: it has constant power consumption, i.e  $P_{load} = U \cdot I = constant$ . This type of load is used in the analysis of energy transients taken up in the DC-link.

This chapter describes the three-phase converter, the structure of the controller for the converter and the models used for the analysis in chapter 3. The analysis is performed on a model of a DC/DC-converter. The conversion between the analyzed model and three-phase AC/DC converters is described in this chapter.

Figure 2.1: Three-phase converter with general load

| Parameter         | value | unit             |

|-------------------|-------|------------------|

| Nominal power     | 6     | kW               |

| Mains voltage     | 400   | V                |

| Mains frequency   | 50    | Hz               |

| Line inductors    | 7     | mH               |

| Line resistance   | 0     | $\Omega$         |

| DC-link capacitor | 100   | $\mu \mathrm{F}$ |

Table 2.1: Simulation parameters

## Simulation parameters

In this chapter and the following chapter, the theory is illustrated with simulations performed with SIMULINK and MATLAB. The model has been built using the above mentioned assumptions. Simulations has been performed with both DC/DC and AC/DC models.

If not otherwise stated, the model parameters used in simulations are according to table  $2.1\,$

## 2.1 The three-phase converter

The converter is an ordinary three-phase transistor bridge connected to the grid via "commutation inductors", see figure 2.2 on the facing page.

Figure 2.2: Averaging of a two-quadrant switch

The circuit can be thought of as a voltage-source inverter connected to the power grid.

The only difference between rectifier and inverter is the definition of power sign.

For the analysis, the circuit is modeled with averaged switch elements, see figure 2.2. This makes it possible to model the circuit in continuous time, by replacing all instantaneous values with their averaged counterparts. The switch frequency of the converter is assumed to be sufficiently high to make an average analysis valid. Sufficiently high in this case means that the switching ripple should be negligible compared to the averaged values.

#### 2.1.1 Mathematical model

The circuit in figure 2.1 on the facing page can be modeled by the following system:

$$\begin{cases}

L\frac{di_{a}}{dt} = e_{a} - u_{a} - Ri_{a} = e_{a} - u_{dc} \frac{2s_{a} - s_{b} - s_{c}}{3} - Ri_{a} \\

L\frac{di_{b}}{dt} = e_{b} - u_{b} - Ri_{b} = e_{b} - u_{dc} \frac{-s_{a} + 2s_{b} - s_{c}}{3} - Ri_{b} \\

L\frac{di_{c}}{dt} = e_{c} - u_{c} - Ri_{c} = e_{c} - u_{dc} \frac{-s_{a} - s_{b} + 2s_{c}}{3} - Ri_{c} \\

C\frac{du_{dc}}{dt} = s_{a}i_{a} + s_{b}i_{b} + s_{c}i_{c} - i_{load}

\end{cases}$$

(2.1)

where  $\{s_a, s_b, s_c\}$  indicate the switch positions of each phase; s can be either 0 or 1, with s = 1 indicating that the output is connected to the positive terminal of the DC-link capacitor.

The model in (2.1) is too detailed. By assuming fast switching, the

switch positions  $s_k$  can be replaced with the average  $d_k$  (d for duty-cycle). The equations then become:

$$\begin{cases}

L\frac{di_{a}}{dt} = e_{a} - u_{dc}\frac{2d_{a} - d_{b} - d_{c}}{3} - Ri_{a} \\

L\frac{di_{b}}{dt} = e_{b} - u_{dc}\frac{-d_{a} + 2d_{b} - d_{c}}{3} - Ri_{b} \\

L\frac{di_{c}}{dt} = e_{c} - u_{dc}\frac{-d_{a} - d_{b} + 2d_{c}}{3} - Ri_{c} \\

C\frac{du_{dc}}{dt} = d_{a}i_{a} + d_{b}i_{b} + d_{c}i_{c} - i_{load}

\end{cases} (2.2)$$

This method can be further extended for low frequency switching, by introducing states for the switch-frequent ripple amplitude, and so on if needed. This is, however, outside the scope of this thesis.

The model can be further simplified, using "space-vector" theory. The three-phase circuit is then transformed to a virtual two-phase circuit. After voltages and currents are transformed using the power-invariant Park transform, the following equations result

$$\begin{cases}

L\frac{di_{\alpha}}{dt} = e_{\alpha} - u_{\alpha} - Ri_{\alpha} \\

L\frac{di_{\beta}}{dt} = e_{\beta} - u_{\beta} - Ri_{\beta} \\

C\frac{du_{dc}}{dt} = \frac{u_{\alpha}}{u_{dc}}i_{\alpha} + \frac{u_{\beta}}{u_{dc}}i_{\beta} - i_{load}

\end{cases} (2.3)$$

which could also be written as a vector differential equation:

$$\begin{cases}

\mathbf{L}\frac{d\vec{i}}{dt} = \vec{e} - \vec{u} - \mathbf{R}\vec{i} \\

C\frac{du_{dc}}{dt} = \frac{\vec{u} \cdot \vec{i}}{u_{dc}} - i_{load}

\end{cases}$$

(2.4)

The states in this model vary sinusoidally with the line frequency. This means, that closed loop control of this system can not be considered as a standard problem, where the states are regulated around a steady state. To be able to apply standard linear control on steady-state variables, the model can be transformed from the fixed  $(\alpha, \beta)$  space to the rotating (d, q) space.

The (d,q) space is so oriented that the integral of the voltage vector points in the d-axis direction. This means that reactive current (assuming sinusoidal currents and voltages) is measured along the d-axis and active current is measured along the q-axis.

The  $(\alpha, \beta)$  to (d, q) transform is performed by subtracting the argument of the integrated line voltage vector (or line flux vector) from all vectors. If constant line-frequency f is assumed, i.e. (d, q)-space is rotating  $\omega = 2\pi f$  rad/s, the transformed model becomes:

$$\begin{cases}

L\frac{di_d}{dt} = -u_d - Ri_d - L\omega i_q \\

L\frac{di_q}{dt} = e_q - u_q - Ri_q + L\omega i_d \\

C\frac{du_{dc}}{dt} = \frac{u_d}{u_{dc}} i_d + \frac{u_q}{u_{dc}} i_q - i_{load}

\end{cases} (2.5)$$

Note that the transform introduces cross-coupling between the equations for the line current. Those terms introduce a nonlinearity in the model, which in some cases must be accounted for. In the derivation of the DC/DC-model parameters (section 2.2), however, it is assumed that the d-axis current is always regulated to zero, which makes the cross-term disappear from the active current equation.

### 2.1.2 Controller principles

There are many papers in the literature on control strategies for controlledcurrent three-phase rectifiers. Basically, the control problem is identical to synchronous-machine control. Since the converter control method is not the main point of this work, I will only give a brief description of some approaches found in the literature.

Hysteresis control Hysteresis control is also called tolerance-band or dead-band control. This controller type recognizes that voltage source converters can only have seven different output voltages. This leads naturally to a limit-cycle oscillation in the line current vector, which by the controller is kept inside a small area of some shape in the current vector space. The advantage is a known deviation from the current reference, but the switching pattern is more or less random, making it hard to predict converter losses.

Synchronous PI controllers This is one of the most popular control methods. The idea is to transform currents and voltages into a rotating reference frame, where the controlled currents are constant in "steady-state", use ordinary PI controllers on the transformed values, and transform the controller outputs back to the fixed reference frame. The drawbacks are the nonlinearities introduced in the transform and less than optimal control performance. The advantage is that it is simple to understand and simple to implement.

Minimum time control There is an excellent paper by Chui and Seui [?] who proposes a minimum-time controller. This controller is slightly better than synchronous PI control, which is shown with simulations and experiments in the paper. The controller uses reactive power impulses to improve the transient response. A later article by the same authors [?] applies the ideas to traditional synchronous PI controllers.

MRAS Model-reference adaptive control has been proposed by Take-shita and Matsui [?]. The approach has the advantage of not having to know the process parameters exactly, while still achieving good performance.

Synchronous PI controllers and minimum time control both work with averaged voltages and currents. The converter is controlled via a PWM-modulator that generates a switching pattern that corresponds to the desired average voltage.

In this thesis, the line current controller is assumed to be a synchronous PI controller. Its properties are well known in the power electronics area. Further, by assuming this type of controller, the three-phase converter can be modelled as two separate four quadrant converters. One for the active power and one for the reactive power. The reactive power is assumed to be zero, which means this part can be removed. See section 2.2 on page 27 for a DC-model of the converter.

#### 2.1.3 Controller structure

The structure of the control system for the power converter is outlined in figure 2.3 on the facing page. To simplify the figure, conversions between three-phase values and space vectors are not shown. The controller is divided in a line-current controller and a DC-link voltage controller,

Figure 2.3: Simplified diagram of the controller structure

operating in cascade. The line-current controller is a PI-controller that operates on vectors in (d,q) space. The parameters are identical for both components.

The DC-link voltage controller is a proportional controller with a feed-forward from the load current (called PE-controller for the rest of this thesis). The output from the voltage controller is scaled with the quotient between the DC-link voltage and the line voltage.

The outlined closed-loop system (designated PE+PI) can be described with the following differential equation system:

$$L\frac{di_d}{dt} = u_d - Ri_d - L\omega i_q$$

$$L\frac{di_q}{dt} = e_q - u_q - Ri_q + L\omega i_d$$

$$C\frac{du_{dc}}{dt} = \frac{u_d}{u_{dc}} i_d + \frac{u_q}{u_{dc}} i_q - i_{load}$$

$$\frac{dI_{i_q}}{dt} = \frac{K_{p_i}}{T_{i_i}} \left[ \frac{u_{dc}}{e_q} \left( K_{p_u} \cdot (u_{dc}^* - u_{dc}) + i_{load} \right) - i_q \right]$$

$$\frac{dI_{i_d}}{dt} = \frac{K_{p_i}}{T_{i_i}} \left[ i_d^* - i_d \right]$$

(2.6)

where  $I_{i_q}$  and  $I_{i_d}$  are the integral terms of the PI controllers and

$$u_d = K_{p_i} \left[ i_d^* - i_d \right] + I_{i_d} \tag{2.8}$$

$$u_q = K_{p_i} \left[ \frac{u_{dc}}{e_q} \left( K_{p_u} \cdot (u_{dc}^* - u_{dc}) + i_{load} \right) - i_q \right] + I_{i_q}$$

(2.9)

In the equations above,  $K_{p_i}$  and  $T_{i_i}$  is the proportional gain and integral time of the current controller, and  $K_{p_u}$  is the gain of the DC-link voltage controller.

One advantage of this controller is that it is easy to understand and analyse and the closed loop system is easily stabilized. Implementation is simplified by the lack of an integrator in the outher loop (see below). The obtainable performance, however is less than perfect. Since the integrator is in the inner loop, the control system cannot eliminate stationary errors in  $u_{dc}$  caused by errors in the feedforward path and/or resistance in the inductors.

A better control system is obtained if the integral part of the active current regulator,  $I_{i_q}$ , is removed and an integral term is inserted in the regulator for  $u_{dc}$ . This control system (called PIE+P onwards) eliminates stationary errors, but great care must be taken to eliminate integrator windup, which otherwise may cause large overshoots. However, if the anti-windup is properly designed, this controller has identical or better dynamic performance.

Without anti-windup, the proposed closed-loop system can be modelled with the following differential equations:

$$L\frac{di_d}{dt} = u_d - Ri_d - L\omega i_q$$

$$L\frac{di_q}{dt} = e_q - u_q - Ri_q + L\omega i_d$$

$$C\frac{du_{dc}}{dt} = \frac{u_d}{u_{dc}} i_d + \frac{u_q}{u_{dc}} i_q - i_{load}$$

$$\frac{dI_{u_{dc}}}{dt} = \frac{K_{p_u}}{T_{i_u}} [u_{dc}^* - u_{dc}]$$

$$\frac{dI_{i_d}}{dt} = \frac{K_{p_i}}{T_{i_t}} [i_d^* - i_d]$$

(2.10)

where  $I_{u_{dc}}$  is the integral part of the DC-link voltage controller, and

Figure 2.4: Performance of cascaded PE+PI (left) versus cascaded PIE+P (right) controllers

$$u_d = K_{p_i} \left[ i_d^* - i_d \right] + I_{i_d} \tag{2.12}$$

$$u_q = K_{p_i} \left[ \frac{u_{dc}}{e_q} \left( K_{p_u} \cdot (u_{dc}^* - u_{dc}) + I_{u_{dc}} + i_{load} \right) - i_q \right]$$

(2.13)

Figure 2.4 on the next page compares the two presented controller structures. The graph to the left is a simulation of the PE+PI controller structure, while the graph to the right is for the proposed PIE+P structure. The controllers are tuned for good performance. In both simulations, the load current feedforward has a 5% measurement error, which causes the steady state voltage error in the left graph.

Proper anti-windup for the integrator  $I_{u_{dc}}$  is not as straightforward as simply limiting the integrator. The integrator should remain unconstrained until the output voltage  $u_q$  reaches the converter limit, at which point the integrator should track the output voltage [?] [?]. For ordinary PI controllers this can be done according to:

$$\frac{dI}{dt} = \frac{K}{T_i} [y^* - y] - \frac{1}{T_r} [u^* - u]$$

(2.14)

$$u^* = K[y^* - y] + I (2.15)$$

$$u = \lim(u^*) \tag{2.16}$$

Where I is the integral part of the controller. In a discrete-time

Figure 2.5: Simple saturation (left) versus proposed saturation (right)

implementation, the tracking time constant  $T_r$  should be selected somwhere between  $2 \cdot T_s$  ( $T_s$  being the sampling interval) and  $T_i$ .  $T_r = T_i/2$  is a good alternative that is used in the simulations.

It remains to derive the limited output of the DC-link voltage controller. Equation (2.13) can be rewritten into:

$$\frac{e_q}{u_{dc}} \left[ \frac{u_q}{K_{p_i}} + i_q \right] - i_{load} = K_{p_u} \cdot (u_{dc}^* - u_{dc}) + I_{u_{dc}}$$

(2.17)

Where the RHS expression corresponds to (2.15) and the LHS expression corresponds to (2.16). Rewriting the integrator input (2.10) completes the anti-windup:

$$\frac{dI_{u_{dc}}}{dt} = \frac{K_{p_u}}{T_{i_u}} \left[ u_{dc}^* - u_{dc} \right] - \frac{1}{T_{r_u}} \left[ i_c^* - \frac{e_q}{u_{dc}} \left( \frac{u_q}{K_{p_i}} + i_q \right) - i_{load} \right]$$

where

$$i_c^* = K_{p_u} \cdot (u_{dc}^* - u_{dc}) + I_{u_{dc}}$$

Figure 2.5 illustrates the difference between a fixed saturation of the voltage controller output (with anti-windup) versus using the proposed saturation.

The controller parameters are the same in both graphs. The fixed limit and the controller parameters are chosen for a clear difference. The difference is smaller for a well tuned controller.

Figure 2.6: Limited (left) versus unlimited voltage controller output

Figure 2.6 on the next page illustrates the importance of limiting the active current command from the DC-link voltage controller. Cascaded proportional controllers are used in both simulations. Controller parameters are identical, but the gain is close to the stability limit (see section 3.1.2). In the left diagram, the voltage controller output is limited to a current corresponding to the nominal power of the converter, whereas it is unlimited to the right. The voltage collapses in the graph to the right since the unlimited current command grows faster than the input current, when the capacitor voltage drops.

It should be noted, however, that the controller parameters used in figure 2.6 is very close to the instability limit. Nevertheless, the simulation shows that the proposed anti-windup has to be combined with an absolute limit on the voltage controller output.

# 2.2 The equivalent four-quadrant DC/DC-converter.

The full three-phase converter in its present form can be studied and analyzed. The analysis can however be simplified by making some reasonable assuptions which allows modelling as a four-quadrant DC/DC boost converter. Furthermore, by establishing relationships between the three-phase converter circuit and the DC/DC boost converter the result of the DC/DC analysis can be transferred to the three-phase converter.

Figure 2.7: Four-quadrant DC/DC boost converter with general load

#### 2.2.1 Mathematical model

The circuit in figure 2.7 on the next page is used to model the active power dynamics of a three-phase converter. For this circuit to be a valid model, the following assumptions must be made:

- Balanced three-phase system.

- Zero reactive power Line currents always in phase with line voltages.

- No line current harmonics.

With these assumptions, the differential equation system (2.5) can be simplified to

$$\begin{cases}

L_{ac} \frac{di_q}{dt} = e_q - u_q - R_{ac}i_q \\

C \frac{du_{dc}}{dt} = \frac{u_q}{u_{dc}}i_q - i_{load}

\end{cases}$$

(2.19)

Where  $L_{ac}$  is the inductance and  $R_{ac}$  is the resistance of the inductors in the three-phase model, see figure 2.1. This model can be compared to the corresponding model for the DC/DC boost converter in figure 2.7:

$$\begin{cases}

L_{dc} \frac{di_1}{dt} = e_{dc} - u_1 - R_{dc} i_1 \\

C \frac{du_{dc}}{dt} = \frac{u_1}{u_{dc}} i_1 - i_{load}

\end{cases}$$

(2.20)

Where  $R_{dc}$  is the resistance of the inductor.

#### 2.2.2 Relation between the AC and DC models

The relationship between the three-phase AC converter and the DC converter should have good physical interpretation; voltage and current levels should be the "natural" for both cases. This means that the line voltage of the DC/DC converter should be the peak-to-peak main voltage of the AC line.

Table 2.2 on the next page lists the conversions between three-phase AC/DC converters and DC/DC boost converters. The conversion factor for the line inductance are derived by identifying parameters in the equations for the line current. Compare the current equations in (2.19) and (2.20)

$$L_{ac}\frac{di_q}{dt} = e_q - u_q - R_{ac}i_q \tag{2.21}$$

$$L_{dc}\frac{di_1}{dt} = e_{dc} - u_1 - R_{dc}i_1 \tag{2.22}$$

Since AC voltages are multiplied by a  $\sqrt{2}$  factor to get the corresponding DC voltage, (2.21) can be extended with  $\sqrt{2}$ , producing:

$$\sqrt{2}L_{ac}\frac{di_q}{dt} = \sqrt{2}e_q - \sqrt{2}u_q - \sqrt{2}R_{ac}i_q \qquad (2.23)$$

Since power should be the same in both models, i.e  $e_{dc} \cdot i_1 = \sqrt{2} e_q \cdot i_1 = e_q \cdot i_q$ , then  $i_q = \sqrt{2} i_1$ . Equation (2.23) then becomes:

$$2L_{ac}\frac{di_1}{dt} = e_1 - u_1 - 2R_{ac}i_1 \tag{2.24}$$

Equation (2.24) is the same as (2.22), but with AC parameters. The DC parameters can now be identified, yielding the result in table 2.2 on the following page.

| Parameter           | AC/DC                        | $_{ m DC/DC}$                                               |

|---------------------|------------------------------|-------------------------------------------------------------|

| Inactive $U_{dc}$   | $\hat{e}_h = \sqrt{2} * E_h$ | $e_{dc}$                                                    |

| Line voltage        | $E_h$                        | $e_{dc} = \sqrt{2} \cdot E_h$                               |

| Power               | $P_{ac} = e_h \cdot i_q$     | $P_{dc} = e_{dc} \cdot i_{dc}$                              |

| Line current        | $i_q$                        | $P_{dc} = P_{ac} \Rightarrow i_{dc} = \frac{i_q}{\sqrt{2}}$ |

| Inductance          | $L_{ac}$                     | $L_{dc} = 2L_{ac}$                                          |

| Inductor resistance | $R_{ac}$                     | $R_{dc} = 2R_{ac}$                                          |

Table 2.2: Conversion between AC/DC and DC/DC converters

#### 2.2.3 Controller structure

The controller for the DC/DC converter model is basically the same as for the AC/AC converter, without the reactive power part. The structure is further simplified by the lack of angular transforms.

## Chapter 3

## Analysis

In this chapter, the properties of an averaged model of a four quadrant DC/DC-converter are examined in detail. Section 3.1 examines the "small-signal" properties of the converter, when controlled by a state-feedback controller. The controlled system is non-linear, but the large-signal stability is not examined. Section 3.2 develops the large-signal transient response. The control-signal limitations disable the controller during power transient and the size of the output voltage transient is determined. In section 3.3 the output voltage is assumed to be held constant, and the amount of energy taken up by the DC-link voltage source during power transients is calculated.

## 3.1 Controller loop

As in the rest of this chapter, a continuous-time DC model of the converter is assumed. This is a serious simplification, since it implies that active and reactive line-current control is decoupled by synchronous PI controllers. Which is not the case, as is evident from equations (2.5), where the cross-coupling factor  $\omega L$  can be seen.

Nevertheless, the cascaded controller structure described in section 2.1.3 is applied to the continuous DC/DC converter. Referring to equations (2.10), (2.13) and figure 2.7, the closed-loop system is described by the following set of non-linear differential equations:

$$L_{dc}\frac{di_1}{dt} = e_{dc} - u_1 - Ri_1 (3.1)$$

$$C\frac{du_{dc}}{dt} = \frac{u_1}{u_{dc}}i_1 - i_{load} \tag{3.2}$$

$$\frac{dI_{u_{dc}}}{dt} = \frac{K_{p_u}}{T_{i_u}} \left[ u_{dc}^* - u_{dc} \right] \tag{3.3}$$

where

$$u_1 = K_{p_i} \left[ \frac{u_{dc}}{e_{dc}} \left( K_{p_u} \cdot (u_{dc}^* - u_{dc}) + I_{u_{dc}} + \hat{\imath}_{load} \right) - i_1 \right]$$

(3.4)

Note that the load feedforward,  $\hat{\imath}_{load}$  in (3.4), may differ from the actual load  $i_{load}$  in (3.2).

#### 3.1.1 Linearization

It is not straightforward to analyse this system. One way to handle the nonlinearities is to linearize around the operating point,  $(u_{dc_0}, i_{1_0})$  and then apply linear analysis methods to the resulting system. Here it gives some insight in how to select controller parameters to avoid local instability, but does not say anything about global stability.

Introduce the linearized state:

$$\tilde{u}_{dc} = u_{dc} - u_{dc_0} \Leftrightarrow u_{dc} = u_{dc_0} + \tilde{u}_{dc} \tag{3.5}$$

$$\tilde{i}_1 = i_1 - i_{1_0} \Leftrightarrow i_1 = i_{1_0} + \tilde{i}_1$$

(3.6)

Substituting (3.5) for  $u_{dc}$  and (3.6) for  $i_1$  in equations (3.1) to (3.4) yields:

$$L_{dc}\frac{d\tilde{i}_1}{dt} = e_{dc} - u_1 - R(i_{1_0} + \tilde{i}_1)$$

(3.7)

$$C\frac{d\tilde{u}_{dc}}{dt} = \frac{u_1}{u_{dc_0} + \tilde{u}_{dc}}(i_{1_0} + \tilde{i}_1) - i_{load}$$

(3.8)

$$\frac{dI_{u_{dc}}}{dt} = \frac{K_{p_u}}{T_{i.}} \left[ u_{dc}^* - u_{dc_0} - \tilde{u}_{dc} \right]$$

(3.9)

where

$$u_{1} = K_{p_{i}} \left[ \frac{u_{dc_{0}} + \tilde{u}_{dc}}{e_{dc}} \left( K_{p_{u}} \cdot \left( u_{dc}^{*} - u_{dc_{0}} - \tilde{u}_{dc} \right) + I_{u_{dc}} + \hat{\imath}_{load} \right) - i_{1_{0}} - \tilde{\imath}_{1} \right]$$

$$(3.10)$$

Linearizing around the setpoint, i.e  $u_{dc_0}=u_{dc}^*$  and  $i_{1_0}=i_{load}u_{dc}/e_{dc}$  simplifies (3.10) to

$$u_1 = K_{p_i} \left[ \frac{u_{dc_0} + \tilde{u}_{dc}}{e_{dc}} \left( K_{p_u} \cdot (-\tilde{u}_{dc}) + I_{u_{dc}} \right) - \tilde{\imath}_1 \right]$$

(3.11)

Substituting (3.11) into (3.7)–(3.9) yields:

$$L_{dc}\frac{d\tilde{i}_{1}}{dt} = e_{dc} - K_{p_{i}} \left[ \frac{u_{dc}^{*} + \tilde{u}_{dc}}{e_{dc}} \left( -K_{p_{u}}\tilde{u}_{dc} + I_{u_{dc}} \right) - \tilde{i}_{1} \right] - R\left( \frac{u_{dc}^{*} + \tilde{u}_{dc}}{e_{dc}} i_{load} + \tilde{i}_{1} \right)$$

(3.12)

$$C\frac{d\tilde{u}_{dc}}{dt} = \frac{1}{u_{dc}^* + \tilde{u}_{dc}} K_{p_i} \left[ \frac{u_{dc}^* + \tilde{u}_{dc}}{e_{dc}} \left( -K_{p_u} \tilde{u}_{dc} \right) + I_{u_{dc}} \right) - \tilde{\imath}_1 \right] (i_{1_0} + \tilde{\imath}_1) - i_{load}$$

(3.13)

$$\frac{dI_{u_{dc}}}{dt} = -\frac{K_{p_u}}{T_{i_u}}\tilde{u}_{dc} \tag{3.14}$$

Further expansion is straightforward, and is left as an exercise to the reader. To further simplify the calculations, an additional assumptions is made. If the load draws constant power instead of constant current (not unrealistic, see beginning of chapter 2),  $P_{load}$  can be substituted for  $(u_{dc}^* + \tilde{u}_{dc})i_{load}$ . After this substitution and elimination of non-linear terms the equations become more manageable:

$$L_{dc}\frac{d\tilde{\imath}_{1}}{dt} = e + \frac{K_{p_{i}}K_{p_{u}}u_{dc}^{*}}{e_{dc}}\tilde{u}_{dc} - \frac{K_{p_{i}}u_{dc}^{*}}{e_{dc}}I_{u_{dc}} + (K_{p_{i}} - R)\tilde{\imath}_{1} - R\frac{P_{load}}{e_{dc}}$$

(3.15)

$$C\frac{d\tilde{u}_{dc}}{dt} = -\frac{K_{p_i}K_{p_u}P_{load}}{e_{dc}^2}\tilde{u}_{dc} + \frac{K_{p_i}P_{load}}{e_{dc}^2}I_{u_{dc}} - \frac{K_{p_i}P_{load}}{u_{dc}^*e_{dc}}\tilde{i}_1 - \frac{P_{load}}{u_{dc}^*}$$

(3.16)

$$\frac{dI_{u_{dc}}}{dt} = -\frac{K_{p_u}}{T_{i_u}}\tilde{u}_{dc} \tag{3.17}$$

From this form it is possible to find the characteristic equation for the linearized system:

$$A(s) = s^{3} + \frac{K_{p_{i}}K_{p_{u}}L_{dc}P_{load} + (R - K_{p_{i}})Ce_{dc}^{2}}{L_{dc}Ce_{dc}^{2}}s^{2} + \frac{K_{p_{i}}K_{p_{u}}P_{load}}{L_{dc}Ce_{dc}^{2}} \left[\frac{L_{dc}}{T_{i_{u}}} + R\right]s + \frac{K_{p_{i}}K_{p_{u}}P_{load}R}{L_{dc}CT_{i_{u}}e_{dc}^{2}}$$

(3.18)

#### 3.1.2 Stability

Since  $P_{load}$  is a factor in all coefficients of the characteristic equation of the closed-loop system, the poles of the linearized system move around with the load of the converter. Consequently, the controller parameters must be chosen to keep all poles in the LHP of the complex plane under all load conditions.

The stability can be examined with Routh's algorithm. The coefficients of a third-order characteristic equation

$$a_0s^3 + b_0s^2 + a_1s + b_1 = 0 (3.19)$$

are arranged in a table according to:

$$\begin{array}{ccc}

a_0 & a_1 \\

b_0 & b_1 \\

a_1 - \frac{b_1}{b_0} a_0 & 0 \\

b_1 & 0

\end{array}$$

(3.20)

If all coefficients in the leftmost column are positive, the system is stable. If the coefficients of (3.18) are identified, the following stability criteria results:

$$\frac{K_{p_{i}}K_{p_{u}}L_{dc}P_{load} + (R - K_{p_{i}})Ce_{dc}^{2}}{L_{dc}Ce_{dc}^{2}} > 0$$

$$\frac{1}{L_{dc}Ce_{dc}^{2}} \left[\frac{L_{dc}}{T_{i_{u}}} + R\right] - \frac{R}{T_{i_{u}}\left(K_{p_{i}}K_{p_{u}}L_{dc}P_{load} + (R - K_{p_{i}})Ce_{dc}^{2}\right)} > 0$$

$$(3.23)$$

$$\frac{K_{p_{i}}K_{p_{u}}P_{load}R}{L_{dc}CT_{i_{u}}e_{dc}^{2}} > 0$$

$$(3.24)$$

Inequality (3.24) suggests that the closed-loop is unstable for either positive or negative power if  $R \neq 0$  or  $T_{i_u} < \infty$ . This is not necessarily the case for the real system. However, it indicates a problem, either with the linearization or with the non-linear closed-loop system.

The inequality (3.22) is more fundamental. (3.23) and (3.23) can be removed simply by assuming  $T_{i_u} = \infty$  and R = 0. (3.22) then becomes:

$$\frac{K_{p_i}K_{p_u}L_{dc}P_{load} - K_{p_i}Ce_{dc}^2}{L_{dc}Ce_{dc}^2} > 0 \iff (3.25)$$

$$|K_{p_u}L_{dc}P_{load}| < Ce_{dc}^2 \quad \text{and} \tag{3.26}$$

$$K_{p_i} < 0 \tag{3.27}$$

The proportional gain  $K_{p_u}$  can be parameterized in  $k_uC$ . This removes the capacitor size C from inequality (3.26), which becomes:

$$|k_u| < \frac{e_{dc}^2}{L_{dc}|\max(P_{load})|}$$

(3.28)

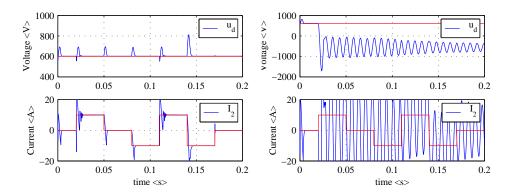

Figure 3.1 on the next page illustrates (3.28). The figure shows the result of two simulations with different  $k_u$ . In the left simulation,  $k_u = 0.95 \cdot e_{dc}^2/L_{dc}/\max|P_{load}|$  and in the right  $k_u = 1.05 \cdot e_{dc}^2/L_{dc}/\max|P_{load}|$ . The integral part in the controller is shut off, i.e.  $T_{i_u} = \infty$  and the gain of the current controller is  $K_{p_i} = -10^5 \cdot L_{dc}$ .

Figure 3.1: Stability depending on  $k_u$ .

Figure 3.2: Stability depending on Ti.

Figure 3.2 on the facing page illustrates stability depending on  $T_{i_u}$ . In the left graph,  $T_{i_u} = 1 \cdot 10^{-3} s$ , versus in the right graph  $T_{i_u} = 3 \cdot 10^{-4} s$ .  $k_u$  is  $0.3 \cdot e_{dc}^2 / L_{dc} / \max |P_{load}|$  and  $K_{p_i}$  is  $-10^5 \cdot L_{dc}$  in both figures.

#### 3.1.3 Stationary error

The closed loop system should eliminate stationary errors, both if there are errors in the  $\hat{\imath}_{load}$  feedforward and in presence of resistance in the line inductors.

In the stationary condition, all state derivatives are zero. The differential equations to then become the following equation system:

$$0 = e_{dc} - K_{p_i} \left[ \frac{u_{dc}}{e_{dc}} \left( K_{p_u} \cdot (u_{dc}^* - u_{dc}) + I_{u_{dc}} + \hat{\imath}_{load} \right) - i_1 \right] - Ri_1$$

(3.29)

$$0 = \frac{1}{u_{dc}} K_{p_i} \left[ \frac{u_{dc}}{e_{dc}} \left( K_{p_u} \cdot (u_{dc}^* - u_{dc}) + I_{u_{dc}} + \hat{\imath}_{load} \right) - i_1 \right] i_1 - i_{load}$$

(3.30)

$$0 = \frac{K_{p_u}}{T_{i_u}} \left[ u_{dc}^* - u_{dc} \right] \tag{3.31}$$

Substituting (3.31) into (3.30) and (3.29) yields:

$$0 = e_{dc} - K_{p_i} \frac{u_{dc}^*}{e_{dc}} \left( I_{u_{dc}} + \hat{\imath}_{load} \right) + (K_{p_i} - R) i_1$$

(3.32)

$$0 = \frac{K_{p_i}}{e_{da}} \left( I_{u_{dc}} + \hat{\imath}_{load} \right) i_1 - \frac{K_{p_i}}{u_{dc}^*} i_1^2 - i_{load}$$

(3.33)

Rewriting equation (3.32) gives the following expression

$$\frac{K_{p_i}}{e_{dc}} \left( I_{u_{dc}} + \hat{\imath}_{load} \right) = \frac{e_{dc} + (K_{p_i} - R)i_1}{u_{dc}^*}$$

(3.34)

The RHS of (3.34) can then be inserted into (3.33) which yields:

$$0 = \frac{e_{dc} + (K_{p_i} - R)i_1}{u_{dc}^*} i_1 - \frac{K_{p_i}}{u_{dc}^*} i_1^2 - i_{load}$$

$$= (e_{dc} + (K_{p_i} - R)i_1) i_1 - K_{p_i} i_1^2 - u_{dc}^* \cdot i_{load}$$

$$= e_{dc} i_1 - Ri_1^2 - i_{load} u_{dc}^*$$

(3.35)

Note that  $\hat{\imath}_{load}$  is cancelled, this means that a load current transducer with low precision has no effect on the stationary error.

Equation (3.35) has the solutions:

$$i_1 = \frac{e \pm \sqrt{e^2 - 4R \cdot P_{load}}}{2R} \tag{3.36}$$

If the solutions are real, the stationary error is eliminated. This is true for:

$$P_{load} < \frac{e^2}{4R} \tag{3.37}$$

#### 3.1.4 Discussion

Expression (3.28) has good physical interpretation. The controller gain parameter  $k_u$  has the dimension  $< s^{-1} >$ , and it can be viewed as the sampling frequency for a dead-beat controller, controlling the capacitor voltage. The LHS says that a large inductor makes a slow converter, but also that the inductor should be inversely proportional to the nominal power of the converter if performance is to be independent of nominal power.

The fact that the non-linear system is stable for both positive and negative power, despite (3.24) suggests that the analysis is insufficient. The stability of the closed loop system should be examined with methods for non-linear systems.

## 3.2 Transient response

This section is an analysis of the dynamic behaviour of the circuit during power transients. During transients, the controller output is limited by the converter. Wile the converter limits the control value, the circuit is essentially an uncontrolled, second order LC circuit. The differential equation for this circuit is solved analytically for stepwise changes in power flow. The output voltage exhibit transients whose size is only determined by component values together with voltage and power levels. The solution leads to design rules for the DC-link capacitor in a back-to-back converter.

Figure 3.3: Time-averaged model of the circuit in figure 2.7

#### 3.2.1 Circuit model

The circuit described in section 2.2 on page 27 can be modelled using the following equations:

$$\frac{du_{dc}}{dt} = \frac{1}{C}(d \cdot i_1(t) - i_{load}(t)) \tag{3.38}$$

$$\frac{di_1}{dt} = \frac{1}{L_{dc}} (d \cdot u_{dc}(t) - e_{dc}(t))$$

(3.39)

where  $d = d_1 - d_2$  is the difference in duty-cycle between the two switch legs of the circuit in figure 2.7 on page 28.

The voltage of the capacitor in the circuit,  $u_{dc}(t)$ , is assumed to be regulated to a quiescent voltage,  $U_{dc}$ . The source voltage is assumed to be constant, i.e  $e_{dc}(t) = E_{dc}$ .

Before the transients, the output power is  $P_0$ . At the start of the transients, the output power instantly changes to  $P^*$ . To simplify the analysis, a constant-current load is assumed. The load is assumed to be able to instantly change its power consumption. This makes the analysis simple and can also be considered a "worst case".

The controller for the converter is assumed to have a feed-forward from the load. The feedforward enables the controller to instantly respond to changes in output power.

#### 3.2.2 Case 1: positive transients

A positive transient is a (begins with a) positive, stepwise change in the output power of the converter. For a sufficiently large positive power step, the controller will saturate the duty cycle d to -1.

During the power step then, the converter states can be described by the following equations: (substitute d = -1 into (3.38) and (3.39))

$$\frac{du_{dc}}{dt} = \frac{1}{C}(-i_1 - i_{load}) \tag{3.40}$$

$$\frac{di_1}{dt} = -\frac{1}{L_{dc}}(u_{dc} + e_{dc}) \tag{3.41}$$

Together with the following initial and final conditions:

$$\dot{u}_{dc}(0) = \frac{1}{C} \left[ -i_1(0) - i_{load} \right]$$

$$= \frac{1}{C} \left[ -\frac{P_0}{E_{dc}} - \frac{P^*}{U_{dc}} \right]$$

(3.42)

$$i_1(0) = \frac{1}{L_{dc}} \left[ U_{dc} + E_{dc} \right] \tag{3.43}$$

$$i_1(t_{final}) = \frac{P^*}{E_{dc}} \tag{3.44}$$

Differentiating (3.40) and then inserting (3.41) into the resulting equation yields a second-order differential equation,

$$\frac{d^2 u_{dc}}{dt^2} + \frac{1}{L_{dc}C} \left[ u_{dc} + e_{dc} \right] = 0. {(3.45)}$$

Equation (3.45) is a lossless second-order differential equation. This class of differential equations can be solved by assuming a solution on the form

$$u_{dc} = A\cos\omega_c t + B\sin\omega_c t + f(t). \tag{3.46}$$

Inserting (3.46) into (3.45) yields

$$A\omega_c^2 \cos \omega_c t + B\omega_c^2 \sin \omega_c t =$$

$$= -\frac{1}{L_{dc}C} \left[ A \cos \omega_c t + B \sin \omega_c t + f(t) + e_{dc}(t) \right] \quad (3.47)$$

Assuming constant source voltage, i.e.  $e_{dc}(t) = E_{dc}$ , identification of terms in (3.47) gives the following solution parameters

$$\omega_c^2 = \frac{1}{L_{dc}C} \tag{3.48}$$

$$f(t) = -E_{dc} (3.49)$$

Inserting (3.49) and t = 0 into (3.46) and rearranging the gives:

$$A = u_{dc}(0) + e_{dc}(0) = U_{dc} + E_{dc}$$

(3.50)

Substituting the time-derivative of (3.46) into (3.40) gives:

$$-A\omega_c \sin \omega_c t + B\omega_c \cos \omega_c t = \frac{1}{C} \left[ -i_1(0) - i_{load} \right]$$

(3.51)

Inserting t = 0 yields:

$$B\omega_c = \frac{1}{C} \left[ -i_1(0) - i_{load} \right]$$

(3.52)

Which can be further rearranged into:

$$B = -\frac{1}{\omega_c C} [i_1(0) + i_{load}]$$

$$= -\sqrt{\frac{L_{dc}}{C}} \left[ \frac{P_0}{E_{dc}} + \frac{P^*}{U_{dc}} \right]$$

(3.53)

Here, the assumption of a constant-current load is important.

The coefficients of equation (3.46) have been found. It remains to find the solution for  $t_{final}$ . This, however, is quite simple. Equation (3.46) can be rewritten as:

$$u_{dc} = \sqrt{A^2 + B^2} \cos\left(\omega_c t + \arctan\frac{B}{A}\right) + f(t)$$

(3.54)

Differentiating (3.54), inserting the result into (3.40) and substituting the final condition (3.44) yields after rearranging:

$$i_1(t_{final}) = C \cdot \omega_c \sqrt{A^2 + B^2} \sin(*) - \frac{P^*}{U_{dc}} = \frac{P^*}{E_{dc}}$$

(3.55)

Solving (3.55) for (\*) gives:

$$(*) = \arcsin\left(\sqrt{\frac{L_{dc}}{C}} \frac{(E_{dc} + U_{dc})P^*}{E_{dc} \cdot U_{dc}\sqrt{A^2 + B^2}}\right)$$

(3.56)

The final value of  $u_{dc}$  can be found by substituting  $\omega_c t_{final}$ +arctan  $\frac{B}{A}$  for (\*) in (3.54). However, since  $cos(*) = \sqrt{1 - \sin^2(*)}$ ,  $u_{dc}(t_{final})$  can be found directly:

$$u_{dc}(t_{final}) = -E_{dc} + \sqrt{A^2 + B^2} \sqrt{1 - \frac{L_{dc}}{C} \frac{P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2(A^2 + B^2)}}$$

$$= -E_{dc} + \sqrt{A^2 + B^2 - \frac{L_{dc}}{C} \frac{P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2} - \frac{L_{dc}}{C} \frac{P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

$$= -E_{dc} + \sqrt{(U_{dc} + E_{dc})^2 + \frac{L_{dc}}{C} \frac{(P_0 U_{dc} + P^* E_{dc})^2 - P^{*2}(E_{dc} + U_{dc})^2}{E_{dc}^2 \cdot U_{dc}^2}}$$

#### 3.2.3 Case 2: negative power step

The derivation of the transient output voltage for a negative power step is similar to the derivation for positive steps. It is not necessary to repeat the derivation in full detail.

For sufficiently large negative power steps,  $P^* < P_0$ , the duty-cycle difference d is set to 1.

The equations are in this case:

$$\frac{du_{dc}}{dt} = \frac{1}{C}(i_1 - i_{load}) \tag{3.61}$$

$$\frac{di_1}{dt} = \frac{1}{L_{dc}} (u_{dc} - e) \tag{3.62}$$

Initial and final conditions:

$$\frac{du_{dc}(0)}{dt} = \frac{1}{C} \left[ i_1(0) - i_{load} \right]

= \frac{1}{C} \left[ -\frac{P_0}{E_{dc}} - \frac{P^*}{U_{dc}} \right]$$

(3.63)

$$\frac{di_1(0)}{dt} = \frac{1}{L_{dc}} \left[ -U_{dc} + E_{dc} \right] \tag{3.64}$$

$$i_1(t_{final}) = \frac{P^*}{U_{dc}} \implies \frac{du_{dc}(t_{final})}{dt} = 0$$

(3.65)

The final condition (3.65) may look a little strange. The point is that  $u_{dc}$  varies sinusoidally during the transient, and the peak value is reached when  $\frac{du_{dc}(t_{final})}{dt} = 0$ .

The parameters in the solution are:

$$A = u_{dc}(0) - e_{dc} = U_{dc} - E_{dc} (3.66)$$

$$B = \sqrt{\frac{L_{dc}}{C}} \left[ \frac{P_0}{e_{dc}} - \frac{P^*}{U_{dc}} \right] \tag{3.67}$$

$$f(t) = e_{dc}(t) = E_{dc} (3.68)$$

From the final condition,  $\dot{u}_{dc}=0$ , and (3.54) it is easy to see that the peak DC-link voltage is:

$$\hat{u}_{dc} = \sqrt{A^2 + B^2} + E_{dc}$$

$$= E_{dc} + \sqrt{(u_{dc}(0) - E_{dc})^2 + \frac{L_{dc}}{C} \left[ \frac{P_0}{E_{dc}} - \frac{P^*}{U_{dc}} \right]^2}$$

$$= E_{dc} + \sqrt{(U_{dc} - E_{dc})^2 + \frac{L_{dc}}{C} \cdot \frac{(P_0 U_{dc} - P^* E_{dc})^2}{E_{dc}^2 U_{dc}^2}}$$

(3.69)

| $P_0$  | $P^*$  | Voltage deviation |         |             |

|--------|--------|-------------------|---------|-------------|

| < kW > | < kW > | anal.             | DC sim. | AC+PWM sim. |

| -6.0   | 6.0    | 574.2             | 570.8   | 570.8       |

| 6.0    | -6.0   | 811.9             | 812     | 807         |

Table 3.1: Voltage deviations for the simulation example

#### 3.2.4 Discussion

The above expressions are quite accurate. The calculated voltage deviations are the same as the result of simulations and measurements. See table 3.1 for a comparison between analytical results and simulations. The converter parameters are:  $L_{ac}=7 \mathrm{mH} \Leftrightarrow L_{dc}=14 \mathrm{mH}, C=100 \mu \mathrm{F},$  and the voltages are:  $E_{dc}=400 \cdot \sqrt{2} \mathrm{V}$  and  $U_{dc}=600 \mathrm{V}$ .

The actual deviations obtained are slightly dependent on the controller parameters. If the controller has too low gain to saturate the converter, the deviations will be larger. Further, for a positive power step, the result is the solution of the differential equation at  $t_{final}$ , the time when the controller should stop saturating the converter. Depending on controller parameters, the deviation may be slightly larger in this case.

The calculations and simulations are performed on ideal (i.e. lossless) models, with stepwise load changes. The deviation in real converters will differ from the theoretical result, from two reasons:

- A real load may not be able to change stepwise, but rather ramps up and down. This is particularly true for electrical drives.

- Real converters have resistance in the line inductances.

The experimental result in table 3.1 gives a hint on the difference between theoretical and practical deviations.

As mentioned before, the results are valid for tree-phase converters. This is true under the assumption of traditional synchronous PID controllers. However, the three-pase converter has an additional degree of freedom; reactive power. The transient performance of the converter can be improved if the reactive power is allowed to temporarily raise during the transient. This has been the subject of papers by Chui and Sui [?, ?]. The obtained voltage deviation is smaller than the theoretical result, but the improvement is small with the converter parameters used by Chui and Sui.

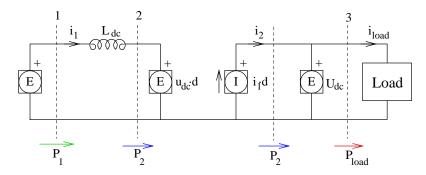

Figure 3.4: Time-averaged model of the circuit used for analysis of energy transients

Given voltage deviation limits and line filter inductor size, the results in this section can be used to determine the size of the DC-link capacitor in e.g. a back-to-back converter.

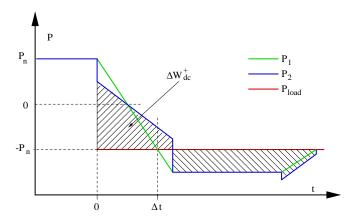

### 3.3 Energy transients

This section is a derivation of an expression for the energy received (or supplied) by the DC-link in a back-to-back converter. The idea is to assume constant DC-link voltage, and integrate the instantaneous power flowing into the voltage source during transitions between different power levels. The circuit model used in the analysis is shown in figure 3.4.

#### 3.3.1 A qualitative description

Before the transient, the power transferred by the converter is  $P_0$ , equal to the load power. At t=0, the load power instantly changes to  $P^*$ . The converter controller instantly changes the input voltage of the converter to drive the input current to the correct value.

The figures 3.5 and 3.6 illustrate a transition from full generation to full motoring, for two different duty-cycle values.

During the transient, energy  $(\Delta W_{dc})$  is lost from the DC-link to the load and the line inductors. After the desired input power level is reached, the lost energy must be regained, therefore the input power is raised above the output power for a short time.