# THEORETICAL ANALYSIS AND REDUCTION TECHNIQUES OF DC CAPACITOR RIPPLES AND REQUIREMENTS IN INVERTERS

By

Xi Lu

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

Electrical Engineering—Doctor of Philosophy

#### **ABSTRACT**

# THEORETICAL ANALYSIS AND REDUCTION TECHNIQUES OF DC CAPACITOR RIPPLES AND REQUIREMENTS IN INVERTERS

By

#### Xi Lu

DC link capacitor is an important component for many conventional topologies, such as three-phase voltage source inverter (VSI), H-bridge VSI and etc. However, it is usually very large, heavy and expensive. Therefore, minimization of the dc capacitor is an essential step towards developing and manufacturing compact low-cost inverter systems for high temperature operation, long life and high reliability. Traditionally, the dc capacitance has been determined according to empirical equations and computer simulations, which provides little insights into how to minimize the dc capacitor. In order to achieve an optimum minimization of the dc capacitor, an accurate theory to calculate the dc capacitor voltage ripple and current ripples must be developed first, then pulse-width modulation (PWM) and control techniques or topological improvements can be further developed to minimize both dc voltage and current ripples. This dissertation is mainly divided into two parts. First half is minimizing the capacitor ripple and requirements for three-phase VSI; while second half is for H-bridge VSI.

In the first half of the dissertation, it proposes an accurate theory of calculating the dc link capacitor voltage ripples and current ripples for inverters and PWM rectifiers. The results are analyzed and summarized into graphs according to the theory, which helps find the right capacitance value for a given voltage ripple tolerance and the rms ripple current that the capacitor has to absorb.

In hybrid electric vehicle (HEV) applications, the high voltage battery pack is connected to the dc link bus through a dc-dc converter. Based on the above-proposed theory, a PWM modulation method for the dc-dc converter is developed to further reduce the dc capacitor current ripples and requirements. To verify the proposed theory and PWM method, a 150 kW inverter prototype has been built. The comparison between the calculation result and experimental result shows that they are in close agreement.

For the second half of the dissertation, contributions for H-bridge inverters are made for photovoltaic and FACTs systems.

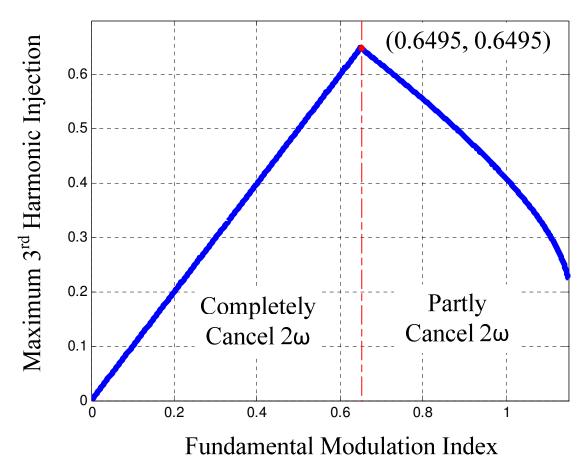

As the demand of the renewable energy increases every year, the photovoltaic (PV) systems have been playing an important part in supplying energy for the global consumption. In order to connect PV modules to the grid without inserting any bulky low frequency step-up transformers, the cascaded H-bridge multilevel inverters are utilized to increase the output voltage level up to the grid voltage (e.g. 13.8 kV). The  $2\omega$  harmonic component on the dc link side of the H-bridge inverters has long been a thorny problem, which requires a huge dc link capacitor bank to absorb this  $2\omega$  low frequency current ripple in order to maintain the dc link voltage ripple under a tolerable value. This dissertation presents a simple  $3^{\text{rd}}$  harmonic injection method for the cascaded H-bridge multilevel inverters for photovoltaic systems at unity power factor. This approach achieves a 40% to 50% reduction of the dc link capacitance, without adding any extra components or increasing the control complexity.

Same  $2\omega$  harmonic problem exists in FACTs devices, which is typically implemented by an H-bridge inverter. A new topology and control method are proposed to significantly reduce the dc capacitance to minimum by only adding a phase leg and an ac capacitor with the value of 1/10 of the original dc capacitance.

Dedicated to my Father and Mother: Jiming Lu and Xuri Shen

## **ACKNOWLEDGEMENTS**

First of all, I would like to give my heartfelt thanks to my dear advisor, Dr. Fang Z. Peng. Thank you very much for having me as one of your students. I really appreciate everything that you have done for me, your clear directions, your precious advices, and all your patient helps during the past years. I would not be able to achieve what I become today and finish all these works without you. I am so grateful and honorable of being your student.

Meanwhile, I am also very thankful to my committee members, Dr. Bingsen Wang, Dr. Mitra, and Dr. Guoming Zhu. Thank you for giving me all the impressive lectures from which I built up my knowledge base.

Many thanks go to my colleagues in PEMD lab, for valuable discussions, suggestions and selfless help, as well as priceless friendships. Special thanks go to Dr. Honnyong Cha for offering me great helps during my first 2 years of graduate study, thanks for helping me with the derivation of the dc capacitance theoretical calculation, and teaching me how to debug and built inverters. Many thanks go to Dr. Wei Qian, Dr. Dong Cao, Dr. Qin Lei, Dr. Shuitao Yang, Dr. Dan Wang, Dr. Julio Cesar Rosas-Caro and Dr. Craig Rogers for delightful technical discussions, research hints on the battery equalizer and experimental method of carrier-based modulation, and proofreading of my papers and thesis. Thanks to Dr. Shuai Jiang, Dr. Baoming Ge, and Dr. Shao Zhang for a lot of valuable discussions in all areas throughout my graduate study. Indeed thanks to Mr. Xianhao Yu, Dr. Zhenguo Gu, Mr. Yang Liu, Mr. Sisheng Liang, and Mr. Runruo Chen for the collaboration in the MW inverter project and the SSVC project during my last a couple of years in PElab. Finally, thanks to Dr. Lihua Chen, Dr. Yi Huang, Dr. Jianfeng Liu, Dr. Yuan Li,

Dr. Maosong Zhang, Dr. Junming Zhang, Dr. Jorge G. Cintron-Rivera, Mr. Joel Anderson, Dr. Uthane Supatti, Mr. Matthew Gebben, Mr. Sangmin Han, and Dr. Irvin Balaguer.

Finally, thanks from my deep heart go to my parents. Thank you for raising me up and teaching me everything. The love that I got from you is beyond expression.

# TABLE OF CONTENTS

| LIST OF TABLES                                                     |                                                |

|--------------------------------------------------------------------|------------------------------------------------|

| LIST OF FIGURES                                                    | X                                              |

| CHAPTER 1 DC Link Capacitors                                       |                                                |

| 1.1 Types of DC Link Capacitors                                    |                                                |

| • 1                                                                | 2                                              |

| 1.1.2 Film capacitor                                               |                                                |

|                                                                    |                                                |

| 1.3 Applications Using DC Link Capacitors                          | s and Outline of Dissertation6                 |

|                                                                    | 6                                              |

| 1.3.2 Single-Phase Inverters                                       |                                                |

| CHAPTER 2 Introduction of HEV Applicati                            | ons and Their DC Capacitors                    |

| 2.1 The Advantage of HEV in the Automot                            | ive Market                                     |

|                                                                    | 10                                             |

| 2.3 Power Electronics Challenge in HEV sy                          | ystems11                                       |

|                                                                    |                                                |

|                                                                    | Mode                                           |

|                                                                    |                                                |

|                                                                    |                                                |

|                                                                    | Converter and SPWM Inverter 16                 |

| •                                                                  |                                                |

| -                                                                  | onverter Control Strategies                    |

|                                                                    | pples and Harmonics of DC Capacitor 18         |

|                                                                    | OC-DC converter and SPWM Inverter to           |

| <u> </u>                                                           | 20                                             |

| CHAPTER 3 DC Capacitance and Current I SPWM Inverter/PWM Rectifier |                                                |

| 3.1 Basic Idea of Calculating DC Link Cap.                         | acitance2 <sup>2</sup>                         |

|                                                                    | 26                                             |

| 3.2.1 Switching Functions                                          |                                                |

| 3.2.2 Relationship between <i>Vdc</i> and <i>Vac</i>               |                                                |

| $\mathcal{E}$                                                      |                                                |

| <u>.</u>                                                           | citance30                                      |

|                                                                    | ne Same Power Factor and Modulation Index . 34 |

| 3.3.2 Maximum A-sec versus Power Fact                              | tor30                                          |

| 3.4    | Calculation of RMS Value of DC Current Ripple                                                           | 42       |

|--------|---------------------------------------------------------------------------------------------------------|----------|

| СНАН   | PTER 4 DC Capacitance Requirement of the Three-Phase Diode Rectifier                                    | 44       |

| 4.1    | Introduction                                                                                            |          |

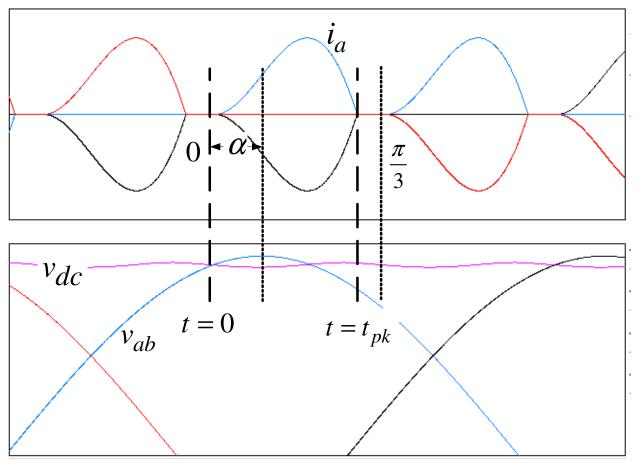

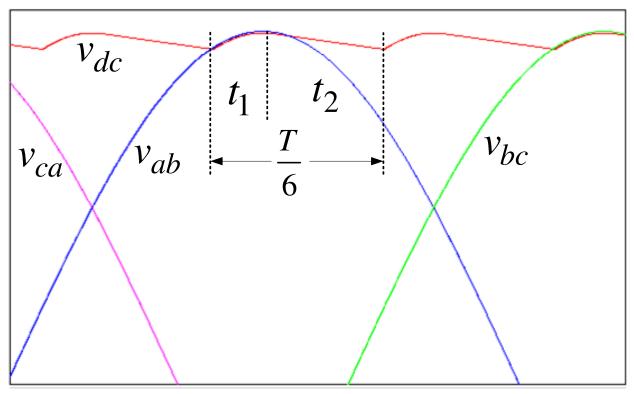

| 4.2    | Calculation of the Critical Inductance                                                                  |          |

| 4.3    | Calculation of Required DC Link Capacitance                                                             |          |

|        | 3.1 With No Line Inductance                                                                             |          |

|        | 3.2 With 0%~1.46% Line Inductance                                                                       |          |

| 4.     | 3.3 With Line Inductance Greater Than 1.46%                                                             |          |

| СНАН   | PTER 5 DC Capacitance Requirement of the Six-Step Inverter                                              | 57       |

| 5.1    | Simplified Configuration and System Parameters                                                          | 57       |

| 5.2    | Calculation of Required DC Link Capacitance                                                             |          |

| СНАН   | PTER 6 Prototype and Testing Results of SHEV Power Electronics Module                                   | 63       |

| 6.1    | Prototype                                                                                               | 63       |

| 6.2    | Test Results of Voltage Ripple                                                                          |          |

| 6.3    | Test Results of Current Ripple                                                                          | 71       |

|        | PTER 7 Minimizing the DC Capacitance between the DC-DC Converter and Ser—A Carrier Modulation Method    |          |

|        |                                                                                                         |          |

| 7.1    | Introduction                                                                                            |          |

| 7.2    | The Conditions Under Consideration                                                                      |          |

|        | <ul><li>2.1 Unity Modulation Index of the Inverter</li><li>2.2 Unity Power Factor of the Load</li></ul> |          |

|        | 2.3 Constant Duty Cycle for the Boost Converter                                                         |          |

|        | 2.4 Sinusoidal Inverter Output Currents                                                                 |          |

|        | 2.5 Analyze One of Six 60° Sectors                                                                      |          |

| 7.3    | The Analysis of the Ideal SPWM Inverter Input Current Waveform                                          |          |

| 7.4    | · · · · · · · · · · · · · · · · · · ·                                                                   |          |

| 7.     | 4.1 Sine Carrier Modulation Method                                                                      |          |

| 7.     | 4.2 Linear Carrier Modulation Method                                                                    | 87       |

| 7.5    | Theoretical Analysis of DC Link Current Ripple for Sine Carrier Modulation Me                           | ethod 91 |

| 7.     | 5.1 Basic Equations                                                                                     | 92       |

| 7.     | 5.2 Current Ripple Analysis                                                                             |          |

| 7.     | 5.3 Calculation Results                                                                                 |          |

| 7.6    | Experimental Results                                                                                    |          |

| 7.7    | Conclusion                                                                                              | 111      |

|        | PTER 8 Minimizing DC Capacitance Requirement of Cascaded H-Bridge Mu                                    |          |

| Invert | ters for Photovoltaic Systems by 3 <sup>rd</sup> Harmonic Injection                                     | 112      |

| 8.1    | Introduction                                                                                            |          |

| 8.2    | Theoretical Analysis of the DC Canacitance Reduction                                                    | 113      |

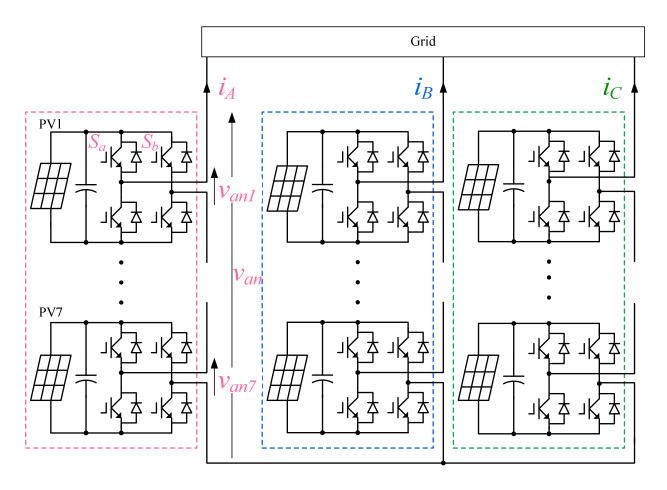

| 8.2    | .1 System Configuration                                            | 113         |  |

|--------|--------------------------------------------------------------------|-------------|--|

| 8.2    | .2 DC link current ripple without 3rd harmonic injection           | 115         |  |

| 8.2    | .3 DC link current ripple with 3rd harmonic injection              | 116         |  |

| 8.2    | * * *                                                              |             |  |

| 8.3    | Simulation Results                                                 |             |  |

| 8.4    | Conclusions                                                        |             |  |

| CHAP   | ΓER 9 Solid State Variable Inductor-Capacitor for Reactive Power C | ompensation |  |

| with M | inimum DC Capacitance                                              | 133         |  |

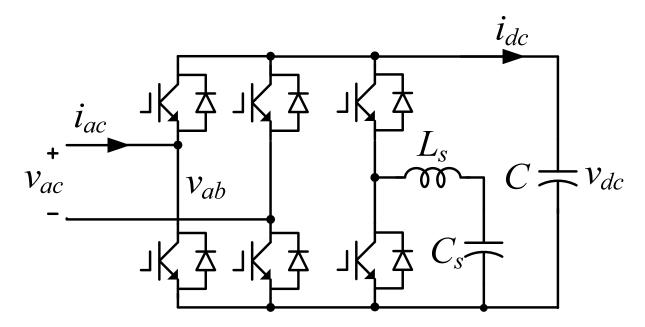

| 9.1    | Introduction                                                       | 133         |  |

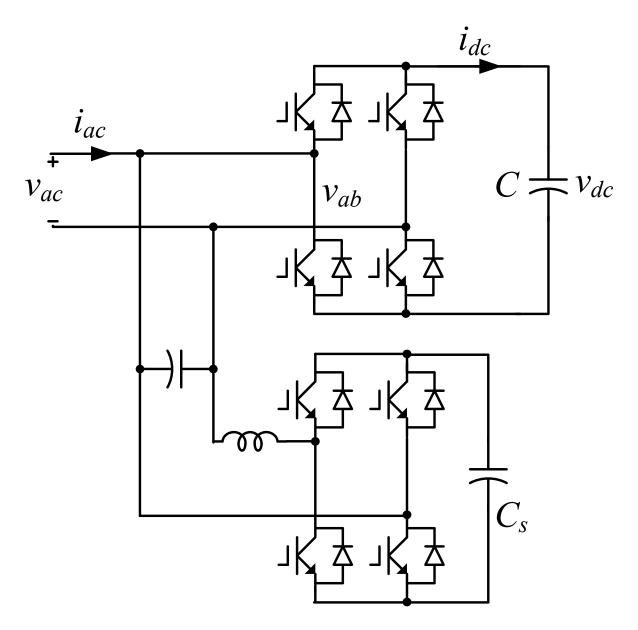

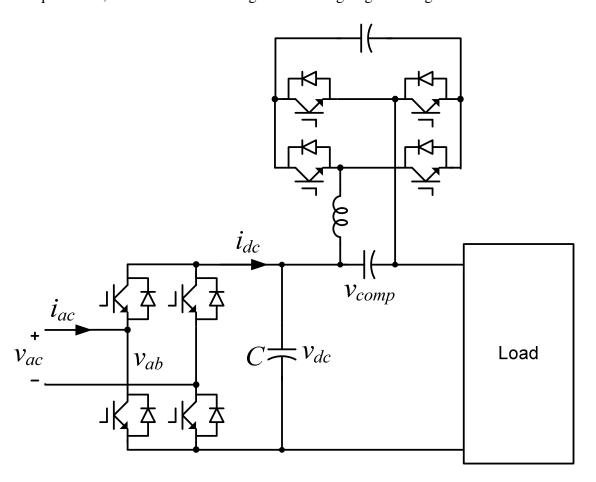

| 9.2    | Past Works                                                         |             |  |

| 9.3    | The Proposed Solid State Variable Inductor-Capacitor (SSVLC)       |             |  |

| 9.4    | Experimental Results.                                              |             |  |

| 9.5    | Conclusions                                                        |             |  |

| CHAPT  | ΓER 10 Contribution and Future Work                                | 159         |  |

| 10.1   | Contributions                                                      | 159         |  |

| 10.2   | Future Work                                                        |             |  |

| APPEN  | NDIX                                                               | 163         |  |

| BIBLIC | BLIOGRAPHY165                                                      |             |  |

# LIST OF TABLES

| Table 1.1 DC Link Capacitor Comparison between Film and Electrolytic [4]                                                   |

|----------------------------------------------------------------------------------------------------------------------------|

| Table 3.1 Expressions of $A \cdot sec (v_a > v_c > v_b)$                                                                   |

| Table 3.2 Simplified Expressions of $A \cdot sec(v_a > v_c > v_b)$                                                         |

| Table 3.3 The M at the maximum <i>A-sec</i> for each pf                                                                    |

| Table 5.1 The list of Inductance and Resistance Changing Base                                                              |

| Table 5.2 The list of Inserted Voltage source Amplitude and Phase Angle Based on Different Power Factor and Load Impedance |

| Table 6.1 The Configuration in the Prototype                                                                               |

| Table 6.2 Expreimental Result of Voltage ripple                                                                            |

| Table 6.3 Experimental Results of rms current of The Capacitor                                                             |

| Table 7.1 Circuit Parameters and Experimental Conditions                                                                   |

| Table 7.2 Simulation Data                                                                                                  |

| Table 7.3 Saber Simulation Result of The rms Value of The DC Link Capacitor's Ripple Current                               |

| Table 9.1 Expressions for ripple power on auxiliary inductor and capacitor for SSVL and SSVC                               |

# LIST OF FIGURES

| Figure 1.1 | Commercial electrolytic capacitors                                                                                                                                                                                                                                                                    | 3 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 1.2 | Commercial film capacitors                                                                                                                                                                                                                                                                            | 4 |

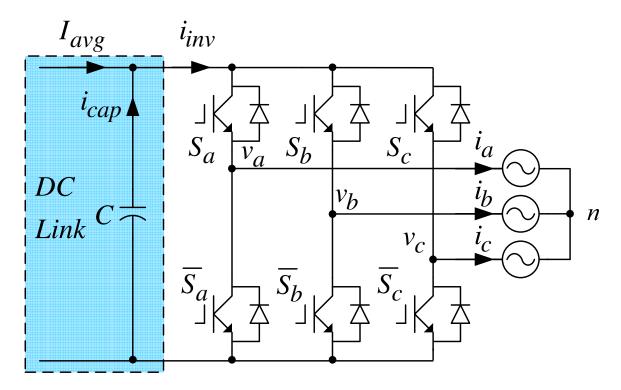

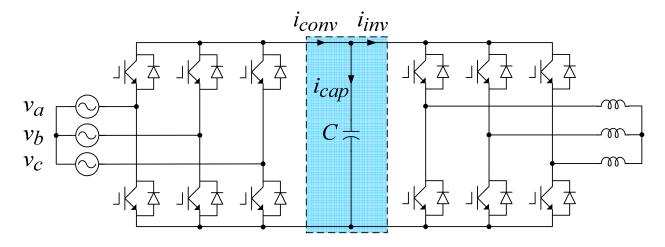

| Figure 1.3 | Typical three-phase inverter with dc link capacitor                                                                                                                                                                                                                                                   | 7 |

| Figure 1.4 | Typical single-phase inverter with dc link capacitor                                                                                                                                                                                                                                                  | 8 |

| Figure 2.1 | The power electronics function blocks of the series hybrid electric vehicle (SHEV) systems                                                                                                                                                                                                            | 1 |

| _          | The schematic of a three-phase inverter/PWM rectifier using SPWM with three-phase current sources as load                                                                                                                                                                                             |   |

| Figure 2.3 | The simplified equivalent circuit of the inverter under six-step operation 1                                                                                                                                                                                                                          | 4 |

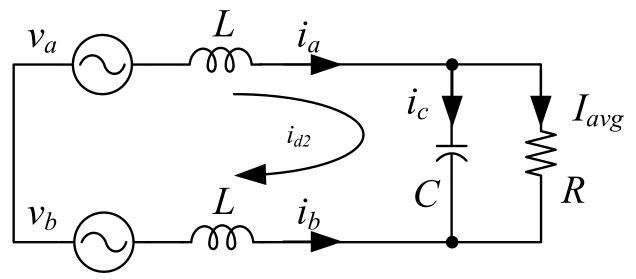

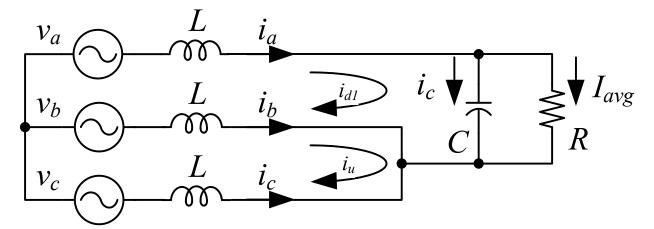

| _          | The schematic of a three-phase uncontrolled diode rectifier with line impedance on the ac side, and with dc link capacitor and resistive load on the dc side                                                                                                                                          | 5 |

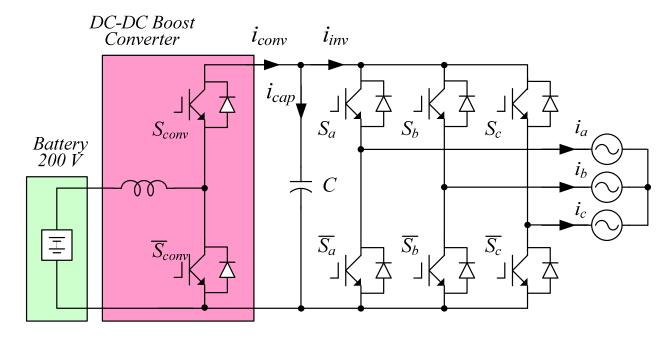

| Figure 2.5 | The schematic of a bidirectional dc-dc converter connected with a three-phase inverte with three-phase current sources as load                                                                                                                                                                        |   |

| Figure 2.6 | The schematic of a typical AC-DC-AC PWM converter system                                                                                                                                                                                                                                              | 8 |

| -          | The schematic of a three-phase inverter/PWM rectifier using SPWM with three-phase current sources as load                                                                                                                                                                                             |   |

| C          | Detailed PWM waveforms in two switching periods (a) sinusoidal reference and triangle carrier waveforms; (b) switching function of phase A; (c) switching function of phase B; (d) switching function of phase C; (e) ideal inverter input current $i_{inv}$ with $I_{avg}$ showing in the same graph |   |

| Figure 3.3 Six sectors for voltage references of phase A, B and C                                                                                    | 32     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

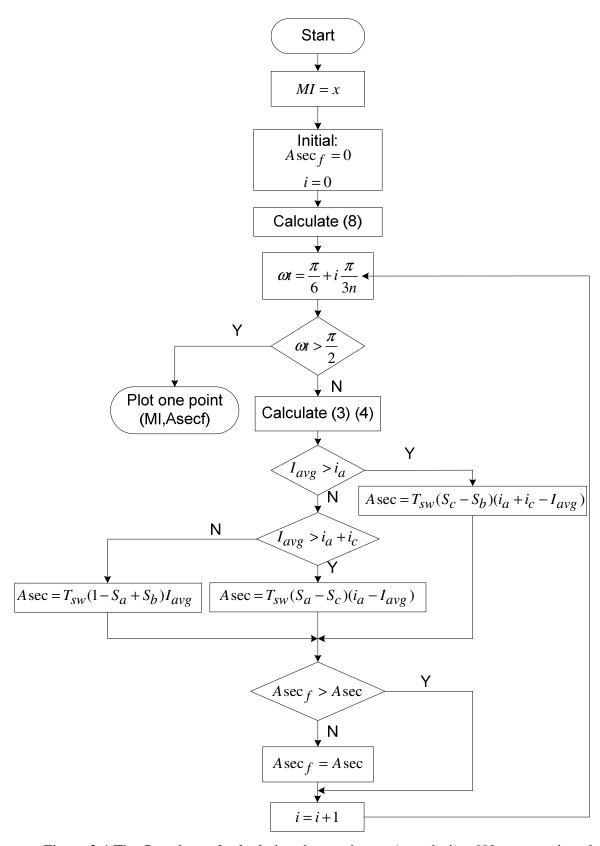

| Figure 3.4 The flowchart of calculating the maximum Asec during 60° at a certain value of and pf                                                     |        |

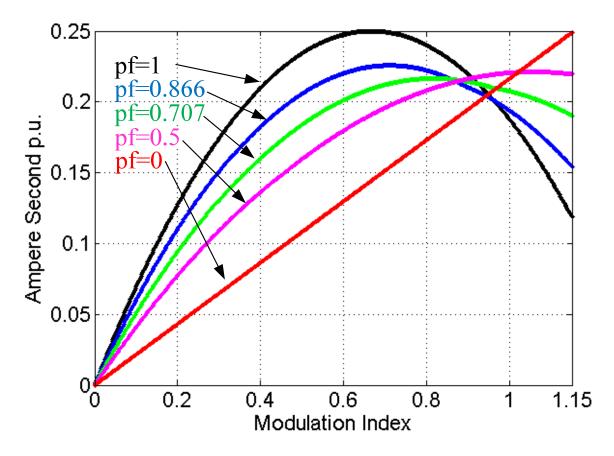

| Figure 3.5 The relationship between Modulation Index $(M)$ and Ampere Second $(A \cdot sec)$                                                         | 38     |

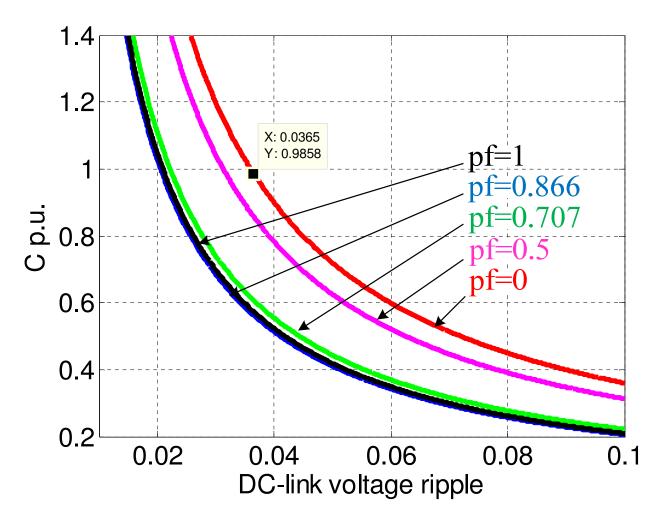

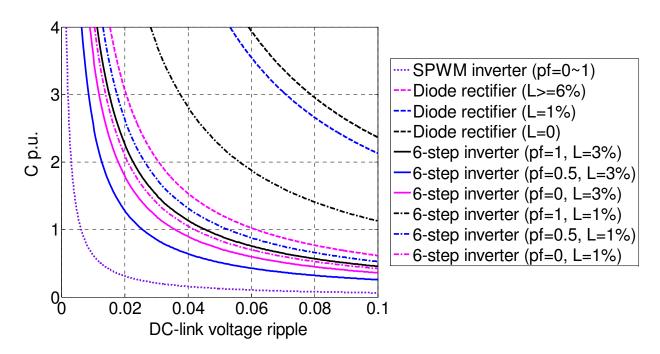

| Figure 3.6 The relationship between per unit value of desired capacitance ( $C_{p.u.}$ ) and DC voltage ripple ( $\varepsilon$ )                     |        |

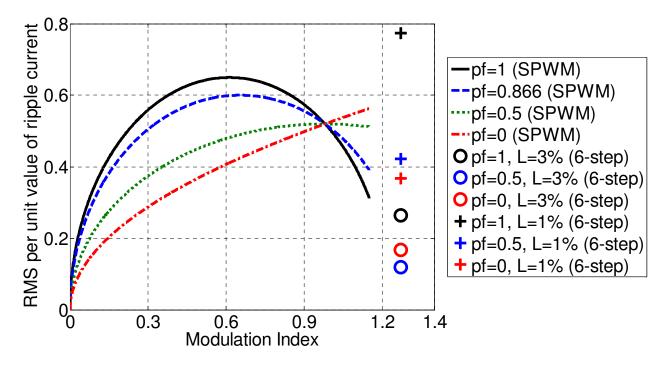

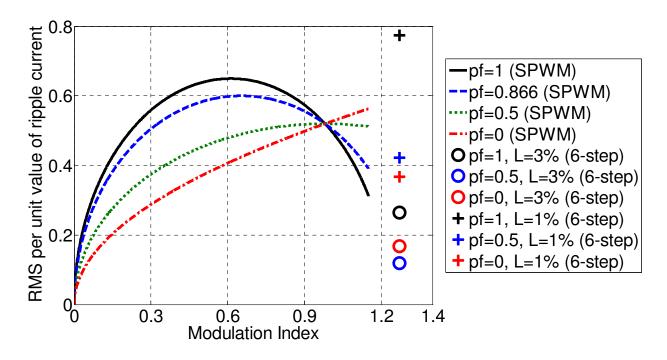

| Figure 3.7 The relationship between the p.u. value of $I_{rms}$ versus MI with different power factors for SPWM and 6-step operations                |        |

| Figure 4.1 Simplified diode rectifier circuit with no line inductance or small line inductan                                                         | ıce 46 |

| Figure 4.2 Simplified diode rectifier circuit with large line inductance                                                                             | 46     |

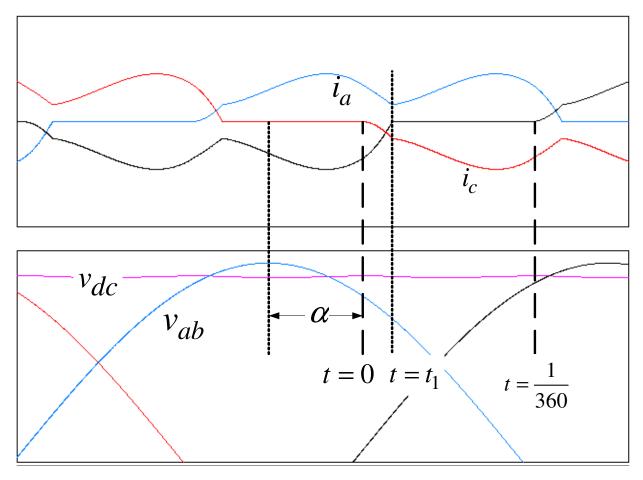

| Figure 4.3 Critical inductance calculation of the diode rectifier (α definition) and Asec calculation of the diode rectifier with a small inductance | 47     |

| Figure 4.4 Asec calculation of the diode rectifier without line inductance                                                                           | 50     |

| Figure 4.5 Asec calculation of the diode rectifier with a large inductance                                                                           | 55     |

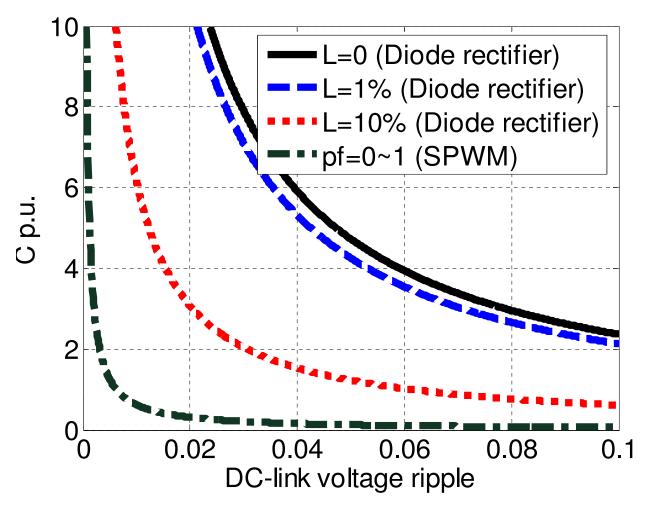

| Figure 4.6 Cp.u. versus ε for rectifier operation compared with SPWM operation                                                                       | 56     |

| Figure 5.1 The simplified equivalent circuit of the inverter under six-step operation                                                                | 58     |

| Figure 5.2 Cp.u. versus ΔV for 6-step                                                                                                                | 61     |

| Figure 5.3 The aggregate of all figures above: Cp.u. versus $\Delta V$ for all operations                                                            | 62     |

| Figure 5.4. Alpms versus MI for SPWM and 6-step operation                                                                                            | 62     |

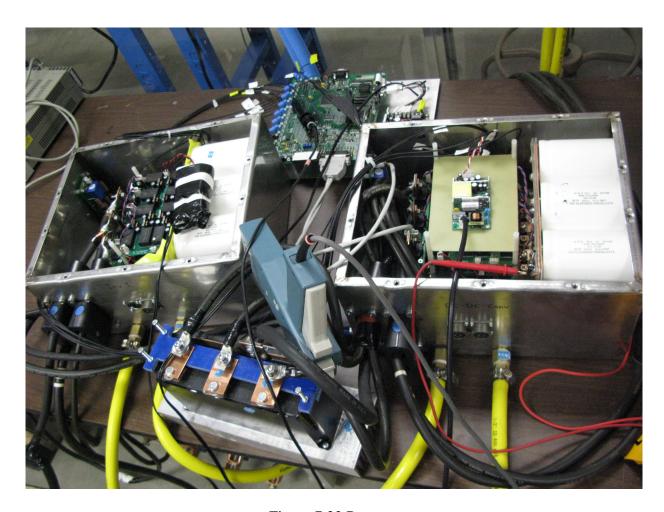

| Figure 6.1 | Inverter module assembly photos (including DC link capacitors, IGBT module, Gate Drive board and Gate drive power supply on top)                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

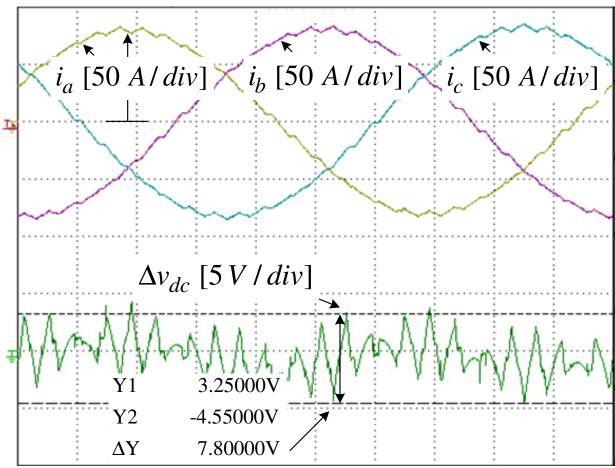

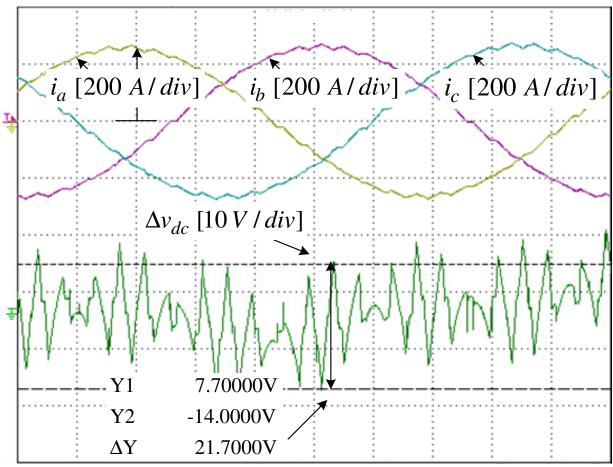

| Figure 6.2 | The experimental waveforms of three phase currents and DC link voltage ripple with DC link voltage at 200 V                                                                                                                                                                                                 |

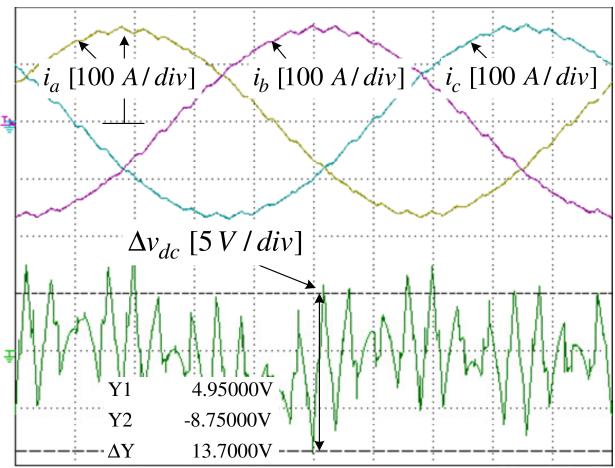

| Figure 6.3 | The experimental waveforms of three phase currents and DC link voltage ripple with DC link voltage at 400 V                                                                                                                                                                                                 |

| Figure 6.4 | The experimental waveforms of three phase currents and DC link voltage ripple with DC link voltage at 650 V                                                                                                                                                                                                 |

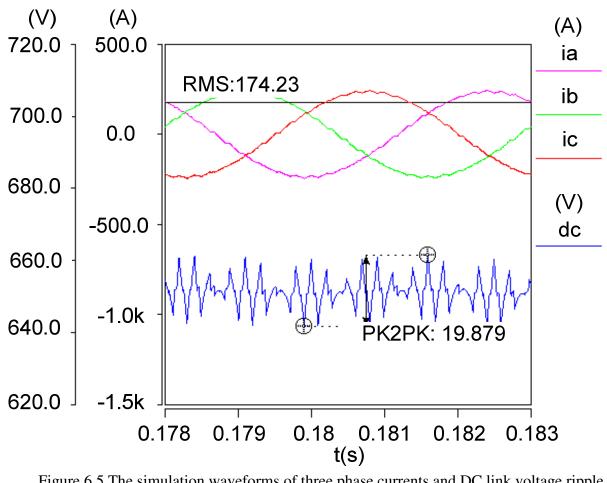

| Figure 6.5 | The simulation waveforms of three phase currents and DC link voltage ripple with DC link voltage at 650 V                                                                                                                                                                                                   |

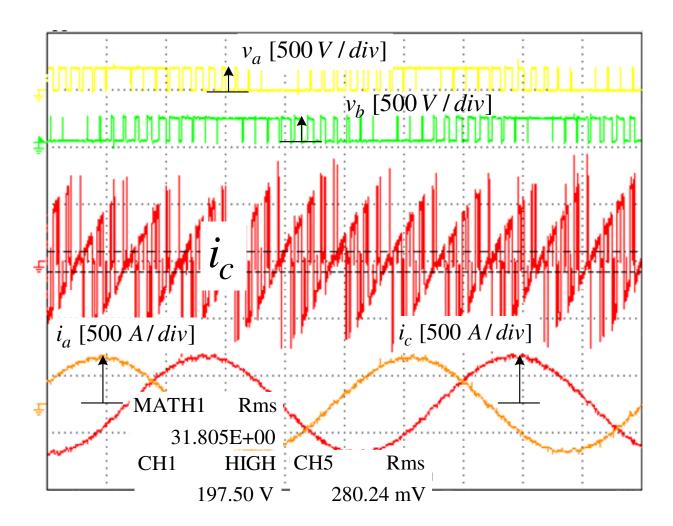

| Figure 6.6 | The experimental waveforms of the capacitor current with DC link voltage at 200 V, pf=0 and MI=0.9                                                                                                                                                                                                          |

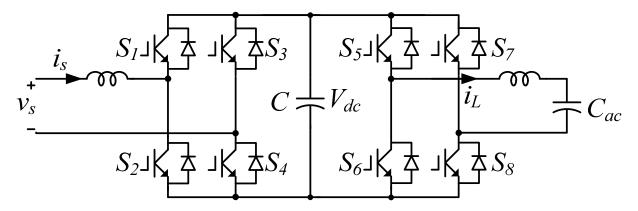

| Figure 7.1 | The schematic of the bidirectional DC-DC converter and the inverter                                                                                                                                                                                                                                         |

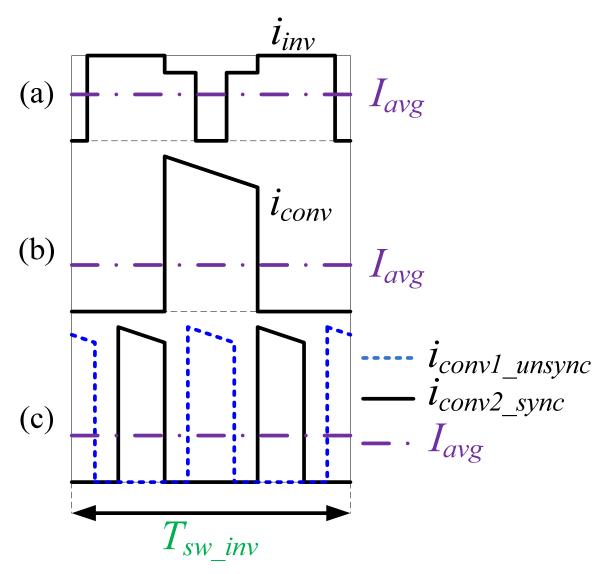

| Figure 7.2 | (a) One sample switching period of the inverter input current with average current drawn in the same figure; (b) The converter output current ( $f_{conv} = f_{inv}$ ); (c) The converter output currents for unsynchronized case and synchronized case ( $f_{conv} = 2 f_{inv}$ ).                         |

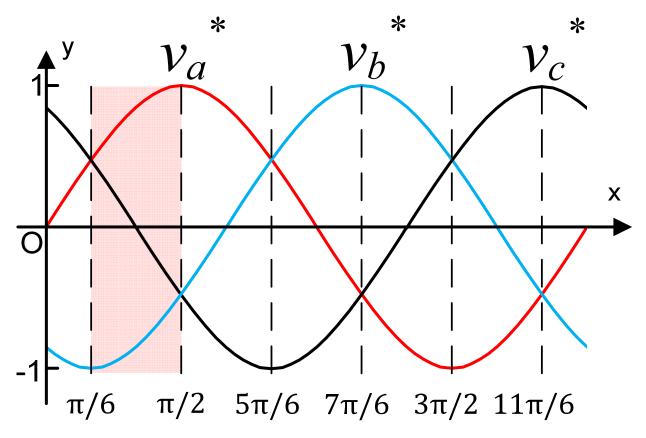

| Figure 7.3 | Three sinusoidal references $v_a^*$ , $v_b^*$ , and $v_c^*$ of the SPWM inverter with one of the six sectors shown in pink shaded block, which will be discussed in this paper 80                                                                                                                           |

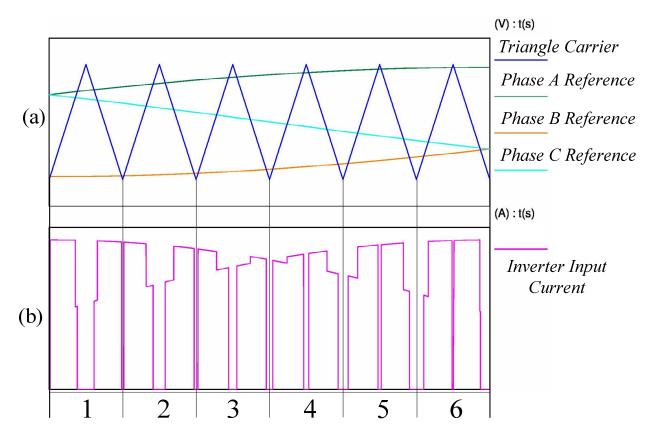

| Figure 7.4 | (a) Common sinusoidal PWM method for the inverter; (b) Simulation waveform of the inverter input current $i_{inv}$                                                                                                                                                                                          |

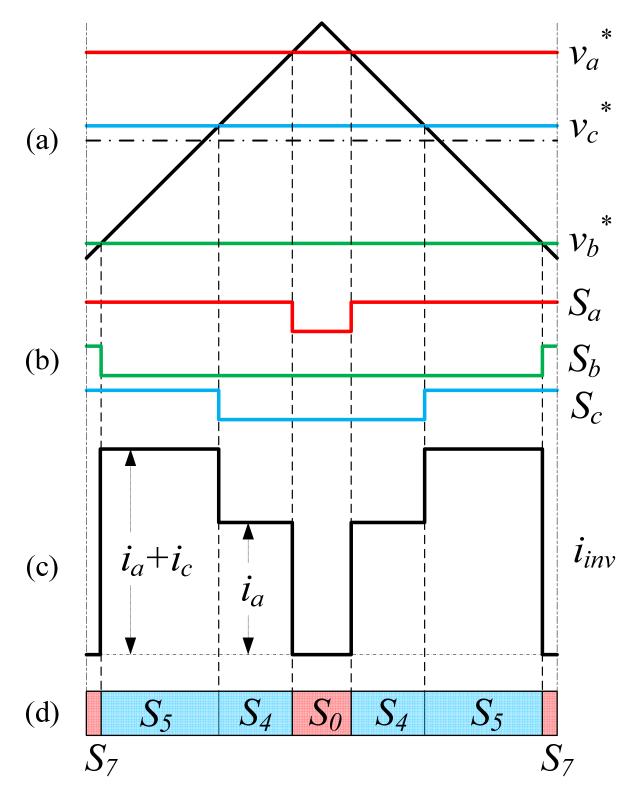

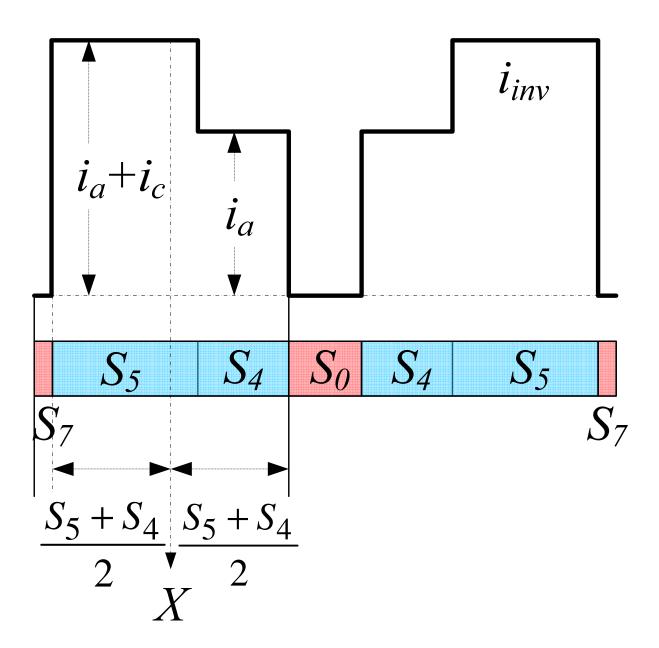

| Figure 7.5 | Detailed waveforms of SPWM in one switching period. (a) Sinusoidal reference and triangle carrier waveforms; (b) Switching functions $S_a$ , $S_b$ and $S_c$ of phase A, B and C; (c) Ideal inverter input current $i_{inv}$ ; (d) Non-zero (active state) and zero (zero state) current portions in blocks |

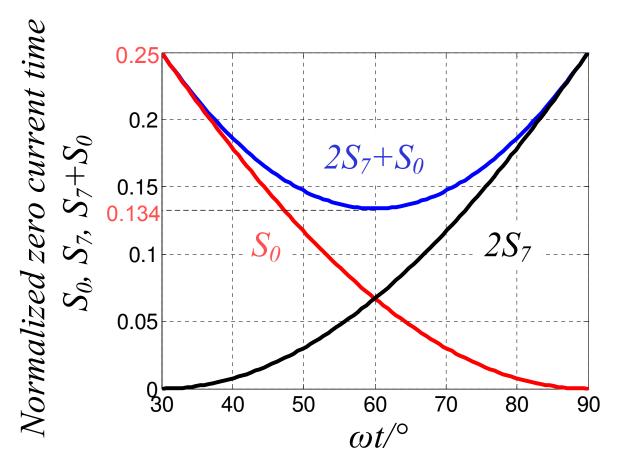

| Figure 7.6 The trend of the $S_0$ , $2S_7$ , and $S_0 + 2S_7$ v.s. $\omega t$                                                                                                                                                                                                                                                                             | . 84 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 7.7 Sine carrier modulation method                                                                                                                                                                                                                                                                                                                 | 86   |

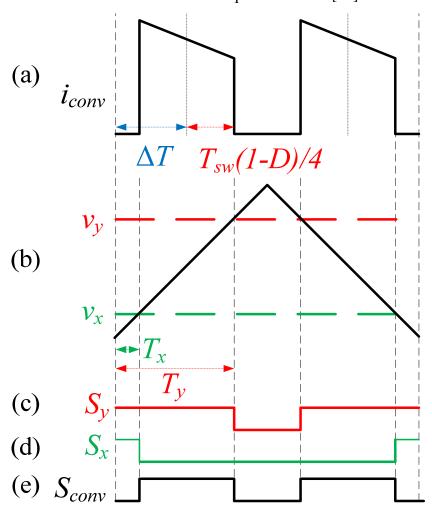

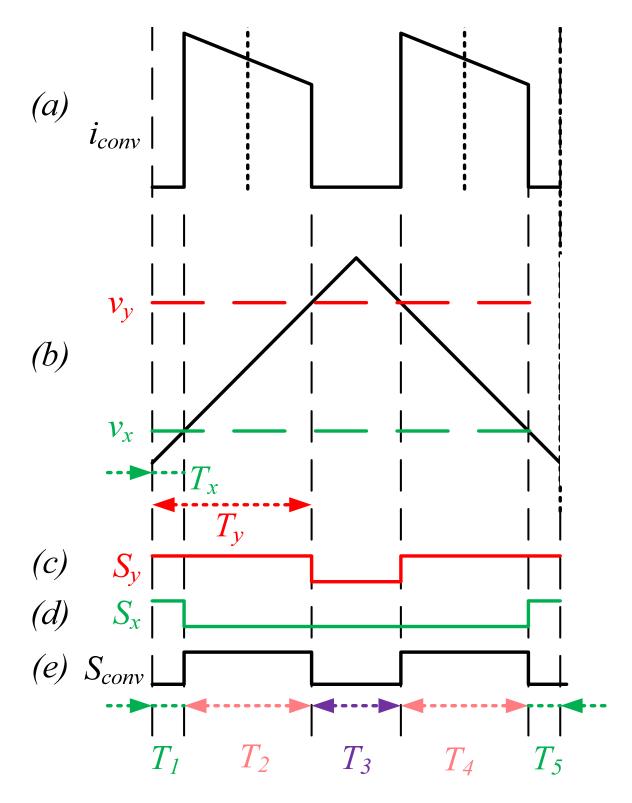

| Figure 7.8 (a) The desired converter output current of the dc-dc converter; (b) Two references compared with the triangle carrier for the dc-dc converter; (c) Generated switching function of $v_y$ ; (d) Generated switching function of $v_x$ ; (e) Generate $S_{conv}$ using $S_x \oplus S_y$                                                         |      |

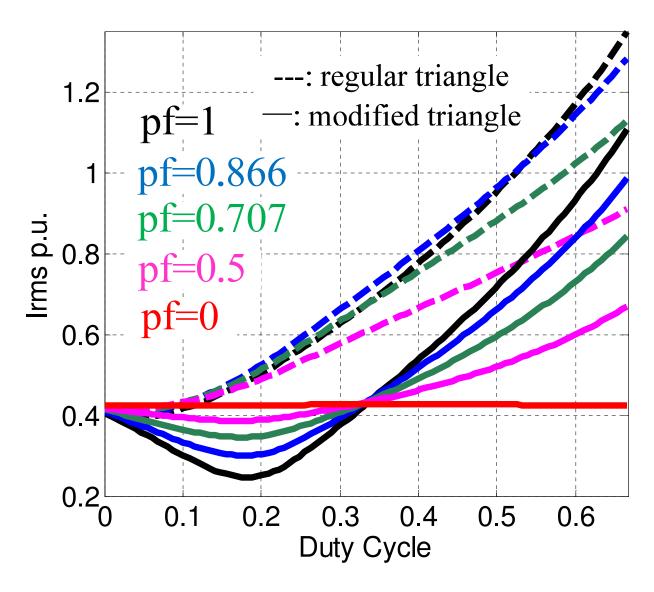

| Figure 7.9 The comparison of $I_{RMS}$ between the regular PWM strategy and modified linear carrier modulation method                                                                                                                                                                                                                                     | 89   |

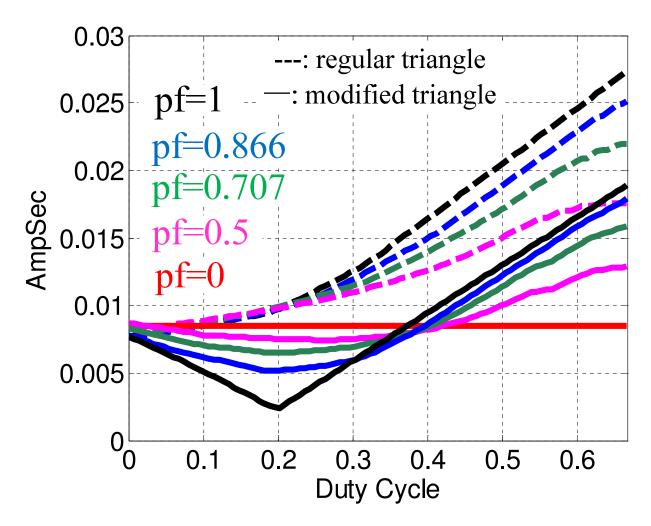

| Figure 7.10 The comparison of <i>A·sec</i> between the regular PWM strategy and modified linear carrier modulation method                                                                                                                                                                                                                                 | 90   |

| Figure 7.11 (a) The desired dc-dc converter output; (b) The realization approach of the carrier modulation method: two references, instead of only one, compared with the tradition triangle carrier; (c) Generated switching function of $v_y$ from (b); (d) Generated switching function of $v_x$ from (b); (e) Generate $S_{conv}$ by $S_x \oplus S_y$ | onal |

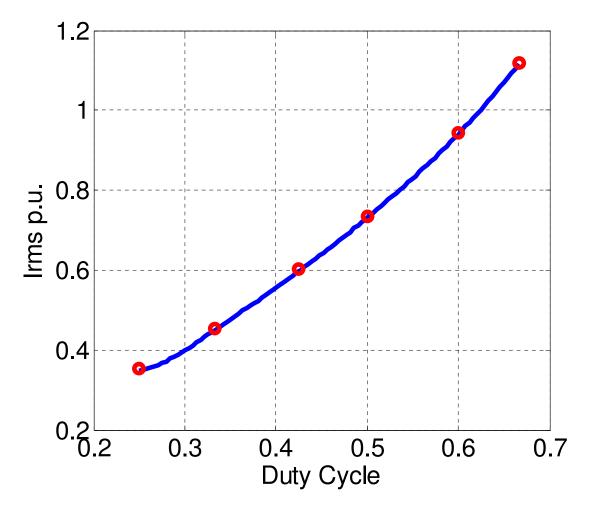

| Figure 7.12 Calculation result and simulation result of the capacitor current ripple per unit val v.s. duty cycle under test condition                                                                                                                                                                                                                    |      |

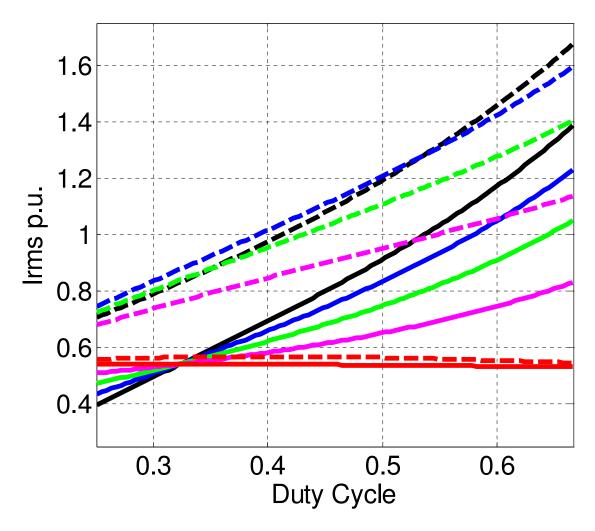

| Figure 7.13 The comparison of the capacitor current ripple per unit value between the regular PWM strategy (dash line) and modified carrier modulation method (solid line)                                                                                                                                                                                |      |

| Figure 7.14 The experimental result of the rms ripple current is 15.651 A at 300 V dc link voltage (Analyzed from the saved data by WVF Viewer from Yokogawa)                                                                                                                                                                                             | 102  |

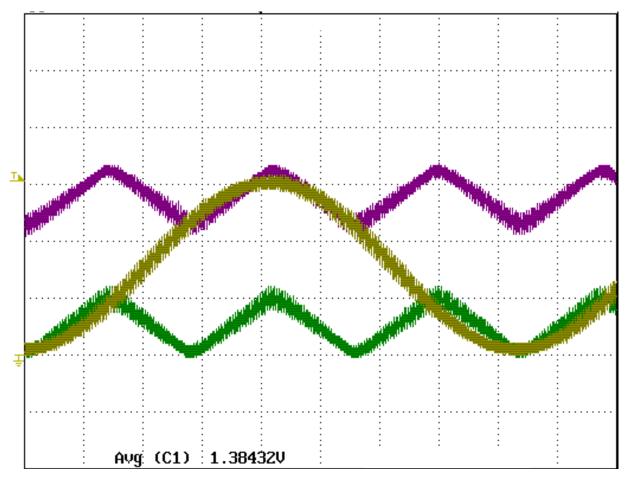

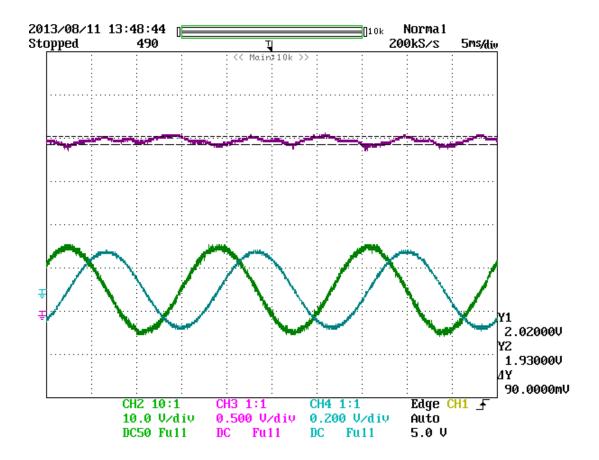

| Figure 7.15 Synchronized the inverter phase A reference signal (yellow) with the converter $V_y$ and $V_y$ low frequency triangle reference signal ( $V_x$ is green and $V_y$ is Purple)                                                                                                                                                                  | ••   |

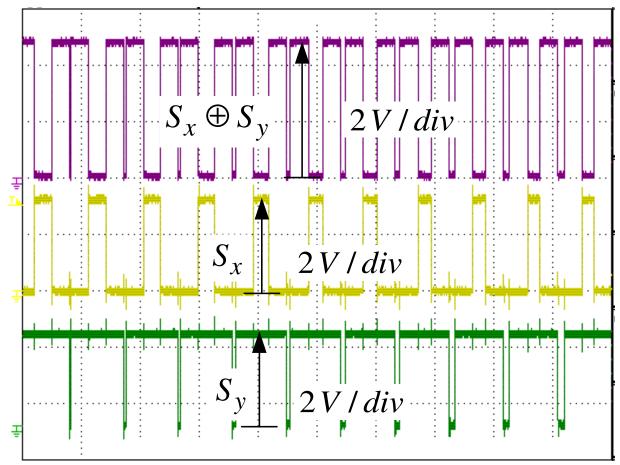

| Figure 7.16 The experimental result of the proposed carrier modulation signal for dc-dc boost converter                                                                                                                                                                                                                                                   | 104  |

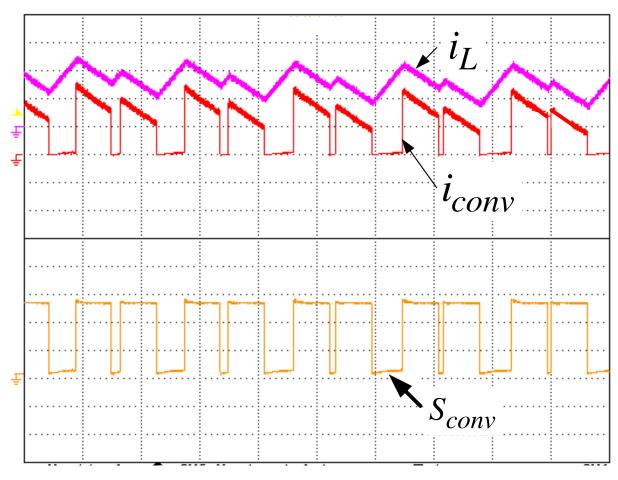

| Figure 7.1 | 17 The experimental results of the inductor current, the converter output current and switching signal of the dc-dc boost converter                                                                                 |     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

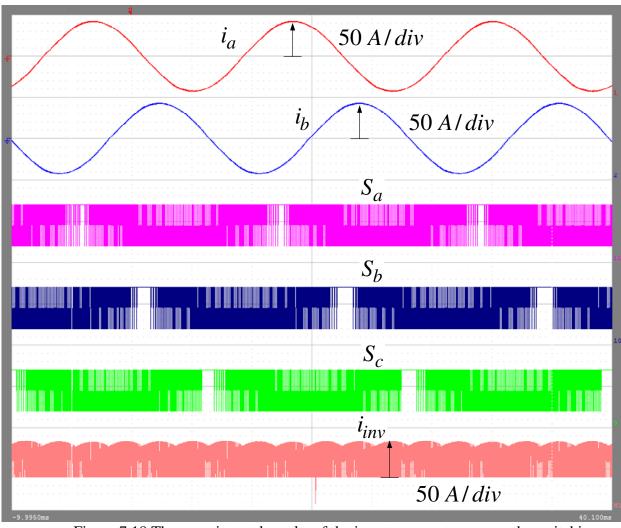

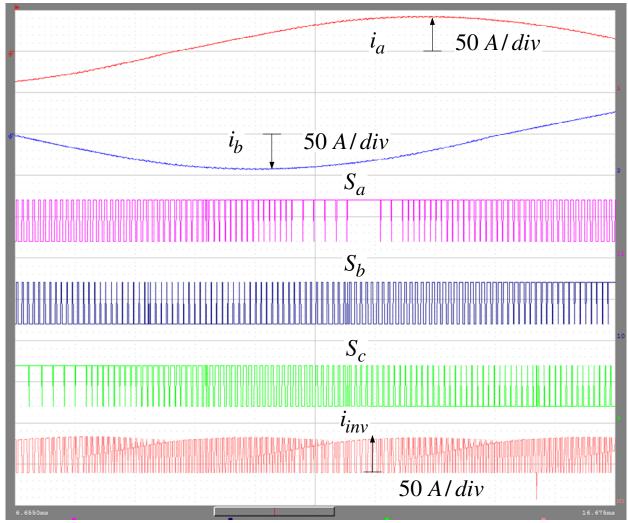

| Figure 7.1 | 18 The experimental results of the inverter output currents, the switching functions, a the input current of the SPWM inverter (Redraw the waveforms from the saved data by WVF Viewer from Yokogawa)               | ì   |

| Figure 7.1 | 19 Zoom in view of Figure 7.18                                                                                                                                                                                      | 107 |

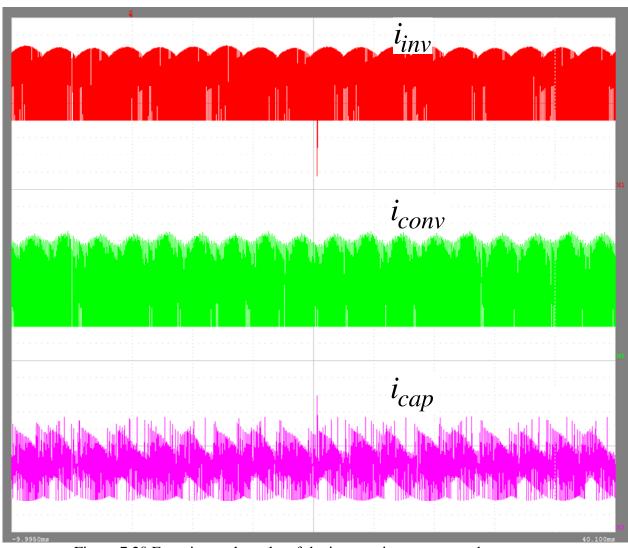

| Figure 7.2 | 20 Experimental results of the inverter input current, the converter output current, and the DC link capacitor current (Redraw the waveforms from the saved data by WVF Viewer from Yokogawa)                       |     |

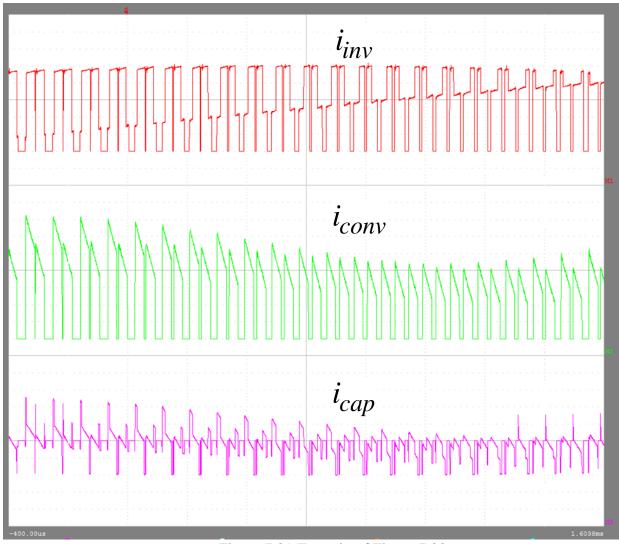

| Figure 7.2 | 21 Zoom in of Figure 7.20.                                                                                                                                                                                          | 109 |

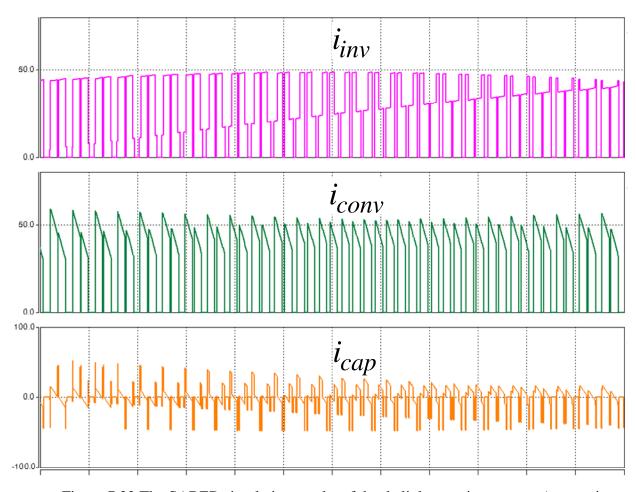

| Figure 7.2 | 22 The SABER simulation results of the dc link capacitor current (comparison for Figure 7.21)                                                                                                                       | 110 |

| Figure 7.2 | 23 Prototype setup                                                                                                                                                                                                  | 111 |

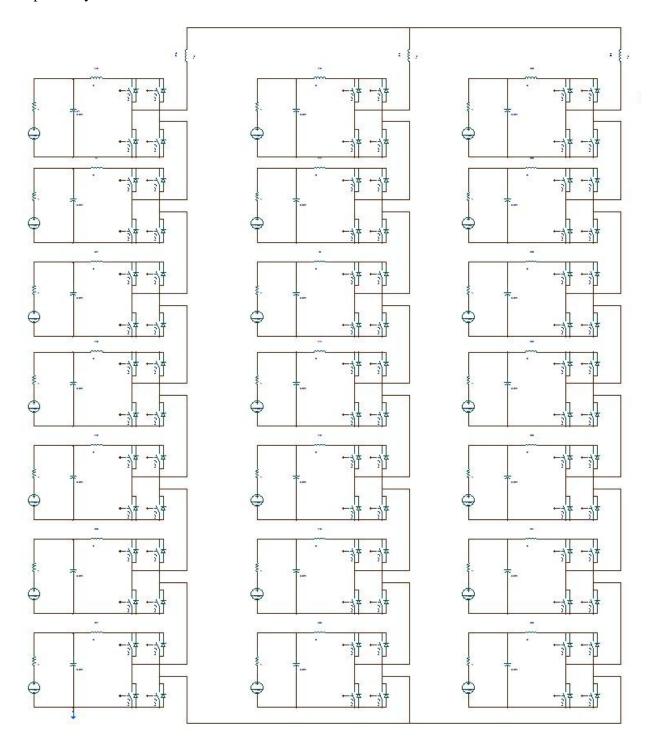

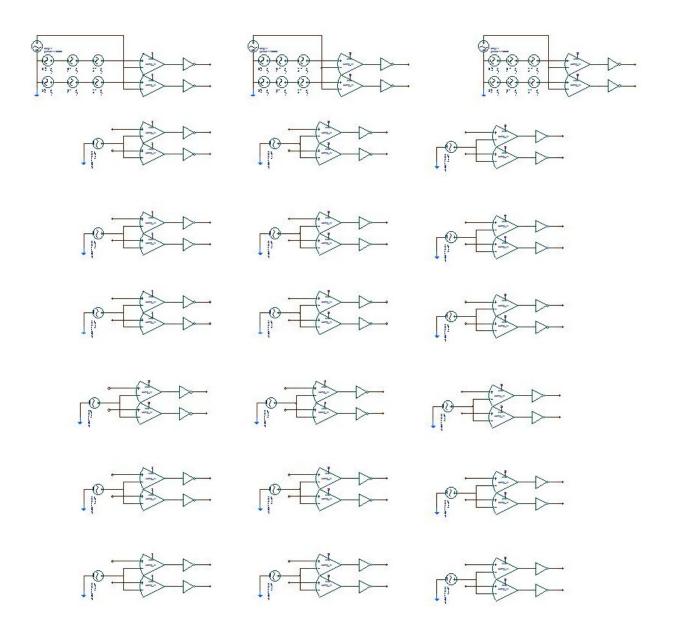

| Figure 8.1 | The system schematic of the 2.1 MVA three-phase cascaded H-bridge multilevel inverter with separate photovoltaic sources.                                                                                           | 114 |

| Figure 8.2 | 2 The schematic of one H-bridge module with notations                                                                                                                                                               | 115 |

| Figure 8.3 | The maximum magnitude of the 3rd harmonic injection that can be selected under a certain fundamental modulation index                                                                                               |     |

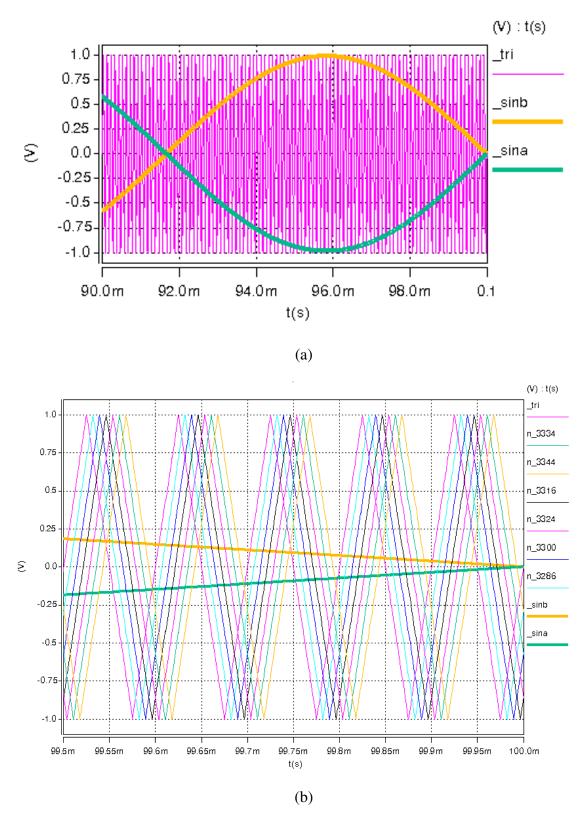

| Figure 8.4 | The phase-shifted carrier-based PWM method: (a) two fundamental references with triangle carrier; (b) zoom-in view of (a), showing the seven phase-shifted triangle carrier for the seven modules in one phase leg. |     |

| Figure 8.5 | 5 SABER Simulation – circuit part                                                                                                                                                                                   | 122 |

| Figure 8.6 | SABER Simulation – PWM generating part                                                                                                                                                                              | 123 |

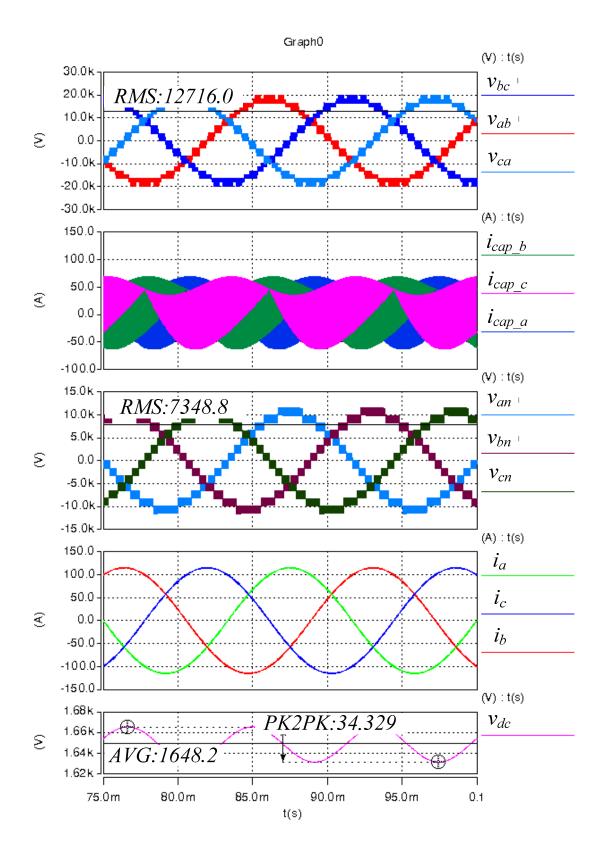

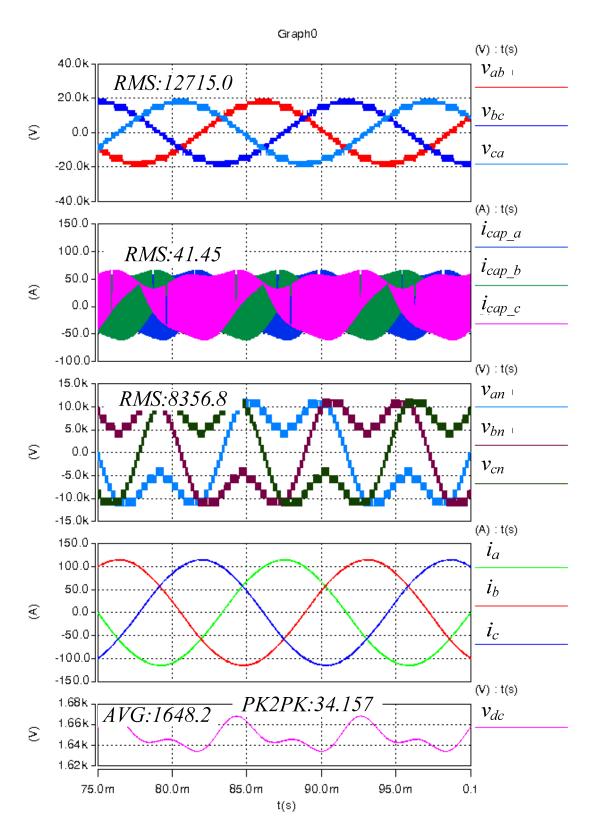

| Figure 8.7 Simulation results of the traditional pulsewidth modulation method without 3rd harmonic injection: M0=0.9, f0=60 Hz, Cdc=3.8 mF                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

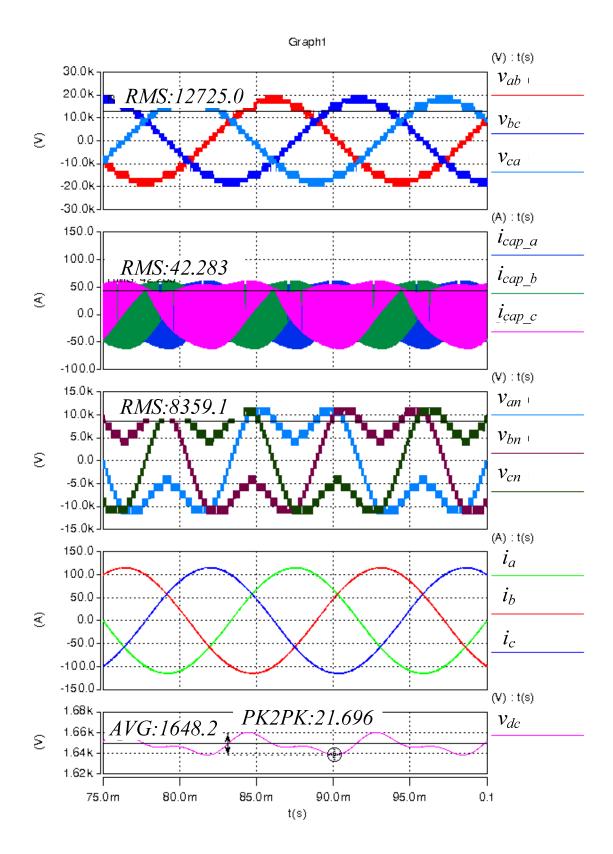

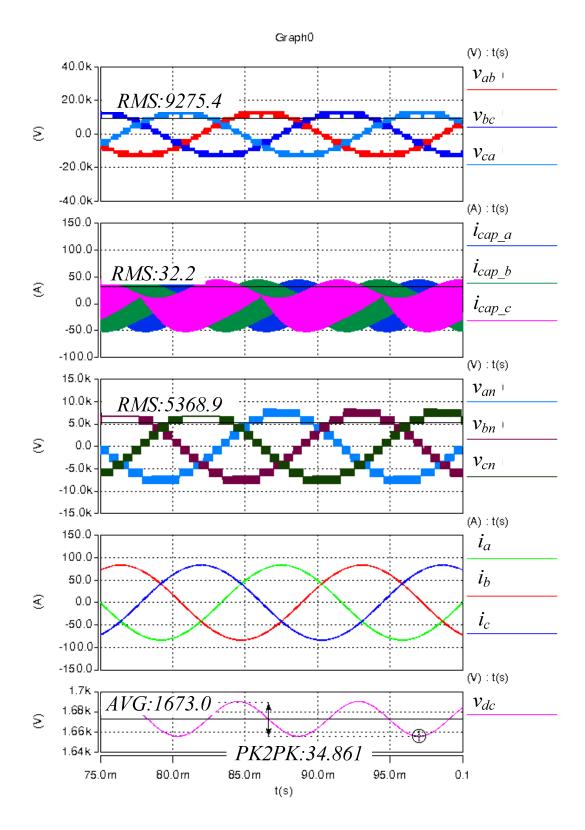

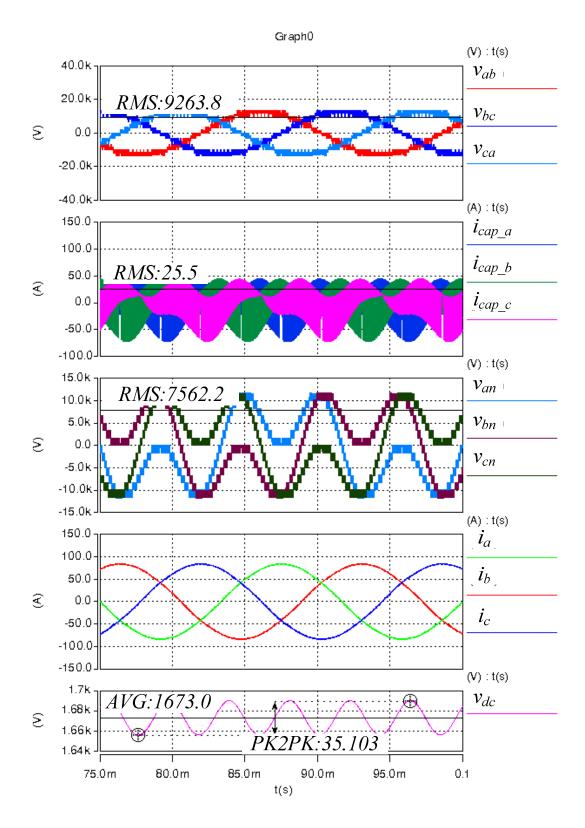

| Figure 8.8 Simulation results of the proposed 3rd harmonic injection pulsewidth modulation method: M0=0.9, f0=60 Hz, M3=0.4865, f3=180 Hz, Cdc=3.8 mF     |

| Figure 8.9 Simulation results of the proposed 3rd harmonic injection pulsewidth modulation method: M0=0.9, f0=60 Hz, M3=0.4865, f3=180 Hz, Cdc=2.2 mF     |

| Figure 8.10 Simulation results of the traditional pulsewidth modulation method without 3rd harmonic injection: M0=0.6459, f0=60 Hz, Cdc=1.6 mF            |

| Figure 8.11 Simulation results of the proposed 3rd harmonic injection pulsewidth modulation method: M0=0.6459, f0=60 Hz, M3=0.6459, f3=180 Hz, Cdc=800 uF |

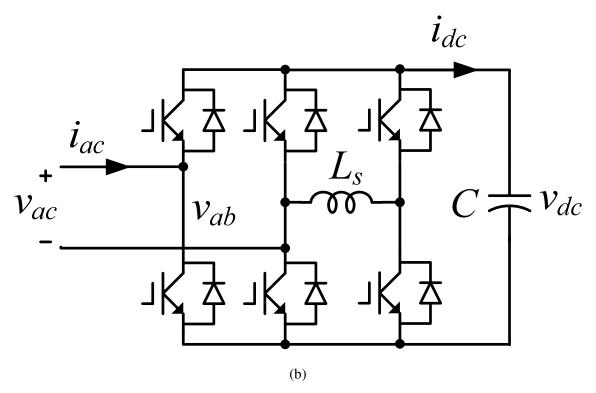

| Figure 9.1 An ideal variable capacitor                                                                                                                    |

| Figure 9.2 A variable capacitor implemented by an H-bridge inverter                                                                                       |

| Figure 9.3 The proposed solid state variable inductor-capacitor:                                                                                          |

| Figure 9.4 Traditional H-bridge inverter                                                                                                                  |

| Figure 9.5 Traditional H-bridge topology with a bidirectional buck/boost converter 142                                                                    |

| Figure 9.6 Traditional H-bridge topology with another bidirectional buck-boost converter 145                                                              |

| Figure 9.7 Traditional H-bridge topology with another H-bridge inverter on the ac side 147                                                                |

| Figure 9.8 Traditional H-bridge topology with another H-bridge inverter in series on the dc side                                                          |

| Figure 9.9 Traditional H-bridge topology with another H-bridge inverter in parallel on the dc side                                                        |

| Figure 9.10 Traditional H-bridge topology with an active filter: (a) use a capacitor as the auxiliary energy storage; (b) use an inductor as the auxiliary energy storage | 151 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

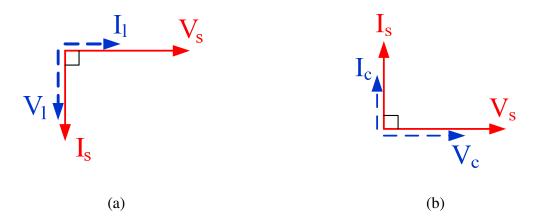

| Figure 9.11 Phasor diagram of (a) SSVL and (b) SSVC.                                                                                                                      | 155 |

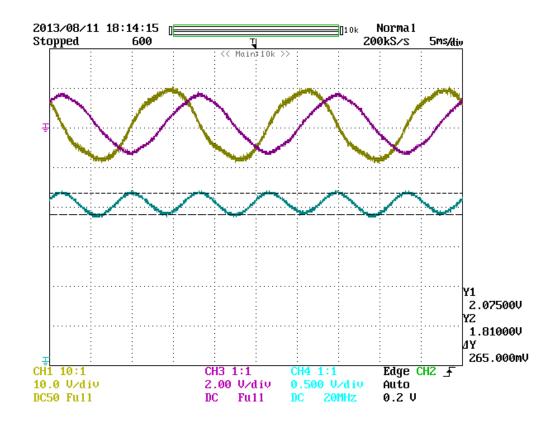

| Figure 9.12 Traditional H-bridge inverter with 820 uF dc capacitor                                                                                                        | 156 |

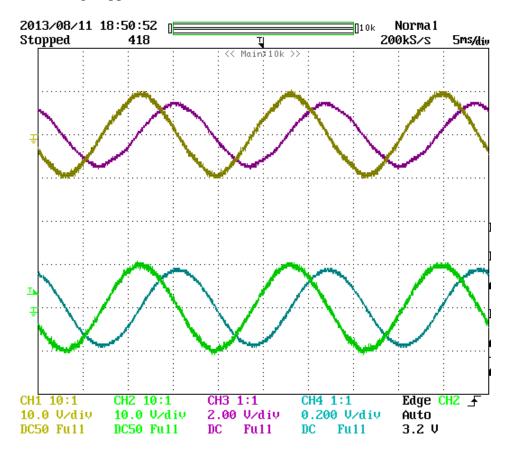

| Figure 9.13 The proposed SSVC with 150 uF dc capacitor and 300 uF ac auxiliary capacitor.                                                                                 | 157 |

| Figure 9.14 The proposed SSVC with 150 uF dc capacitor and 300 uF ac auxiliary capacitor.                                                                                 | 158 |

## **CHAPTER 1 DC Link Capacitors**

DC link capacitors are used in intermediate circuit applications in power electronics e.g. power conversion technique, where different kinds of converters couples to one dc voltage level. Therefore, this kind of capacitors usually has to sustain high dc voltage which exists permanently and which is always accompanied by high frequency ripple voltages. The capacitors that can satisfy these requirements usually occupy a large space in the inverter, and they are also heavy and expensive. However, they commonly exist and play a very important role in most conventional topologies of power electronics, such as the three-phase voltage source inverter (VSI) and the single-phase VSI (or H-bridge VSI). These topologies are so matured in nowadays industry, and traditionally they cannot live without the dc link capacitors.

Therefore, minimization of the dc capacitor is an essential step towards developing and manufacturing compact low-cost inverter systems for high temperature operation, long life and high reliability.

Traditionally, the dc capacitance has been determined according to empirical equations and computer simulations, which provides little insights into how to minimize the dc capacitor. In order to achieve an optimum minimization of the dc capacitor, an accurate theory to calculate the dc capacitor voltage ripple and current ripples must be developed first, then pulse-width modulation (PWM) and control techniques or topological improvements can be further developed to minimize both dc voltage and current ripples.

This dissertation is mainly divided into two parts. First half is minimizing the capacitor ripple and requirements for three-phase VSI; while second half is for single-phase (H-bridge) VSI.

## 1.1 Types of DC Link Capacitors

Before going into details about how to minimize the dc link capacitors, let's take a look at those most common types of dc link capacitors.

In general, there are two types of capacitors are commonly used in the dc link. One is the electrolytic capacitor, and the other one is the film capacitor.

#### 1.1.1 Electrolytic capacitor

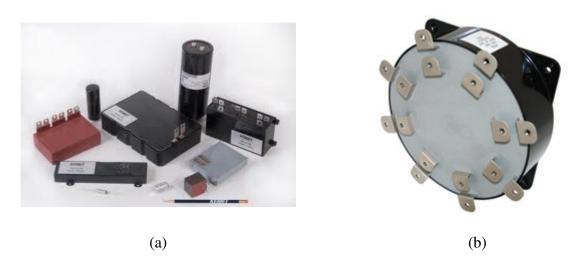

Electrolytic capacitor for dc link usually looks similar to what are shown in Figure 1.1. It uses an electrolyte as one of its plates to achieve a larger capacitance per unit volume than other types. Due to this large capacitance, it makes it a very good candidate for low frequency filter and large energy storage. [1]

However, it also gets a lot of problems. It tends to have larger leakage current than other dry types of capacitors. In addition, the limitation on the operating temperatures keeps it away from high temperature applications. With the large parasitic resistance and inductance, it further limits its ripple current handle capability. Therefore, in some applications with high temperature and ripple currents, the electrolytic capacitors tend to have shorter life and less reliability.

(a) (b)

Figure 1.1 Commercial electrolytic capacitors

Pictures are obtained from the below websites:

- (a) <a href="http://theelectrostore.com/shopsite\_sc/store/html/high-voltage-electrolytic-capacitors-400v-3900uf.html">http://theelectrostore.com/shopsite\_sc/store/html/high-voltage-electrolytic-capacitors-400v-3900uf.html</a>

- (b) <a href="http://www.royalrrs.com/products/Capacitors/">http://www.royalrrs.com/products/Capacitors/</a>

#### 1.1.2 Film capacitor

Film capacitors are made with an insulating plastic film as the dielectric, and combined with metallized aluminum or zinc as the electrodes. They are usually wound into cylindrical shape, with terminals attached on the sides, and then encapsulated. Some of them are look similar to what shown in Figure 1.2. [2, 3]

They are known of high current ripple handle ability, high operating temperature, very small equivalent series resistance and inductance. All these features make it a very good candidate for high switching frequency inverter/converters. However, the capacitance value tends to be smaller than the electrolytic capacitors. Additionally, the energy density is not as high as the electrolytic ones either.

Figure 1.2 Commercial film capacitors

Pictures are obtained from the below websites:

- (a) <a href="https://encrypted-tbn3.gstatic.com/images?q=tbn:ANd9GcQs8-">https://encrypted-tbn3.gstatic.com/images?q=tbn:ANd9GcQs8-</a>

\_8lP1VhCh90QQCjguK1HM-SqDLoc87\_Hs\_OZYvo4ZoWwaX

- (b) http://www.sbelectronics.com/wp-content/uploads/2011/04/700D349\_300\_200.jpg

## 1.2 Comparisons

It is more straightforward to compare these two kinds of capacitors in a table shown in Table 1.1.

In conclusion, as the switching frequency goes higher, operating temperature goes higher, and the requirement of reliability goes up, it is more preferred to choose film capacitor rather than aluminum electrolytic capacitor.

Table 1.1 DC Link Capacitor Comparison between Film and Electrolytic [4]

| Parameter             | Film                 | Aluminum Electrolytic |

|-----------------------|----------------------|-----------------------|

| Capacitance           | Low                  | High                  |

| ESR                   | Low                  | High                  |

| Max operating temp    | 105 °C               | 85 °C                 |

| Max voltage           | Larger than 1000 Vdc | 600 Vdc               |

| Ripple Current        | High                 | Low                   |

| Life                  | Long                 | Short                 |

| <b>Energy Density</b> | Low                  | High                  |

| Failure mode          | Fail open            | rupture               |

| Construction          | Dry                  | Liquid electrolyte    |

| Polarity              | Non polar            | Have polarity         |

# 1.3 Applications Using DC Link Capacitors and Outline of Dissertation

As mentioned previously, the dc link capacitors are needed in quite a lot of topologies, including those extremely matured ones, for example, the three-phase inverter and the single-phase inverter. These two topologies are going to be the focus of this dissertation.

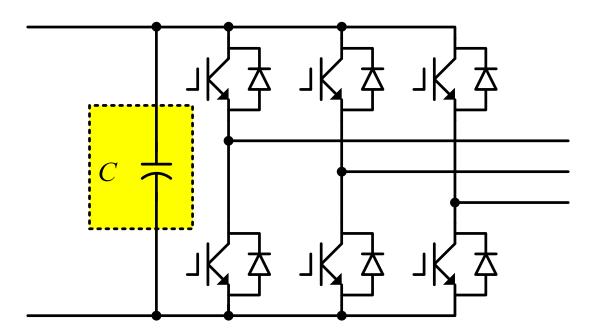

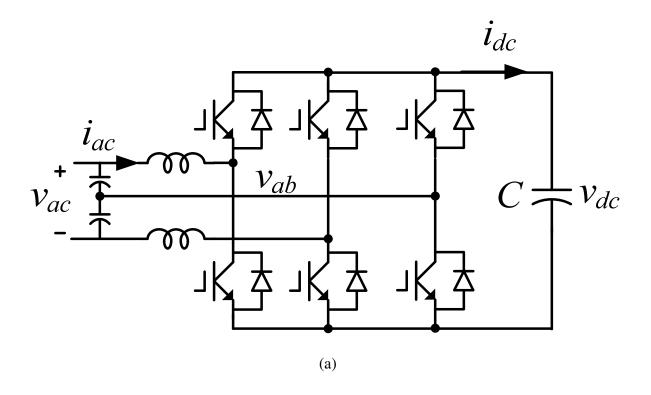

#### 1.3.1 Three-Phase Inverters

Figure 1.3 shows a typical three-phase inverter with a dc link capacitor shaded in the dashed box. This three-phase inverter has been widely used in the industry, for example, the hybrid electric vehicles (HEV), electric vehicles (EV) and so on.

In the first half of this dissertation, minimizing the dc link capacitance is focused on this three-phase inverter in HEV application, which is quite a hot topic in recent years.

Chapter 2 gives a general introduction and motivation of the first a few chapters (Chapter 3 to Chapter 7) on HEV applications, and introduces the limited work done in the past, which indicates more room for this dissertation to contribute.

Chapter 3 to Chapter 5 introduces the theoretical calculation of dc capacitance requirement and dc current ripple requirement for 3-phase inverter under SPWM, diode rectifier and 6-step operation method. This indicates the theoretical minimum value of dc capacitance. Chapter 6 shows the simulation, prototype and experimental results of a HEV system.

Chapter 7 proposes a new carrier modulation method to synchronize the dc-dc converter and SPWM inverter in the HEV systems to further minimize the dc link capacitor. It is cross checked with simulation and experimental results.

Figure 1.3 Typical three-phase inverter with dc link capacitor

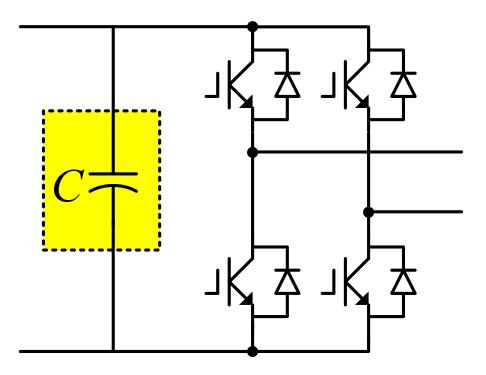

#### 1.3.2 Single-Phase Inverters

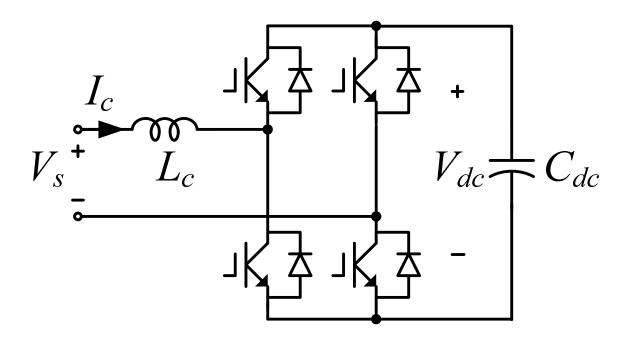

Figure 1.4 shows a typical single-phase (H-bridge) inverter with a dc link capacitor shaded in the dashed box. This single-phase inverter is also widely used in the industry for its matured technology and simple configuration and control.

There are quite a lot of applications. However, in this dissertation, the photovoltaic and the reactive power compensation is the focused application.

Chapter 8 proposes a 3<sup>rd</sup> harmonic injection for the photovoltaic system to reduce the dc link capacitor down to around 50%.

Chapter 9 proposes a new topology by adding an additional phase leg and a passive component to transfer the ripple energy to the auxiliary passive component, so as to reduce the dc link capacitor down to minimum.

And finally Chapter 10 is the contribution and future work.

Figure 1.4 Typical single-phase inverter with dc link capacitor

## **CHAPTER 2** Introduction of HEV

## **Applications and Their DC Capacitors**

## 2.1 The Advantage of HEV in the Automotive Market

Emissions of  $CO_2$  by human activities are currently amounting to about 27 billion tons per year [5]. The considerably high amount of  $CO_2$  emission forces people to make every effort to minimize these emissions from the aspect of the human activities. Many excellent thoughts are considered, compared, analyzed, developed and finally built, tested and realized. One of these outstanding ideas, which protecting our mother earth from global warming and pollutions, is the development of hybrid electric vehicles (HEV), plug-in hybrid electric vehicles, and pure-electric vehicles. There are many worth reading websites and reviewed papers discussing the configurations of each kind and the comparison among them [6-8].

Nowadays, compared to the plug-in HEV and pure-electric vehicle, the HEV is the most popular and commercial type in the current automotive market. Similar to the ordinary vehicles, HEV possesses the power of fast acceleration and longer driving distance without the limitation of charging requirements.

The HEV system utilizes two different and independent energy sources, and hence, achieves a much higher fuel economy than the traditional vehicle with solely operated by the low-efficiency energy source—the internal combustion engine (ICE). Therefore, utilizing the HEV

can reduce the emissions of  $CO_2$  and help clean the cities, at the same time save the limited energy resources for the world due to its higher efficiency (mile per gallon).

However, speaking to individuals, the cost of a HEV is still higher than the gas price that can be saved from it. Therefore, in order to impel more and more people to buy HEVs, the price needs to be further lowered down. That is why engineers have been doing researches on minimizing the cost, weight and size of the motors, generators, power electronics devices, and passive components in HEV systems during the past decades.

The work in this dissertation is mainly focusing on minimizing one of the biggest passive components in the HEV systems—the dc link capacitor, which leads to the ultimate goal of minimizing the cost, weight and size of the whole HEV systems.

## 2.2 Types of HEV Systems

Focus on HEVs, there are many different ways to classify HEV systems, and the general classification is to classify HEVs according to the way in which power is supplied to the drivetrain. Hence, there are three categories: series hybrid electric vehicles (SHEV), parallel hybrid electric vehicles (PHEV), and series-parallel hybrid electric vehicles (SPHEV). Generally speaking, the SHEV is used on heavy duty vehicles (buses, trucks etc.), while the PHEV is usually applied to light duty vehicles (family sedan etc.).

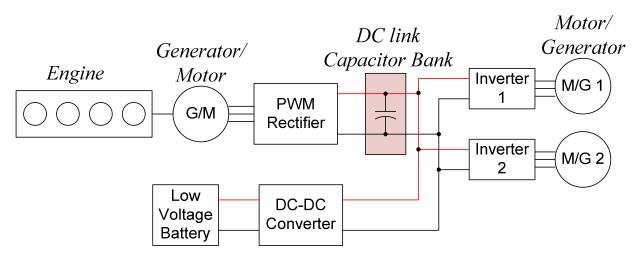

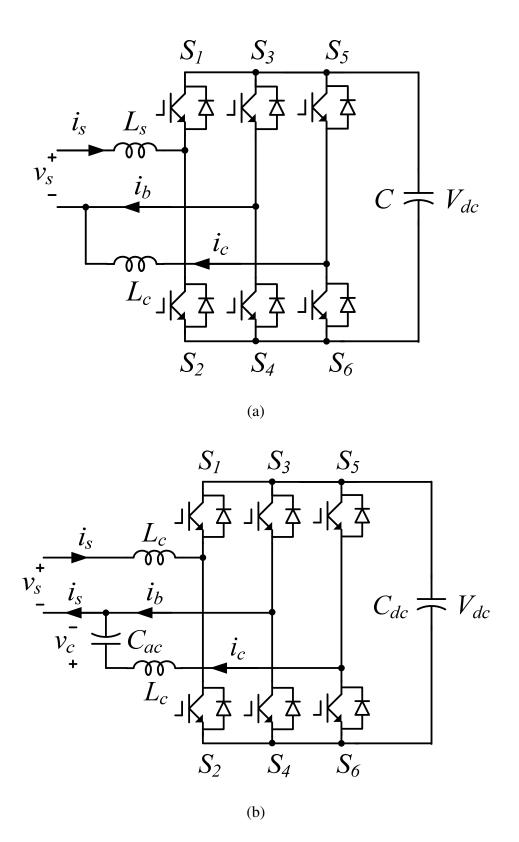

In order to illustrate the power electronics modules that located in the HEV, take the SHEV system as an example. The general power electronics function blocks in the commercial SHEV systems can be demonstrated similarly as Figure 2.1, which consists of an internal combustion engine (ICE), a generator/motor, a bidirectional pulse-width modulation (PWM) rectifier, a dc

link capacitor bank, a bidirectional inverter and a motor/generator. Additionally, instead of a high voltage battery, a low voltage battery with a smaller size is usually preferred and connected to the dc link through a dc-dc boost converter. For the sake of having the PWM rectifier, the inverter, and the dc-dc converter each at the same power rating, the system can have two smaller inverters controlling two traction motors respectively (shown in Figure 2.1) instead of only one inverter, whose power rating is the summation of the PWM rectifier's and the dc-dc converter's.

Figure 2.1 The power electronics function blocks of the series hybrid electric vehicle (SHEV) systems

### 2.3 Power Electronics Challenge in HEV systems

As shown in Figure 2.1, in a SHEV converter/inverter system, the dc link capacitor bank, shown in the shaded block, is usually bulky, heavy and expensive. The reason for this is that, this dc link capacitor bank needs to absorb all the current ripples generated by two inverters, the PWM rectifier, as well as the dc-dc converter. However, traditionally, this dc capacitance has been determined according to empirical equations and computer simulations, which provide little insight into how to minimize the dc link capacitance. Therefore, they are usually much bigger than needed, so that they occupy an unnecessarily large space. It is the biggest component in an

inverter box. As a result, minimization of the dc capacitance is an essential step towards developing and manufacturing compact, light, low-cost HEV converter/inverter systems for high temperature operation, long life and high reliability.

Therefore, in order to achieve an optimum minimization of the dc capacitor, an accurate theory to calculate the dc capacitor voltage and current ripple must be developed first, then PWM and control techniques can be further developed to minimize both dc voltage and current ripples.

## 2.4 Inverter Operation Modes in HEV

#### 2.4.1 Sinusoidal Pulsewidth Modulation Mode

In the HEV converter/inverter systems, when the vehicle is at a relatively low speed, such as accelerating from a stop, battery is often chosen as the power supply, instead of the inefficient ICE. Plus, dc-dc converter is operated as a boost converter, to boost the low battery voltage to relatively high dc link voltage. Afterwards, the three-phase inverter used to drive the traction motor usually use sinusoidal pulse-width modulation (SPWM) mode. The SPWM mode can supply a smoothly increasing ac voltage to cooperate with the increasing speed, in order to ensure the maximum current and maximum torque. That comes from the *V/f* control. In this motoring situation, Figure 2.2 is the equivalent circuit.

Another important situation is when the generator/ICE started. In order to save the trouble of building another lower power rating starter and adding an additional 12-V battery, just utilizing the existed battery and the PWM rectifier instead could be a good choice. This requires the PWM rectifier works as an inverter at this time, which again Figure 2.2 is the equivalent circuit.

How about the regenerative modes? Regenerative mode happens at when the driver pushes

the brake pedal. At this time, the motor acts as a generator. The generated power is transferred through a three-phase PWM inverter (PWM rectifier mode in this case) and a dc-dc converter, and stored this power in the battery. By doing so, instead of wasting the energy to heat up the brakes or bleeding resistors, the energy is stored and can be reused later on. This results in energy saving, and high efficiency. Since the motor/generator is operating as a generator, the three-phase PWM inverter should operate as a PWM rectifier accordingly to convert the power from ac to dc. Although it sounds so different, the PWM rectifier is actually the same as the SPWM inverter. Therefore, in the regenerative mode, as the brake pedal is being pushed and the speed is decreasing, the PWM rectifier is operated by SPWM, which again Figure 2.2 is considered.

And of course, when the energy comes from ICE/generator side to the dc link side, the PWM rectifier is working as a PWM rectifier. Therefore, it is again Figure 2.2.

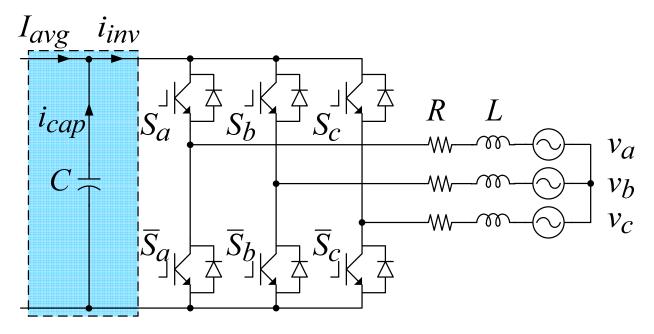

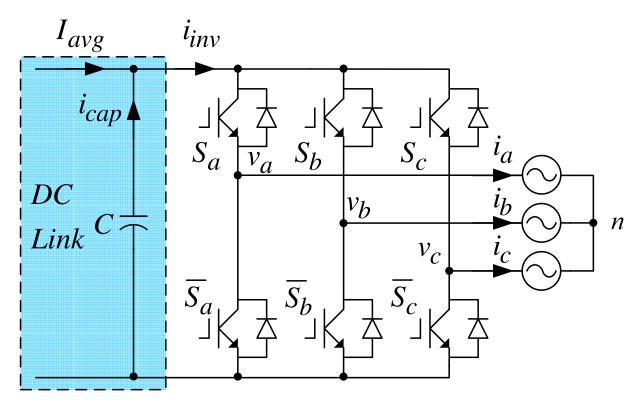

Figure 2.2 The schematic of a three-phase inverter/PWM rectifier using SPWM with three-phase current sources as load

### 2.4.2 Six-Step Mode

After the acceleration, the vehicle reaches at a much higher speed. This requires the inverter to output a higher voltage. In this case, six-step operation is often used, due to its higher dc voltage utilization. This is demonstrated in Figure 2.3. The only difference from the SPWM operation mode is that, for six-step operation, when the vehicle goes to higher speed, the back electromotive force (EMF) can no longer be ignored, that is what happened with those added voltage sources at the load side in Figure 2.3.

Figure 2.3 The simplified equivalent circuit of the inverter under six-step operation

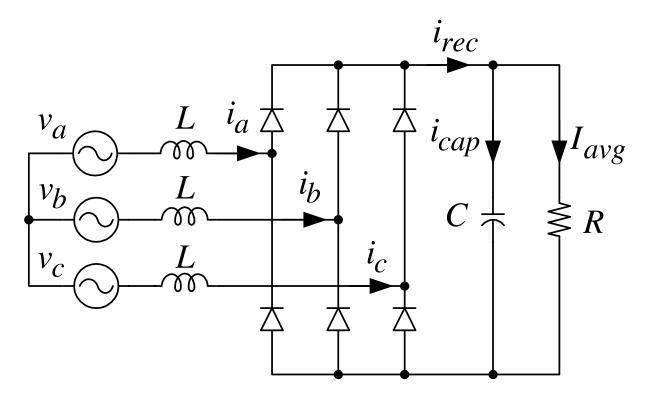

#### 2.4.3 Diode Rectifier Mode

The last mode is diode rectifier mode. For the PWM rectifier, if all the power switches switch off, and only the freewheeling diodes forced on and off the input voltages, the PWM rectifier becomes an uncontrolled diode rectifier, as shown in Figure 2.4.

If considered PHEV, there is no PWM rectifier connecting the generator/motor to the dc link. However, if considered SHEV, there is a PWM rectifier connecting the generator/motor to the dc link, which at most time rectifies the three-phase ac voltages generated by the generator/motor to dc voltage. As you may notice, this PWM rectifier can work as an uncontrolled diode rectifier, like Figure 2.4.

Figure 2.4 The schematic of a three-phase uncontrolled diode rectifier with line impedance on the ac side, and with dc link capacitor and resistive load on the dc side

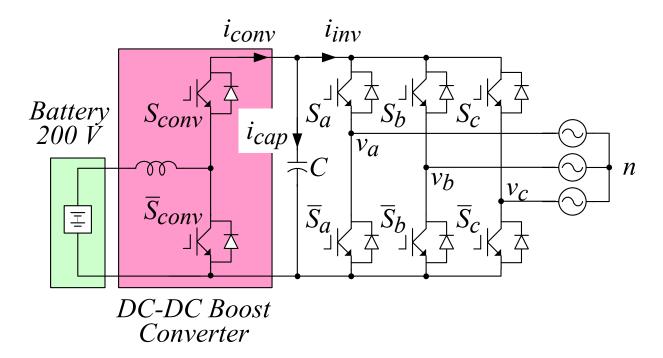

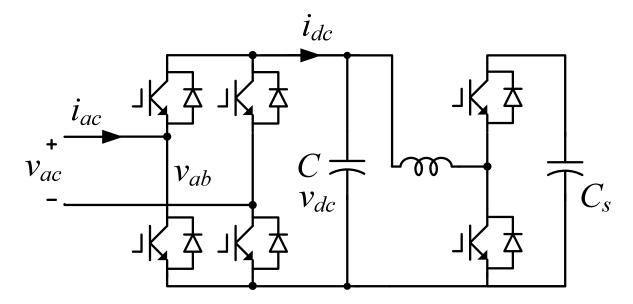

### 2.4.4 Synchronization between DC-DC Converter and SPWM Inverter

One last converter that have not been mentioned above is the dc-dc converter that connects the battery—the energy storage system—to the dc link. Therefore, this dc-dc converter contributes a certain amount of current harmonics to the dc link capacitor as well, which results in voltage ripples on the dc link. Consequently, in order to minimize the dc capacitance of the HEV systems, this part should be considered as well, which shows in Figure 2.5.

Figure 2.5 The schematic of a bidirectional dc-dc converter connected with a three-phase inverter with three-phase current sources as load

In conclusion, rectifiers and inverters, operated by SPWM and six-step mode, as well as the uncontrolled diode rectifier and dc-dc converter, are discussed in this thesis. Graphs, which show the right capacitance value for a given voltage ripple tolerance, are summarized at the end of each chapter.

### 2.5 Summary of Previous Work

#### 2.5.1 Complicated AC-DC-AC PWM Converter Control Strategies

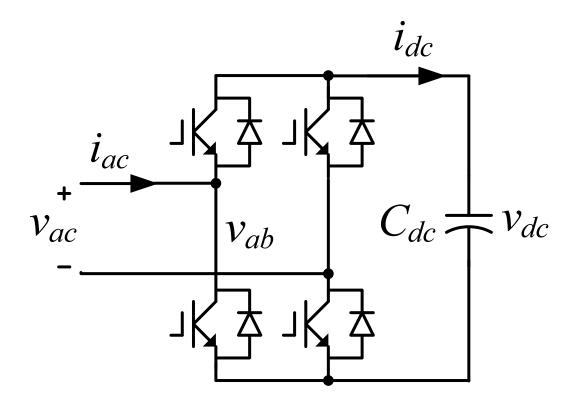

One of the typical AC-DC-AC PWM converters (sometimes called AC-AC converter) is shown in Figure 2.6. There are many papers discussing control strategies to reduce ripple current going through the dc link capacitor *C* by making the converter side dc link current the same as the inverter side dc link current, which theoretically needs no capacitance at all. For instance, direct capacitor current control [9], direct instantaneous input/output power balancing [10, 11], four-step commutation strategy [12], space vector modulation strategy [13], output current linearization feedback control (input/output current tracking) [14, 15], nonlinear control [16-18], and some other methods utilizing the current information. Also, there are a large number of papers discussing the matric converter or indirect matrix converter without dc link capacitor [19-21]. Similarly, they are all proposed with complicated close-loop control. However, there are few papers which discuss accurately obtaining the theoretical minimum capacitance for HEV systems by calculating the current ripple going through the dc link capacitor and voltage ripple across the dc link capacitor under open loop condition.

Figure 2.6 The schematic of a typical AC-DC-AC PWM converter system

# 2.5.2 Theoretical Analysis of Current Ripples and Harmonics of DC Capacitor

Some studies have been done on current ripple and harmonics of the dc link capacitor. For example, [22] is a very good paper about the rms current stress on the dc link capacitor for voltage source inverter (VSI) systems. In addition, [23, 24] are both on the topic of dc link current harmonics analysis. [25] is closer to the designer's viewpoint, but no closed-form equations of current ripple and capacitance value is derived. [26] did not give a theoretical calculation either. These papers provide a theoretical basis of the current ripple and harmonics. However, there are few papers talking about the voltage ripple and harmonics of the dc link capacitor. Also, there are few papers analyzed the current and voltage ripples through the Ampere-Second point of view, which is actually the source of the voltage ripple.

# 2.5.3 Simple Synchronization between DC-DC converter and SPWM Inverter to Minimize Capacitance

In the HEV converter/inverter system, inverters are always connected to dc-dc converters, for the sake of boosting the battery's low dc voltage to high dc voltage, and then converting into ac voltage to drive the traction motors, as shown in Figure 2.5. However, the dc link capacitor bank between the dc-dc converter and the inverter is usually bulky, heavy and expensive. Yet the bottleneck of the capacitor's size is determined by the current ripple requirement rather than the voltage ripple requirement. Hence, a better way to minimize the dc capacitance is narrowed down to minimize the current ripple through the capacitor by synchronizing the dc-dc converter and the SPWM inverter. The PWM and control techniques are fairly important. A good way will help minimizing the capacitance, whereas an unsuccessful one may need more capacitance than the normal operation.

Similar to the condition described in [9], in order to minimize the dc link capacitance between the dc-dc converter and SPWM inverter, making the converter side dc link current  $i_{CONV}$  equals to the inverter side dc link current  $i_{INV}$  in a pulsewidth modulation (PWM) converter-inverter system is the final destination, so that ideally no current will flow through the dc link capacitor and no voltage fluctuation will be across the capacitor, meaning no capacitor needed at all. Till now, most papers that discussed the current ripple reduction and the dc link capacitance minimization are based on the AC-DC-AC PWM converter-inverter systems with relatively complicated close-loop control methods [9-11, 14, 27-29]. The best result that they can achieve is almost without any dc link capacitors. Besides, there are papers discussing innovating PWM strategies only on inverter side allowing reduction of the dc input current ripples [30-32]. Furthermore, for DC-DC-AC PWM converter [33]. However, very few papers have been written

focusing on the current ripple reduction by synchronizing between the DC-DC converter and the SPWM inverter, the so-called DC-DC-AC PWM converters, which is also commonly existed in the HEV systems. [34] was a good start for the synchronization by making the DC-DC converter's switching frequency twice as much as the inverter's switching frequency and optimizing the phase difference of the carrier waveforms between the inverter carrier and DC-DC carrier. This method does decrease the current ripple quite a lot. In spite of this, more improvement can be done.

## 2.6 Goal and Methodology

When designing a voltage source inverter, the dc link capacitor is an important parameter to the designer. It is always preferred to know the capacitance's per unit value if given a percentage of the tolerable dc link voltage ripple. As a result, once we get a curve showing the relationship between the per unit value of the dc link capacitor and the desired voltage ripple percentage of the dc link, as well as taking consideration of a certain value of power factor, we can easily find out the capacitance by only checking the curve and then multiplying the capacitance base value. This makes life much easier. In conclusion, our task is to find the curve mentioned above, which shows the relationship between the per unit value of the capacitance and the dc link voltage ripple percentage.

For the sake of calculating the capacitance, (2.1) is the basic equation that comes up to one's mind, which express the current going through a capacitor,  $i_{cap}$ , is equal to the capacitance, C, times the derivative of the voltage across this capacitor,  $v_{cap}$ .

$$i_{cap} = C \frac{dv_{cap}}{dt} \tag{2.1}$$

Extract the capacitance C out of (2.1), one can get (2.2).

$$C = \frac{i_{cap} \cdot dt}{dv_{cap}} \tag{2.2}$$

Let's take a closer look at (2.2), the numerator is  $i_{cap} \cdot dt$ , which is a current times a time interval. From now on, it will be called "Ampere-Second", short as  $A \cdot sec$ , in this thesis. Moreover, the denominator  $dv_{cap}$ , is actually the dc link voltage ripple, due to the assumption that this thesis is only dealing with dc link capacitance calculation.

For the sake of deriving the dc link capacitance, according to (2.2) obtaining an accurate expression, for the  $i_{cap} \cdot dt$  —Ampere-Second  $(A \cdot sec)$ —of the ac ripple current  $i_{cap}$  that is flowing in and out of the dc link capacitor during one switching cycle, is the key point to get the required dc capacitance per unit (p.u.) value, of a given tolerable voltage ripple value, such as 10%.

Based on the previous discussion about the necessity and importance of finding the minimum dc capacitance for the HEV system, and the previous work that have done by others, here comes the outline of thesis.

Picking a dc link capacitor is decided by two constrains: one is the capacitance which is determined by the voltage ripple; the other one is the rms current ripple across the capacitor for the worst case, which will cause the capacitor internal temperature rise and has to be under a certain value to ensure the proper operation of the ordinary capacitors. Therefore, each chapter will be divided into basically two parts:

1. Calculation of the capacitance with a certain requirement of the voltage ripple endurance;

#### 2. Calculation of the rms current ripple.

Voltage ripple is more directly related to the capacitance, as one can see from (2.3). Therefore, in order to get the minimum capacitance for the system,  $i_{cap} \cdot dt$  (Ampere-Second) should be obtained first.

$$C = \frac{i_{cap} \cdot dt}{dv_{cap}} = \frac{i_{cap} \cdot dt}{\varepsilon V_{dc}}$$

(2.3)

These calculations have to be done for 3 different topologies that exists in the HEV systems: SPWM inverter (motoring low speed), 6-step inverter (motoring high speed), and diode rectifier (the PWM rectifier without controlling the switches).

In the following a few chapters, an accurate theory of calculating the voltage ripples and current ripples of the inverters and converters in HEV systems is presented, respectively. The topologies shown in Figure 2.2 (a) three-phase inverter/PWM rectifier, Figure 2.4 a three-phase uncontrolled diode rectifier, and Figure 2.5 a dc-dc converter, are mainly discussed in these chapters, which are the basic modules for a hybrid electric vehicle, both SHEV and PHEV. The voltage and current ripples of these cases are analyzed and summarized into graphs, which helps one to find the right capacitance value for a given voltage ripple tolerance and the rms ripple current that the capacitor has to absorb. Experiments are demonstrated with 510  $\mu$ F of dc link capacitance for a 150 kVA inverter, and the results verify the derived expressions.

# CHAPTER 3 DC Capacitance and Current

## Ripple Requirement of the Three-Phase

## **SPWM Inverter/PWM Rectifier**

Chapter 2 gives a general idea of why we need to minimize the dc link capacitor for HEV converter/inverter systems, and four topologies that are going to be discussed in this thesis. In this chapter, the objective is to find the requirement of the dc link capacitance and the current ripple for a three-phase SPWM inverter or a three-phase PWM rectifier. In fact, in terms of influence to the dc link capacitor voltage and current ripple, these two topologies are inherently the same. Therefore, only one needs to be analyzed, and the detailed analysis in this chapter is based on SPWM inverter [35].

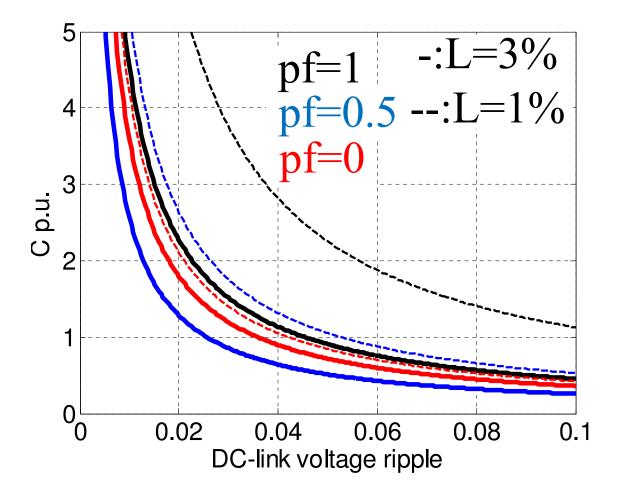

In order to make the conclusions more general and convenient for other designers to apply to their own applications, the results of the dc link capacitance requirement are analyzed and summarized into graphs at the end of this chapter according to the proposed accurate theory. The conclusive graphs can help to find the right capacitance value for a given voltage ripple tolerance and the rms current ripple that the capacitor has to absorb for different power factors.

Finally, this chapter ends up with the experimental results from a 150 kVA inverter prototype, which proves the calculation result and experimental result are in close agreement.

First of all, let's start from the first topology in Figure 2.2—the three-phase SPWM inverter/rectifier. (For convenience, Figure 2.2 is redrawn here as Figure 3.1 on the next page.)

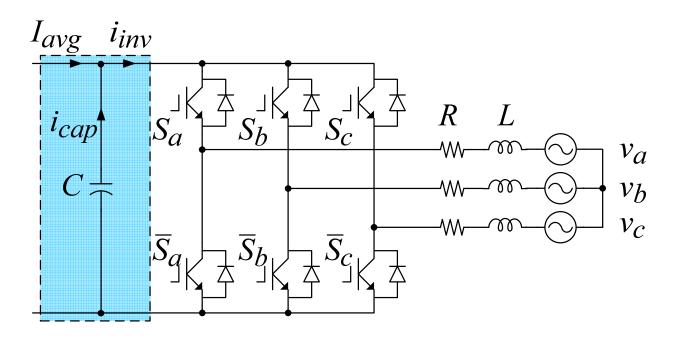

Figure 3.1 The schematic of a three-phase inverter/PWM rectifier using SPWM with three-phase current sources as load

## 3.1 Basic Idea of Calculating DC Link Capacitance

As mentioned in Chapter 2, for the sake of calculating the capacitance, (3.1) is the basic equation that comes up to one's mind, which express the current going through a capacitor,  $i_{cap}$ , is equal to the capacitance, C, times the derivative of the voltage across this capacitor,  $v_{cap}$ .

$$i_{cap} = C \frac{dv_{cap}}{dt} \tag{3.1}$$

Extract the capacitance C out of (3.1), one can get (3.2).

$$C = \frac{i_{cap} \cdot dt}{dv_{cap}} \tag{3.2}$$

In (3.2), the denominator, voltage ripple across the capacitor,  $dv_{cap}$ , is usually known for a design. In general, the smaller the capacitance is, the bigger the voltage ripple is. As a result, the bigger the voltage ripple on the dc link, the more harmonics goes to the ac side load. However, we want both small capacitor and low harmonics to the load. Obviously, there is a tradeoff between the two. This tradeoff is determined by the designer's target. Hence, this voltage ripple factor is considered a constant in the followed calculation.

Therefore, according to (3.2) and explanation in the above paragraph, the required dc capacitance C is proportional to the numerator,  $i_{cap} \cdot dt$ , which is called Ampere-Second ( $A \cdot sec$ ) in the later paragraphs.

In conclusion, an accurate expression for the minimum required dc link capacitance can be obtained by finding an accurate  $A \cdot sec$  expression of the ac ripple current  $i_{cap}$ , where  $i_{cap}$  represents the current going in and out of the dc link capacitor.

As explained above, the most challenging part of this calculation is to find an expression for  $A \cdot sec$ . This is achieved by integrating the positive/negative part of  $i_{cap}$  in one switching period. Obviously, if  $i_{cap}$  is integrated during one switching cycle, the result is zero because the dc link capacitor does not have a dc current offset, otherwise the dc link voltage will keep increasing and finally blow up the capacitor. That is why integrating the whole switching cycle does not help. Therefore, integrating either positive or negative part is the target.

## 3.2 Theoretical Basis

Figure 3.1 shows the schematic of a three-phase SPWM inverter/PWM rectifier with dc link capacitor and three-phase load/current source. Let's take a close look at this figure. First of all, it is desired to decompose the ideal inverter input current  $i_{inv}$  into two parts.

- A constant dc current  $I_{avg}$  is assumed to be supplied by a dc current source, which does not introduce any other current ripples. It can be imagined as a diode rectifier in series with a huge inductor. Although this does not really exist in the HEV system nowadays, the purpose of this assumption is eliminating all current ripples that coming from other sources, but only focusing on the current ripples that come from the SPWM inverter side, as shown in Figure 3.1.

- As one may already know, the other part of the ideal inverter input current  $i_{inv}$  is the ac ripple current  $i_{cap}$ , which flows in and out of the dc link capacitor bank, whose average is zero in every switching cycle and of course every fundamental cycle as well.

Therefore,  $I_{avg}$  is equal to the average of  $i_{inv}$ .

#### 3.2.1 Switching Functions

First of all, assume the rms value of the inverter output line-to-line voltage is  $V_{ac}$ , the 3rd harmonic injection is  $v_{3\omega}$  (the same to all three phases), the fundamental frequency in radian is

$\omega$ , the rms value of the inverter output line current is  $I_{ac}$ , the modulation index is M, and the power factor angle is  $\phi$ .

The inverter three-phase output voltages  $v_{an}$ ,  $v_{bn}$  and  $v_{cn}$  in Figure 3.1 can be expressed as shown in (3.3). Understand that the inverter three-phase output voltages are PWM waveforms. Equation (3.3) only shows their fundamental components. That is why they are sinusoidal expressions, without the summation of any higher order of sine terms.

$$v_{an} = \frac{\sqrt{2}}{\sqrt{3}} V_{ac} \sin(\omega t) + v_{3\omega}$$

$$v_{bn} = \frac{\sqrt{2}}{\sqrt{3}} V_{ac} \sin(\omega t - \frac{2}{3}\pi) + v_{3\omega}$$

$$v_{cn} = \frac{\sqrt{2}}{\sqrt{3}} V_{ac} \sin(\omega t + \frac{2}{3}\pi) + v_{3\omega}$$

(3.3)

Secondly, the inverter three-phase output currents  $i_a$ ,  $i_b$  and  $i_c$  are all perfect sinusoidal currents. For one thing, it is relatively reasonable because the traction motors are usually equivalent to huge inductors, which are enough to smooth out most of the ripples. For another thing, similar as previous explanation, it is desired to eliminate all the other ripples influence, and only focus on the ripples that generated by the SPWM operation method.

Similarly, the inverter output three phase currents  $i_a$ ,  $i_b$  and  $i_c$  can be expressed as shown in (3.4), where they are assumed to be perfect sinusoidal currents.

$$i_{a} = \sqrt{2}I_{ac}\sin(\omega t - \phi)$$

$$i_{b} = \sqrt{2}I_{ac}\sin(\omega t - \phi - \frac{2}{3}\pi)$$

$$i_{c} = \sqrt{2}I_{ac}\sin(\omega t - \phi + \frac{2}{3}\pi)$$

(3.4)

From Figure 3.2 and the proof in the Appendix, the switching functions of the three upper switches  $S_a$ ,  $S_b$  and  $S_c$  are obtained in (3.5).

$$S_{a} = \frac{1}{2} + \frac{1}{2}M \sin \omega t + \frac{v_{3}\omega}{V_{dc}}$$

$$S_{b} = \frac{1}{2} + \frac{1}{2}M \sin(\omega t - \frac{2}{3}\pi) + \frac{v_{3}\omega}{V_{dc}}$$

$$S_{c} = \frac{1}{2} + \frac{1}{2}M \sin(\omega t + \frac{2}{3}\pi) + \frac{v_{3}\omega}{V_{dc}}$$

$$(3.5)$$

### 3.2.2 Relationship between *Vdc* and *Vac*

Please note that the dc link voltage has a relationship with the ac output line-to-line voltage as shown in (3.6), under both normal modulation and over modulation, which means  $M \in [0, 1.15]$ .

$$M\frac{V_{dc}}{2} = \frac{\sqrt{2}}{\sqrt{3}}V_{ac} \tag{3.6}$$

#### 3.2.3 Average Current

The input real power of the inverter on the dc side can be expressed as (3.7).

$$P_{dc} = V_{dc} I_{avg} \tag{3.7}$$

The output real power of the inverter on the ac side can be expressed as (3.8).

$$P_{ac} = \sqrt{3}V_{ac}I_{ac}\cos\phi \tag{3.8}$$

The efficiency of the inverter is usually above 90%. This means the power loss is relatively small comparing to the total power. Therefore, if the power loss in the inverter is ignored, the input real power is equal to the output real power, as shown in (3.10).

$$V_{dc}I_{avg} = \sqrt{3}V_{ac}I_{ac}\cos\phi \tag{3.9}$$

Put  $I_{avg}$  on one side of the equation, and others on the other side. Equation (3.10) can be obtained.

$$I_{avg} = \sqrt{3} \frac{V_{ac}}{V_{dc}} I_{ac} \cos \phi \tag{3.10}$$

Hence, substituting (3.6) into (3.10), the average current (3.11) is obtained.

$$I_{avg} = \frac{3\sqrt{2}M}{4}I_{ac}\cos\phi \tag{3.11}$$

Similarly, the average current expression (3.11) can be achieved by substituting (3.4) and (3.5) into (3.12) as well, which means the switching functions shown in (3.5) are actually indicating the average duty cycle in each switching cycle.

$$I_{avg} = S_a i_a + S_b i_b + S_c i_c \tag{3.12}$$

## 3.3 Calculation of Required DC Link Capacitance

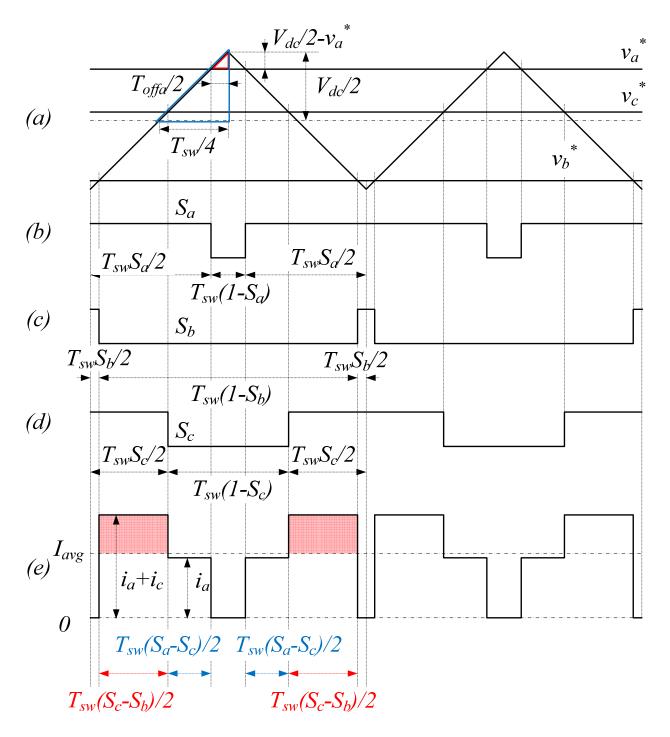

Figure 3.2 shows the PWM switching details during two switching cycles. Figure 3.2 (b) (c) (d) shows the switching functions of three phases determined by the traditional SPWM strategy, whose duty cycle in each switching period can be calculated from (3.5). In addition, Figure 3.2 (e) is the ideal inverter input current  $i_{inv}$ . As it is assumed the inverter is fed by a constant current source of  $I_{avg}$ , it can be understood that the current waveform that is flowing in and out of the dc link capacitor bank,  $i_{cap}$ , is the waveform in (e), but with  $I_{avg}$  as the x-axis instead of 0.

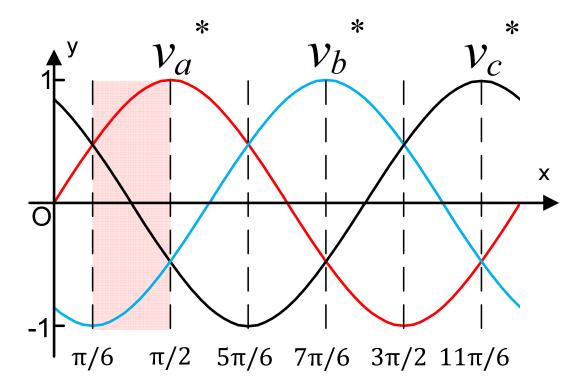

Instead of looking at the whole 360°, it is the same to analyze only 60°, for the reason that the waveforms are repeated in a low frequency at  $6\omega$  due to the three-phase system. Therefore, the following analysis will only focus on the range of 30° to 90° (take  $v_a$  as a reference), where  $v_a > v_c > v_b$ , drawed in pink (or shaded area) in Figure 3.3.

Figure 3.2 Detailed PWM waveforms in two switching periods (a) sinusoidal reference and triangle carrier waveforms;

- (b) switching function of phase A;

- (c) switching function of phase B;

- (d) switching function of phase C;

- (e) ideal inverter input current  $i_{inv}$  with  $I_{avg}$  showing in the same graph.