# **Final Program and Abstracts**

# Topical Workshop on Heterostructure Microelectronics for Information Systems Applications (TWHM-ISA '98)

19990322 003

DISTRIBUTION STATEMENT A Approved for Public Release Distribution Unlimited August 30-September 2, 1998

Shonan Village Center Hayama-machi, Kanagawa, Japan

AFOSR/AOARD ONR IEEE Electron Device Society In Cooperation with: The Japan Society of Applied Physics The Institute of Electronics, Information and Communication Engineers

DTIC QUALITY INSPECTED 1

**Sponsors:**

Reproduced From Best Available Copy

# Topical Workshop on Heterostructure Microelectronics for Information Systems Applications (TWHM-ISA '98)

Final Program and Abstracts

August 30-September 2, 1998

Shonan Village Center Hayama-machi, Kanagawa, Japan

Sponsors:

AFOSR/AOARD ONR IEEE Electron Device Society In Cooperation with: The Japan Society of Applied Physics The Institute of Electronics, Information and Communication Engineers

Front Cover Illustration: A work of Hokusai Katsushika "Soshu-Shichirigahama" Through the courtesy of THE ADACHI FOUNDATION FOR THE PRESERVATION OF WOODCUT PRINTING

| ublic reporting burden for this collection of information                                                                                                                                                                                                                   | CUMENTATION PA                                                                                                                                                                                                                                       |                                                                                                                                                                                            | Form Approved<br>OMB No. 0704-0188                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| amering and maintaining the data needed, and co                                                                                                                                                                                                                             | ation is estimated to average 1 hour per response<br>empleting and reviewing the collection of information                                                                                                                                           | e, including the time for reviewing                                                                                                                                                        | Instructions, searching existing data sources,                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| avis Highway, Suite 1204, Arlington, VA 22202-4<br>AGENCY USE ONLY (Leave blank)                                                                                                                                                                                            | 2. REPORT DATE                                                                                                                                                                                                                                       | 3. REPORT TYPE AND E                                                                                                                                                                       | (0704-0188), Washington, DC 20503.                                                                                                                                                                                                                                                 |

| AGENCT USE ONLY (Leave Diank)                                                                                                                                                                                                                                               | 15 March 99                                                                                                                                                                                                                                          |                                                                                                                                                                                            | ay 98 through 30 Oct.98                                                                                                                                                                                                                                                            |

| TITLE AND SUBTITLE                                                                                                                                                                                                                                                          | I I I I I I I I I I I I I I I I I I I                                                                                                                                                                                                                |                                                                                                                                                                                            | 5. FUNDING NUMBERS                                                                                                                                                                                                                                                                 |

| Workshop for Heteros                                                                                                                                                                                                                                                        | structure Microeled                                                                                                                                                                                                                                  |                                                                                                                                                                                            | 5. FUNDING NUMBERS                                                                                                                                                                                                                                                                 |

| Information Systems                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             | Applications (IWHM-                                                                                                                                                                                                                                  | -15A '90)                                                                                                                                                                                  | N00014-98-1-0582                                                                                                                                                                                                                                                                   |

| AUTHOR(S)                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | N00014-90-1-0902                                                                                                                                                                                                                                                                   |

| T. Ishibashi and D.                                                                                                                                                                                                                                                         | Pavlidic                                                                                                                                                                                                                                             |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| PERFORMING ORGANIZATION NAMES                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | 8. PERFORMING ORGANIZATION                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | REPORT NUMBER                                                                                                                                                                                                                                                                      |

| Office of Naval Res                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | December of Why                                                                                                                                                                                                                                                                    |

| Regional Office Chie                                                                                                                                                                                                                                                        | cago                                                                                                                                                                                                                                                 |                                                                                                                                                                                            | Regents of The<br>University of Michigan                                                                                                                                                                                                                                           |

| 536 S. Clark St., R                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | Tax# 386-00-6309                                                                                                                                                                                                                                                                   |

| Chicago, IL 60605-                                                                                                                                                                                                                                                          | 1583                                                                                                                                                                                                                                                 |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| SPONSORING / MONITORING AGENCY                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | 10. SPONSORING / MONITORING                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                             | 800 N. Quincy S                                                                                                                                                                                                                                      | St.                                                                                                                                                                                        | AGENCY REPORT NUMBER                                                                                                                                                                                                                                                               |

| Dr. John C. Zolper                                                                                                                                                                                                                                                          | Arlington, VA                                                                                                                                                                                                                                        | 22217-5660                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                    |

| Electronics Division                                                                                                                                                                                                                                                        | ÷ .                                                                                                                                                                                                                                                  |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| Office of Naval Rese                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| . SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| DISTRIBUTION / AVAILABILITY STATE                                                                                                                                                                                                                                           | MENT                                                                                                                                                                                                                                                 |                                                                                                                                                                                            | 12. DISTRIBUTION CODE                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| APPROVED FOR PUBLIC                                                                                                                                                                                                                                                         | RELEASE                                                                                                                                                                                                                                              |                                                                                                                                                                                            | DOD                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| 3. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| 3. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                  |

| 3. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                  |

| The 3rd Topical Worksho                                                                                                                                                                                                                                                     | op on Heterstructure Micros                                                                                                                                                                                                                          | electronics for Info                                                                                                                                                                       | rmation Systems Applications                                                                                                                                                                                                                                                       |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i                                                                                                                                                                                                                        | in Hayama-machi, Japan. A                                                                                                                                                                                                                            | special emphasis wa                                                                                                                                                                        | rmation Systems Applications<br>as placed on the applications in                                                                                                                                                                                                                   |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i                                                                                                                                                                                                                        | in Hayama-machi, Japan. A<br>his workshop. The Worksho                                                                                                                                                                                               | special emphasis want of sessions contain                                                                                                                                                  | as placed on the applications in a variety of contributions on                                                                                                                                                                                                                     |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits                                                                                                                                                          | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog                                                                                                                                                                 | special emphasis wa<br>op sessions contain<br>ties employed are ba                                                                                                                         | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar                                                                                                                                                                               |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure                                                                                                                          | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re                                                                                                                              | special emphasis wa<br>op sessions contain<br>gies employed are be<br>sonant tunneling die                                                                                                 | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety                                                                                                                                            |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure                                                                                                                          | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re                                                                                                                              | special emphasis wa<br>op sessions contain<br>gies employed are be<br>sonant tunneling die                                                                                                 | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety                                                                                                                                            |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of beterostructure material                                                                                           | in Hayama-machi, Japan. A<br>nis workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (                                                                                                | special emphasis was<br>op sessions contain<br>gies employed are bassonant tunneling die<br>e.g. GaAs, InP and                                                                             | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV                                                                                                            |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe                                                              | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re-<br>systems including III-Vs (<br>b), and wide bandgap semi-                                                                 | special emphasis was<br>op sessions contain<br>gies employed are be<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III                                                  | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special                                                                           |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed                                  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi-<br>on the effective insertion of                                 | special emphasis was<br>op sessions contain<br>gies employed are bas<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and                         | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as                                        |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed                                  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re-<br>systems including III-Vs (<br>b), and wide bandgap semi-                                                                 | special emphasis was<br>op sessions contain<br>gies employed are bas<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and                         | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as                                        |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed                                  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi-<br>on the effective insertion of                                 | special emphasis was<br>op sessions contain<br>gies employed are bas<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and                         | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as                                        |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed                                  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi-<br>on the effective insertion of                                 | special emphasis was<br>op sessions contain<br>gies employed are bas<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and                         | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as                                        |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in it<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed<br>mobile, fiber optic, space c | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi-<br>on the effective insertion of                                 | special emphasis was<br>op sessions contain<br>gies employed are bas<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and                         | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as<br>sing.                               |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed<br>mobile, fiber optic, space c  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi<br>on the effective insertion of<br>communications, as well as si | special emphasis was<br>op sessions contain<br>gies employed are be<br>esonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and<br>gnal and data proces | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as<br>sing.                               |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed<br>mobile, fiber optic, space c  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi-<br>on the effective insertion of                                 | special emphasis was<br>op sessions contain<br>gies employed are be<br>esonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and<br>gnal and data proces | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as<br>sing.<br>15. NUMBER OF PAGES<br>113 |

| The 3rd Topical Worksho<br>(TWHM-ISA '98), held in i<br>information systems for th<br>devices, materials, circuits<br>transistors, heterostructure<br>of heterostructure material<br>semiconductors (e.g. SiGe<br>emphasis was also placed<br>mobile, fiber optic, space c  | in Hayama-machi, Japan. A<br>his workshop. The Worksho<br>and systems. The technolog<br>field effect transistors and re<br>systems including III-Vs (<br>e), and wide bandgap semi<br>on the effective insertion of<br>communications, as well as si | special emphasis was<br>op sessions contain<br>gies employed are be<br>sonant tunneling did<br>e.g. GaAs, InP and<br>conductors (e.g. III<br>of these devices and<br>gnal and data proces  | as placed on the applications in<br>a variety of contributions on<br>ased on heterostructure bipolar<br>odes, and make use of a variety<br>related compounds), group IV<br>-V Nitrides and SiC). Special<br>d circuits into systems such as<br>sing.                               |

### **TWHM-ISA '98 COMMITTEE MEMBERS**

Workshop Co-Chairs:

Technical Program Co-Chairs:

Financial Administrator & Local Arrangements:

Secretary:

Sponsor Coordination:

Committee members:

D. Pavlidis (Univ. of Michigan) T. Ishibashi (NTT)

T. Mizutani (Nagoya Univ.) B. Bayraktaroglu (Northrop Grumman)

Y. Miyamoto (Tokyo Inst. Tech.)

C. Nguyen (Hughes Labs.)

S. Fujishiro (AFOSR/AOARD) K. White (AFOSR/AOARD)

D. D'Avanzo (Hewlett-Packard) T. Enoki (NTT) H. Hasegawa (Hokkaido Univ.) K. Hirakawa (Univ. of Tokyo) U. König (Daimler-Benz) K. Matsumoto (ETL) S. Matsushita (Sanyo Electric) U. Mishra (UCSB) Y. Mitsui (Mitsubishi) K. Mizuno (Tohoku Univ.) K. Morizuka (Toshiba) T. Nakamura (Hosei Univ.) S. Nishi (Oki Electric) T. Nozaki (NEC) H. Sato (Sharp) F. Schuermeyer (Wright Labs.) S. Takamiya (Kanazawa Univ.) H. Tokuda (Toshiba) D. Ueda (Matsushita) N. Yokoyama (Fujitsu) J. Zolper (ONR)

### **Sponsors and Cooperations**

Air Force Office of Scientific Research/ Asian Office of Aerospace R&D (Sponsor) Office of Naval Reseach (Sponsor) IEEE Electron Device Society (Technical Sponsor) The Japan Society of Applied Physics (Cooperation) The Institute of Electronics, Information and Communication Engineers (Cooperation)

### Preface

Welcome to the 1998 Topical Workshop on Heterostructure Microelectronics for Information Systems Applications (TWHM-ISA '98). Since 1994, when this Workshop began in Susono, it was followed by another successful meeting in Sapporo two years later and has become a well respected and recognized event for bringing up the latest achievements of Heterostructure Microelectronics as viewed by industry and university experts in the field. This year TWHM is being held in Hayama-machi on the beautiful Miura Peninsula and a new tone has been added to it by placing special emphasis on heterostructure microelectronics applications on information systems. This change is reflected by the addition of ISA to the Workshop name, and was prompted by the evolution of heterostructure microelectronics witnessed over the previous events and the fact that the heterostructure issues we address are no longer a future dream, but actual applications.

The sessions contain a variety of contributions on devices, materials, circuits and systems. The technologies employed are based on heterostructure bipolar transistors, heterostructure field effect transistors and resonant tunneling diodes, and make use of a variety of heterostructure material systems including III-Vs (e.g. GaAs, InP and related compounds), group IV semiconductors (e.g. SiGe), and wide bandgap semiconductors (e.g. III-V Nitrides and SiC). Special emphasis is also placed on the effective insertion of these devices and circuits into systems such as mobile, fiber optic, space communications, as well as signal and data processing.

We would like to take this opportunity to thank the workshop committee members of TWHM-ISA '98 for soliciting papers and arranging the excellent program. The financial and organizing support made by the Asian Office of Aerospace Research and Development (AOARD), and the Office of Naval Research (ONR) are also greatly appreciated. Technical sponsorship by the IEEE Electron Device Society, the Japan Society of Applied Physics, and the Institute of Electronics, Information and Communication Engineers has also been instrumental in the organization of this Workshop.

On behalf of the Organizing Committee and the Technical Program Committee, we welcome you to the 1998 Topical Workshop on Heterostructure Microelectronics for Information Systems Applications. We hope you will enjoy the presentations and encourage you to share your experience with others in order to ensure a very productive Workshop and contribute to the successful expansion of the field of Heterostructure

Microelectronics.

Dimitris Pavlidis Workshop Co-Chair Tadao Ishibashi Workshop Co-Chair

| (E | WHMJ |  |

|----|------|--|

| ゾ  | ISA  |  |

## CONTENTS

| Committee |        | ii |

|-----------|--------|----|

|           |        |    |

| Preface   | ······ |    |

# Final Program

# SESSION 1 HIGH-SPEED & HIGH-FREQUENCY DEVICES Monday, August 31

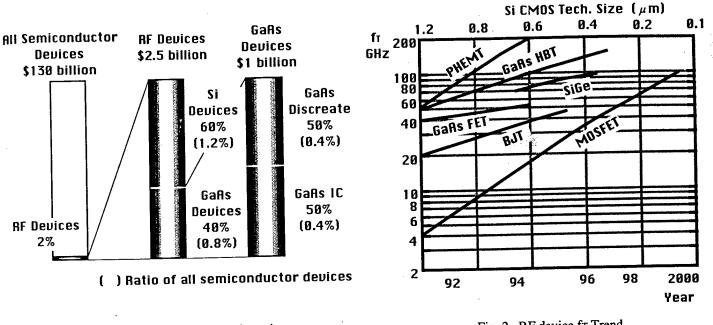

|      | 9:20                             | S1-1                         | Compound Semiconductor Devices for Future Data Transmission Systems (Invited)<br>M. Takigawa (Fujitsu Laboratories Ltd., Japan)                                                                                                                                              | 2                    |

|------|----------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

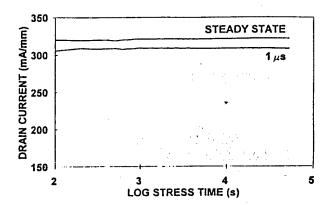

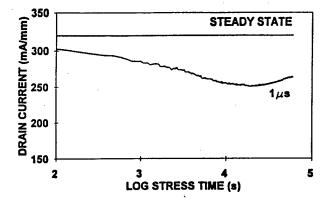

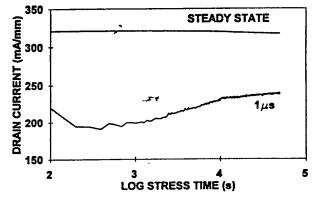

| .45  | - 10:00                          | S1-2                         | Correlation Between Gate Lag, Power Drift and Power Slump of Digitally Modulated<br>RF Power PHEMTs for Wireless Communication Applications (Invited)<br>J. C. M. Hwang (Lehigh University, USA)                                                                             | 4                    |

| 9,10 | 10:20                            | S1-3                         | Novel HEMT Processing Technologies and Their Circuit Applications (Invited)<br>I. Adesida, A. Mahajan and G. Cueva (University of Illinois, USA)                                                                                                                             | 6                    |

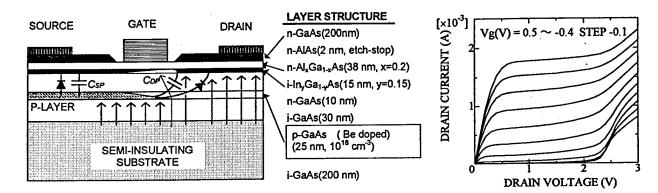

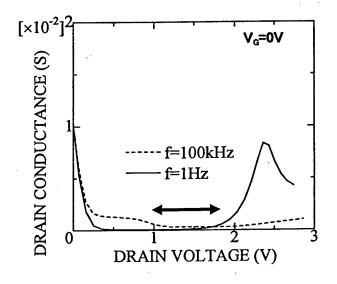

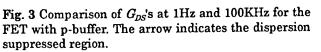

|      | 10:35                            | S1-4                         | Suppression of G <sub>DS</sub> Frequency Dispersions in Heterojunction FETs with a Partially<br>Depleted p-Type Buffer Layer<br>Y. Ohno, S. Ohkubo, K. Kasahara, K. Kunihiro and Y. Takahashi (NEC Co., Japan)                                                               | 8                    |

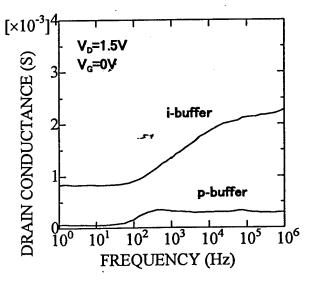

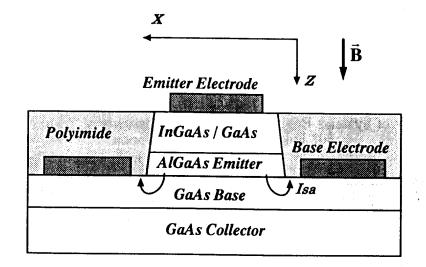

|      | 10:40                            | S1-5                         | A New Method for Evaluation of Surface Recombination in Heterojunction Bipolar<br>Transistors by Magnetotransport<br>T. Nozu, T. Sugiyama, S. Hongo, K. Tsuda and K. Morizuka (Toshiba Co., Japan)                                                                           | 10                   |

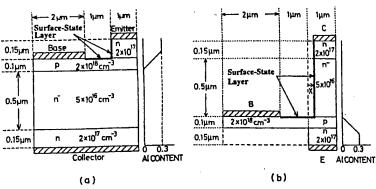

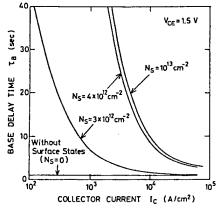

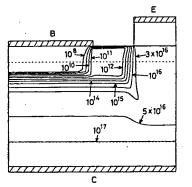

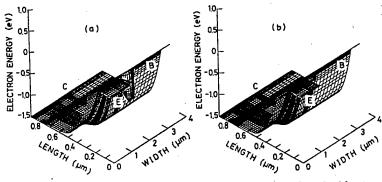

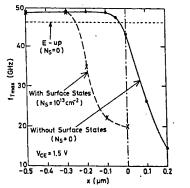

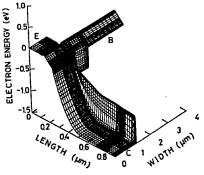

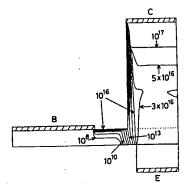

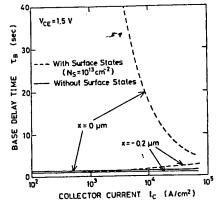

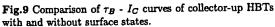

|      | 10:45                            | S1-6                         | Effects of Surface States on Cutoff Frequency Characteristics of AlGaAs/GaAs HBTs<br>K. Horio and N. Kurosawa (Shibaura Institute of Technology, Japan)                                                                                                                      |                      |

|      |                                  |                              |                                                                                                                                                                                                                                                                              |                      |

|      |                                  |                              | 2 NOVEL DEVICES Monday, August                                                                                                                                                                                                                                               | 31                   |

|      |                                  |                              | 2 NOVEL DEVICES<br>Resonant-Tunneling Analog/Mixed-Signal Circuit Technology(Invited)<br>A. Seabaugh, B. Brar, T. Broekaert, F. Morris and G. Frazier<br>(Raytheon Systems Company, USA)                                                                                     |                      |

|      | 11:10                            | S2-1                         | Resonant-Tunneling Analog/Mixed-Signal Circuit Technology(Invited)                                                                                                                                                                                                           | 14                   |

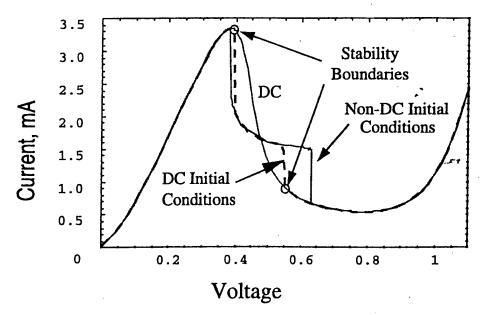

|      | 11:10<br>11:35                   | S2-1<br>S2-2                 | Resonant-Tunneling Analog/Mixed-Signal Circuit Technology(Invited)<br>A. Seabaugh, B. Brar, T. Broekaert, F. Morris and G. Frazier<br>(Raytheon Systems Company, USA)                                                                                                        | 14<br>16             |

|      | 11:10<br>11:35<br>12:00          | S2-1<br>S2-2<br>S2-3         | Resonant-Tunneling Analog/Mixed-Signal Circuit Technology(Invited)<br>A. Seabaugh, B. Brar, T. Broekaert, F. Morris and G. Frazier<br>(Raytheon Systems Company, USA)<br>Influence of RTD Device Physics on Circuit Performance (Invited)<br>J. N. Schulman (HRL Labs., USA) | 14<br>16<br>18       |

|      | 11:10<br>11:35<br>12:00<br>12:25 | S2-1<br>S2-2<br>S2-3<br>S2-4 | <ul> <li>Resonant-Tunneling Analog/Mixed-Signal Circuit Technology(Invited)         <ul> <li>A. Seabaugh, B. Brar, T. Broekaert, F. Morris and G. Frazier</li></ul></li></ul>                                                                                                | 14<br>16<br>18<br>20 |

| SESSI | ON 3          | MICROWAVE/MILLIMETER WAVE DEVICES Monday, August 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |               | Advanced Heterostructure Transistor Technologies for Wireless Communications (Invited)<br>N. L. Wang (EiC Co., USA)                                                                                                                                                                                                                                                                                                                                                                                                    |

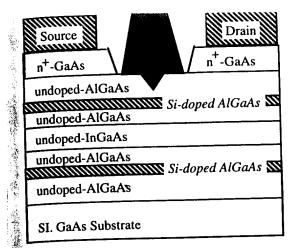

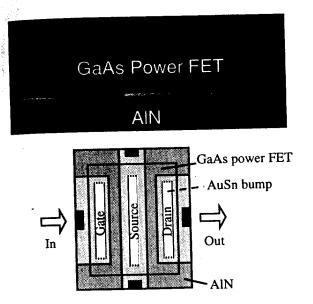

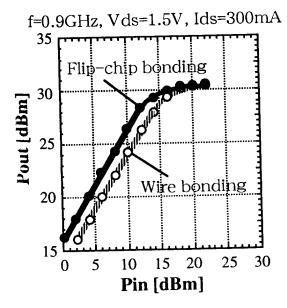

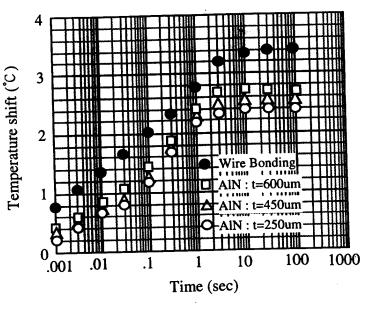

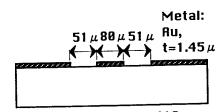

| 14:25 | <b>S</b> 3-2  | A Novel GaAs Flip-Chip Power FET with High Gain and Efficiency (Invited)<br>T. Tanaka, H. Furukawa, H. Nagata and D. Ueda (Matsushita Electronics Co., Japan)                                                                                                                                                                                                                                                                                                                                                          |

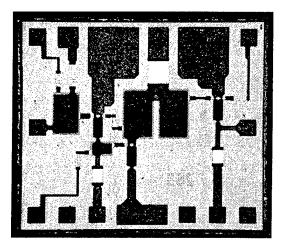

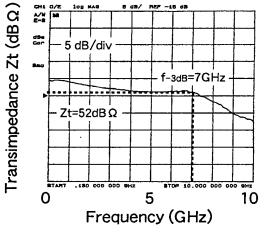

| 14:50 | S3-3          | A Low Power Dissipation 0.4~0.7 GHz Transimpedance Amplifier IC for SCM Optical                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |               | K. Fujimoto, H. Masato, K. Kawashima, M. Nishitsuji, M. Tanaka*, Y. Kudo** and O. Ishikawa<br>(Matsushita Electronics Co., Japan, *Matsushita Communication Kanazawa R&D Labs. Co., Ltd., Japan,<br>**Matsushita Communication Ind. Co., Ltd., Japan)                                                                                                                                                                                                                                                                  |

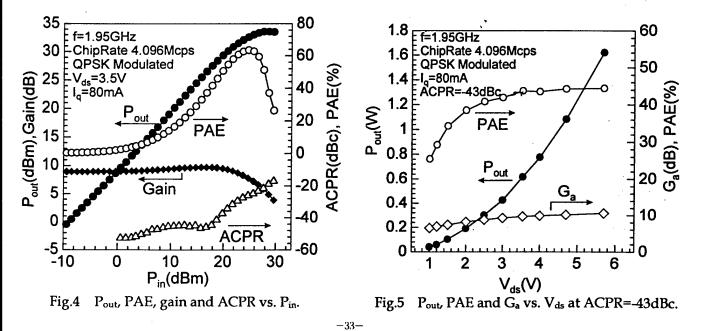

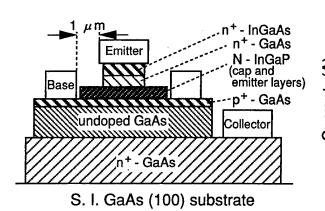

| 14:55 | <b>S3-4</b>   | 44% Efficiency Power Heterojunction FET Operated at 3.5 V for 1.95 GHz Wide-Band<br>CDMA Cellular Phones                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15:00 | S3-5          | T. B. Nishimura, N. Iwata, M. Tomita and Y. Bito (NEC Co., Japan)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |               | Current-Density Condition<br>K. Mochizuki, T. Oka and T. Tanoue ( <i>Hitachi Ltd., Japan</i> )                                                                                                                                                                                                                                                                                                                                                                                                                         |

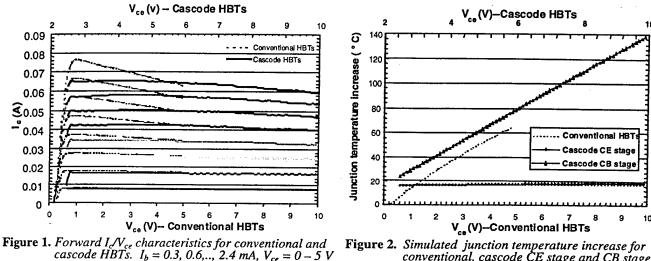

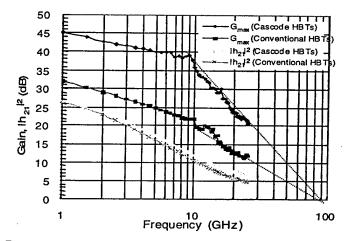

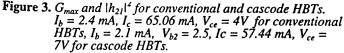

| 15:05 | S3-6          | Comparison of Conventional and Thermally-Stable Cascode (TSC) AlGaAs/GaAs HBTs for<br>Microwave Power Applications                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |               | S. S. H. Hsu <sup>*</sup> , B. Bayraktaroglu <sup>†</sup> and D. Pavlidis <sup>*</sup> (*The Univ. of Michigan, USA,<br><sup>†</sup> Northrop Grumman Co.,USA)                                                                                                                                                                                                                                                                                                                                                         |

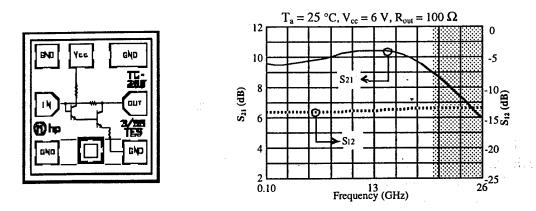

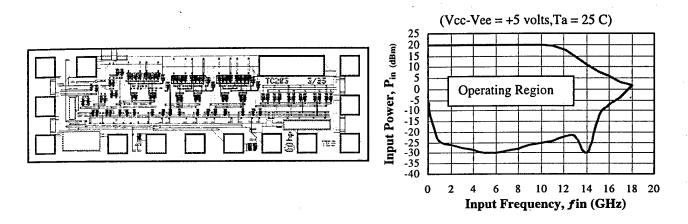

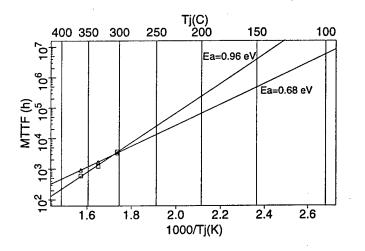

| 15:10 | S3-7          | InGaP HBT Technology for RF and Microwave Instrumentation<br>T. Low, T. Shirley, C. Hutchinson, G. Essilfie, W. Whiteley, B. Yeats and D. D'Avanzo<br>(Hewlett-Packard Co., USA)                                                                                                                                                                                                                                                                                                                                       |

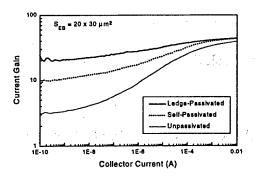

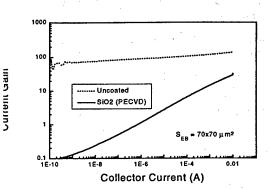

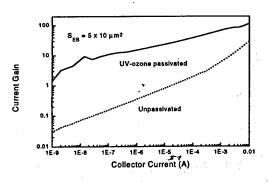

| 15:15 | S3-8          | Passivation of InP-based HBTs         R. Driad, S. Laframboise, S. P. McAlister and W. R. McKinnon         (National Rsearch Council of Canada, Canada)                                                                                                                                                                                                                                                                                                                                                                |

| SESS  | SION          | 4 WIDE BANDGAP DEVICES Monday, August 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

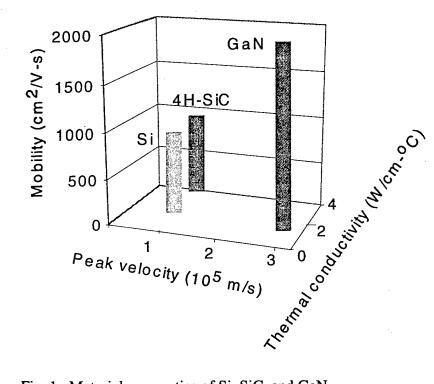

|       |               | GaN-based Electronic Devices (Invited)<br>M. S. Shur and R. Gaska* (Rensselaer Polytechnic Institute, USA, *APA Optics, Inc., USA)                                                                                                                                                                                                                                                                                                                                                                                     |

| 16:05 | S4-2          | <ul> <li>Lateral Epitaxial Overgrowth (LEO) for Low Defect Density GaN on Sapphire (Invited)</li> <li>S. P. DenBaars, H. Marchand, J. P. Ibbetson, P. T. Fini, S. Chichibu, S. J. Rosner<sup>1</sup>, S. Keller,</li> <li>J. S. Speck and U. K. Mishra (Univ. of California, USA, <sup>1</sup>Hewlett-Packard Labs., USA)</li></ul>                                                                                                                                                                                    |

| 16:30 | ) S4-3        | <ul> <li>SiC and GaN Wide Bandgap Semiconductor Materials and Devices (Invited)</li> <li>A. A. Burk, Jr.<sup>1</sup>, M. J. O'Loughlin<sup>1</sup>, R. R. Siergiej<sup>2</sup>, A. K. Agarwal<sup>2</sup>, S. Sriram<sup>2</sup>, R. C. Clarke<sup>2</sup>,</li> <li>M. F. MacMillan<sup>2</sup>, V. Balakrishna<sup>2</sup> and C. D. Brandt<sup>2</sup>, (<sup>1</sup>Northrop Grumman ESSD Advanced<br/>Technology Laboratory, USA, <sup>2</sup>Northrop Grumman ESSD Science and Technology Center, USA)</li></ul> |

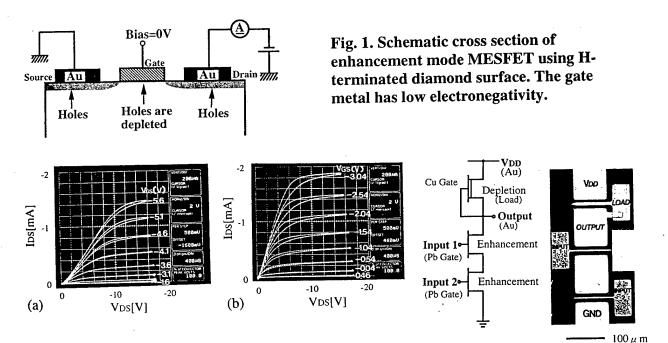

| 16:55 | 5 S4-4        | <ul> <li>Diamond Field Effect Transistors using Hydrogen-terminated Surface (Invited)</li> <li>H. Kawarada (Waseda University, Japan)</li></ul>                                                                                                                                                                                                                                                                                                                                                                        |

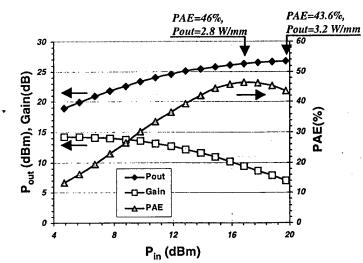

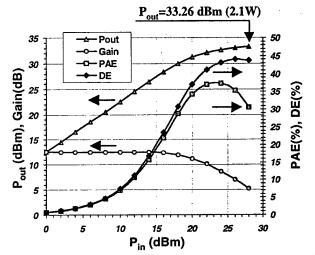

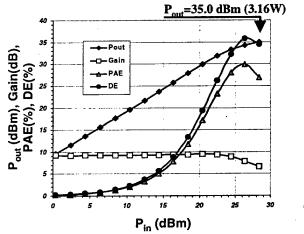

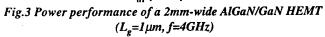

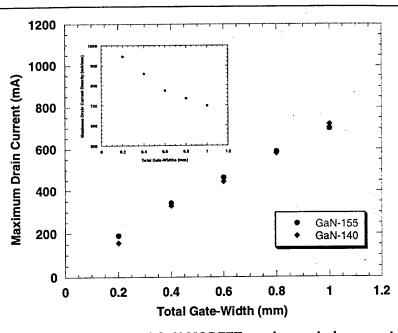

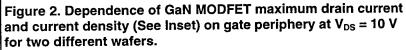

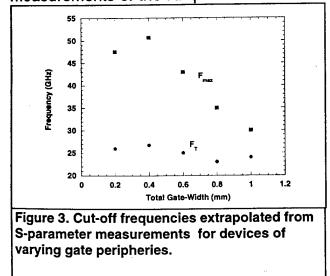

| 17:20 | 0 <b>S</b> 4- | <ul> <li>GaN Microwave HEMTs</li> <li>YF. Wu*, B. J. Thibeault*, B. P. Keller*, S. Keller**, S. P. Denbaars** and U. K. Mishra**</li> <li>(*WiTech, Goleta, USA, **University of California, USA)</li></ul>                                                                                                                                                                                                                                                                                                            |

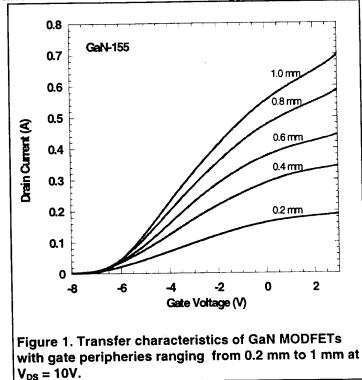

| 17:2  | 5 S4-         | <ul> <li>6 GaN MODFET Microwave Power Technology for Future Generation Radar and</li> <li>Communications Systems</li> <li>D. E. Grider, N. X. Nguyen and C. Nguyen (HRL Labs., USA)</li></ul>                                                                                                                                                                                                                                                                                                                          |

| 17:30 | S4-7  | Progress Towards Ultra-Wideband AlGaN/GaN MMICs<br>J. C. Zolper (Office of Naval Research, USA)                                                                                                                                                                                                                          | 54 |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 17:35 | S4-8  | <b>Optimization of Schottky Gate Formation Process for n-Channel GaN MESFETs</b><br>Y. Koyama, T. Hashizume and H. Hasegawa ( <i>Hokkaido University, Japan</i> )                                                                                                                                                        | 56 |

| SESS  | ION 5 | CIRCUIT APPLICATIONS, DEVICE FABRICATION AND CHARACTERIZATION<br>Tuesday, September 1                                                                                                                                                                                                                                    |    |

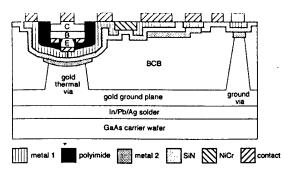

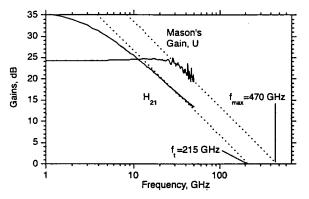

| 9:00  | S5-1  | Novel Bipolar Technologies and Their Circuit Applications (Invited)<br>M. Rodwell, Q. Lee, D. Mensa, J. Guthrie, S. C. Martin <sup>*</sup> , R. P. Smith <sup>*</sup> , R. Pullela, B. Agarwal,<br>S. Jaganathan, T. Mathew and S. Long ( <i>University of California, USA,</i><br>* Jet Propulsion Labs., Caltech, USA) | 58 |

| 9:25  | S5-2  | SiGe Heterostructure CMOS Circuits and Applications (Invited)<br>E. H. C. Parker and T. E. Whall (University of Warwick, UK)                                                                                                                                                                                             | 60 |

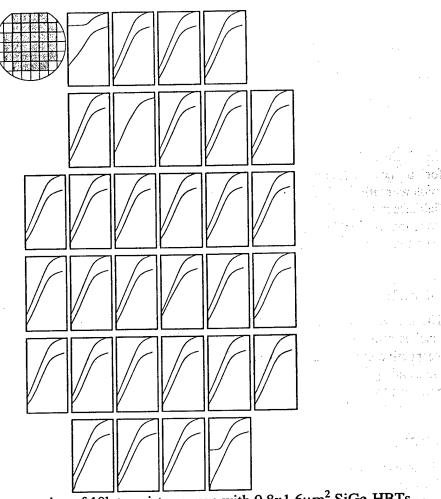

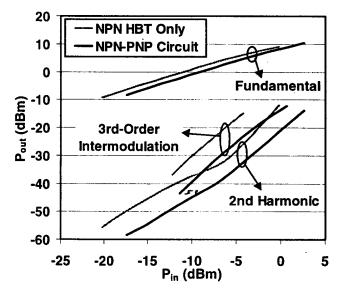

| 9:50  | S5-3  | Power Amplification using NPN and PNP InP HBTs and Application to Push-Pull Circuits<br>D. Sawdai, D. Pavlidis and S. Mohammadi ( <i>Univ. of Michigan, USA</i> )                                                                                                                                                        | 62 |

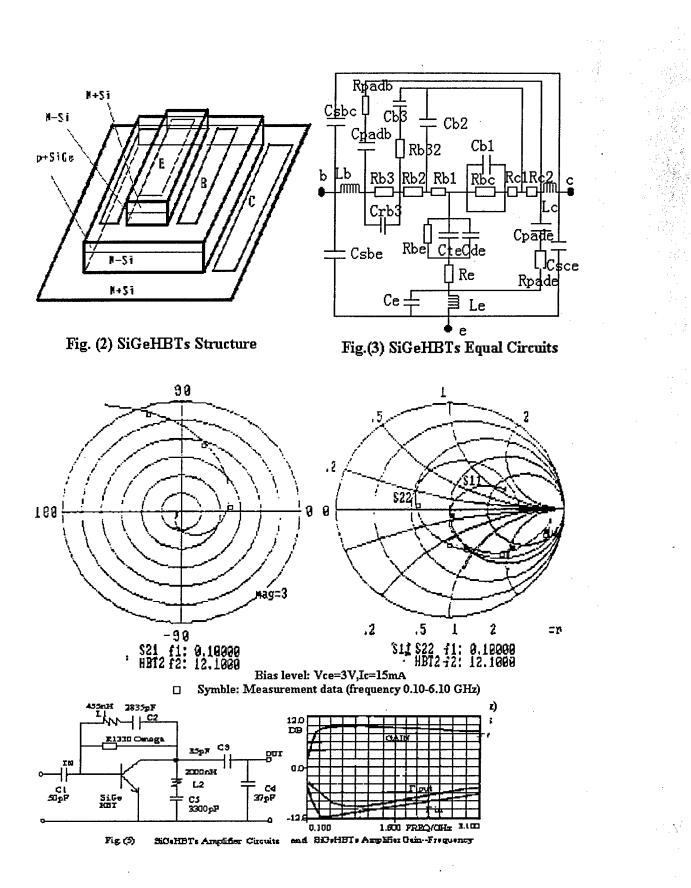

| 9:55  | S5-4  | Simulation of the Microwave Performance of SiGe HBTs and Its Amplifiers<br>L. X. Zhao and G. D. Shen ( <i>Beijing Polytechnic University, China</i> )                                                                                                                                                                    | 64 |

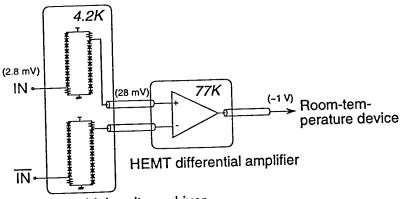

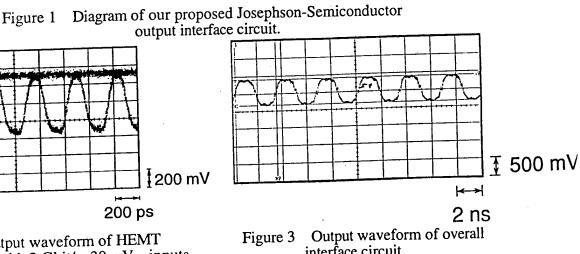

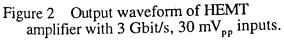

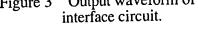

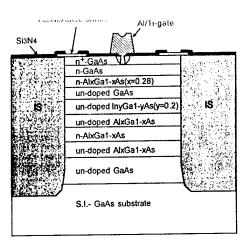

| 10:00 | S5-5  | 77K Analog Monolithic HEMT Amplifier for High-Speed Josephson-Semiconductor<br>Interface Circuit<br>N. Harada, Y. Awano, K. Hikosaka and N. Yokoyama (Fujitsu Ltd., Japan)                                                                                                                                               | 66 |

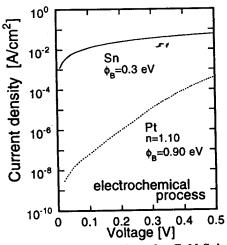

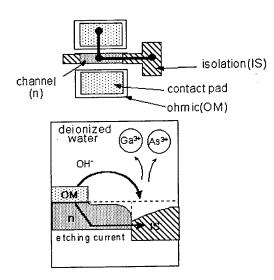

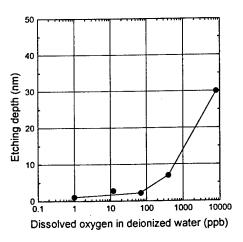

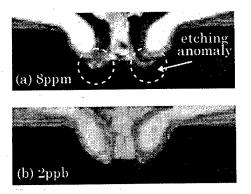

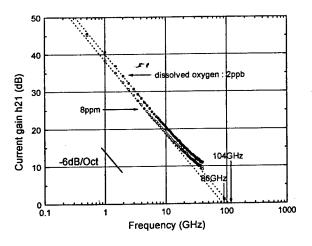

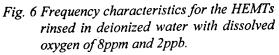

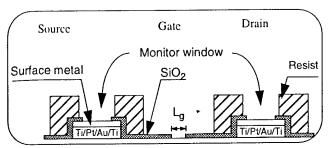

| 10:05 | S5-6  | Improvement of 0.1 µm-Gate InGaAs/AlGaAs HEMT Performance by Suppression of<br>Electro-Chemical Etching in Deionized Water<br>T. Ohshima, R. Shigemasa, M. Sato, M. Tsunotani and T. Kimura<br>(Oki Electric Industry Co., Ltd., Japan)                                                                                  | 68 |

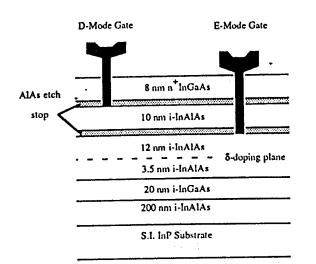

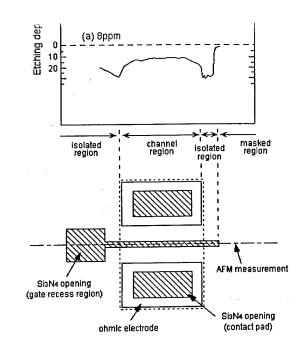

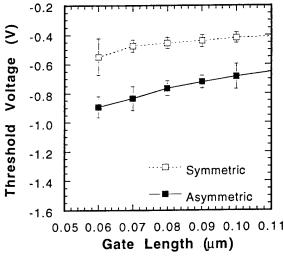

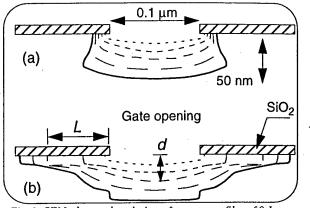

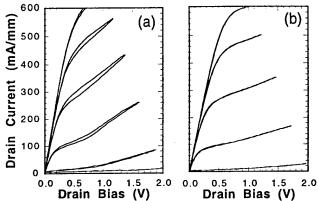

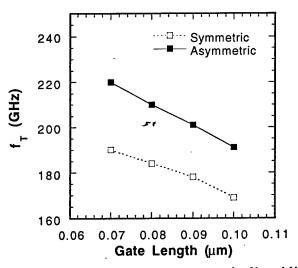

| 10:10 | S5-7  | Electrochemical Formation of Asymmetry in Gate-recess Grooves for InAlAs/InGaAs MODFETs<br>with Short Gate-lengths<br>D. Xu, T. Enoki, T. Suemitsu, Y. Umeda, H. Yokoyama and Y. Ishii<br>(NTT System Electronics Labs., Japan)                                                                                          | 70 |

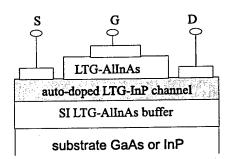

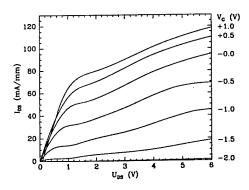

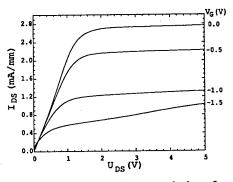

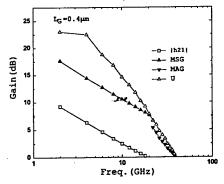

| 10:15 | S5-8  | Demonstration of Low Temperature Grown InP-Channel HFET Transferred onto GaAs Substrate<br>M. Kunze, L. H. Lee, H. Y. Chung and E. Kohn (University of Ulm, Germany)                                                                                                                                                     | 72 |

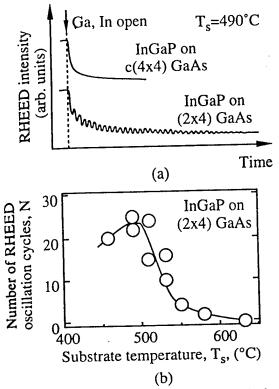

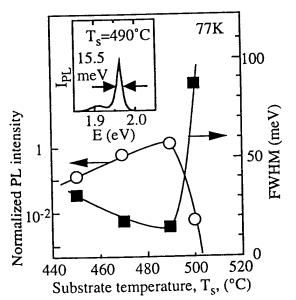

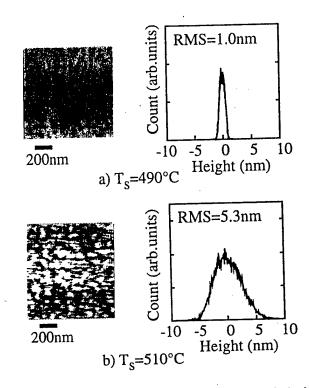

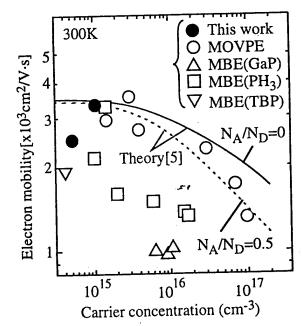

| 10:20 | S5-9  | Growth of Device Quality InGaP/GaAs Heterostructure by GSMBE using TBP<br>H. Sai, H. Fujikura, A. Hirama and H. Hasegawa (Hokkaido University, Japan)                                                                                                                                                                    | 74 |

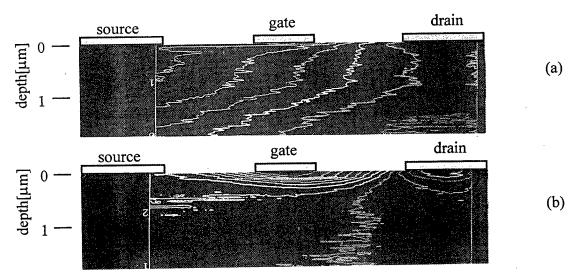

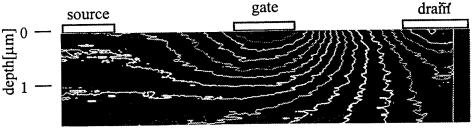

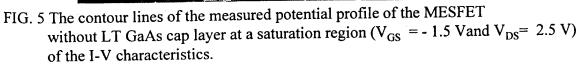

| 10:25 | S5-10 | Potential Profile Measurement of GaAs MESFETs Passivated with Low-Temperature Grown<br>GaAs Layer by Kelvin Probe Force Microscopy<br>K. Matsunami, T. Usunami, S. Kishimoto, K. Maezawa, T. Mizutani, P. Schmid* and K. M. Lipka*<br>(Nagoya University, Japan, * University of Ulm, Germany)                           | 76 |