# Xilinx Memory Interface Generator (MIG) 1.5 User Guide

DDR SDRAM, DDRII SRAM, DDR2 SDRAM, QDRII SRAM, and RLDRAM II Compilers

UG086 (v1.5) February 15, 2006

Xilinx is disclosing this Specification to you solely for use in the development of designs to operate on Xilinx FPGAs. Except as stated herein, none of the Specification may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of this Specification may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

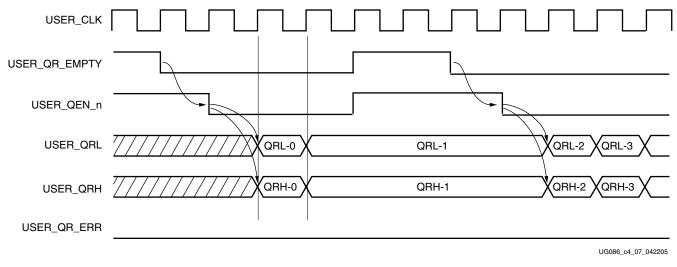

Xilinx does not assume any liability arising out of the application or use of the Specification; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Specification. Xilinx reserves the right to make changes, at any time, to the Specification as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Specification.

THE SPECIFICATION IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE SPECIFICATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE SPECIFICATION, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE SPECIFICATION, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE SPECIFICATION. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE SPECIFICATION TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Specification is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Specification in such High-Risk Applications is fully at your risk.

© 2005, 2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

## **Revision History**

| Date     | Version | Revision                 |

|----------|---------|--------------------------|

| 10/01/04 | 1.0     | Initial MIG 1.0 release. |

| 01/01/05 | 1.1     | MIG 1.1 release.         |

| 05/01/05 | 1.2     | MIG 1.2 release.         |

| 08/18/05 | 1.3     | MIG 1.3 release.         |

| 11/04/05 | 1.4     | MIG 1.4 release.         |

| 02/15/06 | 1.5     | MIG 1.5 release.         |

The following table shows the revision history for this document.

# Table of Contents

|      | Revision History                            | . 2 |

|------|---------------------------------------------|-----|

| Pref | ace: About This Guide                       |     |

|      | Guide Contents                              | 9   |

|      |                                             |     |

|      | References                                  |     |

|      | Additional Resources                        |     |

|      | Typographical Conventions                   | 11  |

| Cha  | pter 1: Using the MIG 1.5 Tool              |     |

|      | MIG 1.5 Tool Changes from MIG 1.4           | 14  |

|      | Tool Features                               |     |

|      | Xilinx Design Tools Version Requirements    |     |

|      |                                             |     |

|      | Installation                                |     |

|      | Method 1                                    |     |

|      | Method 2                                    |     |

|      | Getting Started                             |     |

|      | User Options                                |     |

|      | Part Selection – Target and Compatible Part |     |

|      | Clocking Type                               |     |

|      | Use CC (for Direct Clocking)                |     |

|      | Frequency                                   |     |

|      | Memory                                      |     |

|      | Data Width and Depth                        |     |

|      | View Memory Details                         |     |

|      | View HW Tested Configs                      |     |

|      | Set Mode Register(s)                        |     |

|      | Set Advanced Options                        |     |

|      | View All Controllers                        |     |

|      | Design Parameters                           |     |

|      | Add Test Bench                              |     |

|      | Use DCM                                     |     |

|      | Edit Signal Names                           |     |

|      | Output Directory                            |     |

|      | Module Name                                 |     |

|      | Select Banks                                |     |

|      |                                             |     |

|      | Verify my ucf                               |     |

|      |                                             |     |

|      |                                             | 25  |

|      |                                             | 25  |

|      |                                             | 26  |

|      |                                             | 26  |

|      | User Guide                                  |     |

|      | Version Info                                | 26  |

## **SECTION 1: VIRTEX-4 FPGA TO MEMORY INTERFACES**

## **Chapter 2: Implementing DDR SDRAM Controllers**

| Feature Summary 29                              |

|-------------------------------------------------|

| Architecture                                    |

| Interface Model                                 |

| Implemented Features                            |

| Burst Length                                    |

| CAS Latency                                     |

| Registered DIMMs 31                             |

| Precharge                                       |

| Auto Refresh                                    |

| Different Memories (Density/Speed)              |

| Hierarchy                                       |

| DDR Controller Submodules 34                    |

| Controller                                      |

| Datapath                                        |

| User Interface                                  |

| Infrastructure                                  |

| IOBS Module                                     |

| DDR SDRAM Memory Initialization and Calibration |

| DDR SDRAM System and User Interface Signals     |

| DDR SDRAM Writes (User Interface)               |

| DDR SDRAM Reads (User Interface)                |

# **Chapter 3: Implementing DDR2 SDRAM Controllers**

| Interface Model                        | 41 |

|----------------------------------------|----|

| Direct Clocking Interface              | 42 |

| Feature Summary                        | 42 |

| Supported Features                     | 42 |

| Unsupported Features                   | 42 |

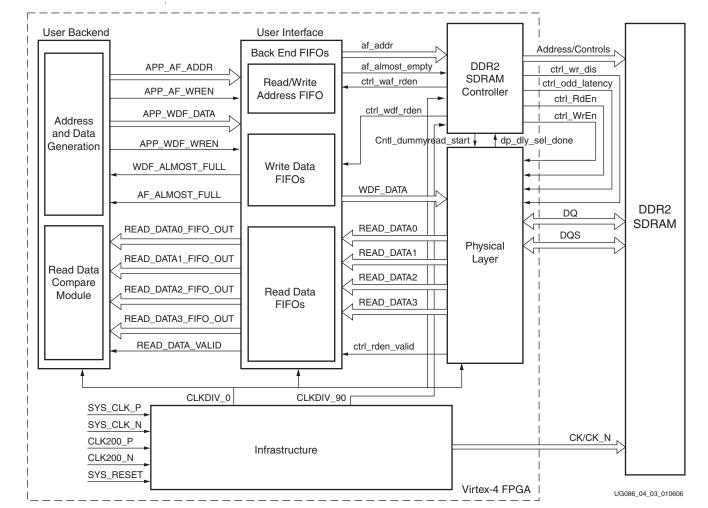

| Architecture                           | 43 |

| Implemented Features                   | 43 |

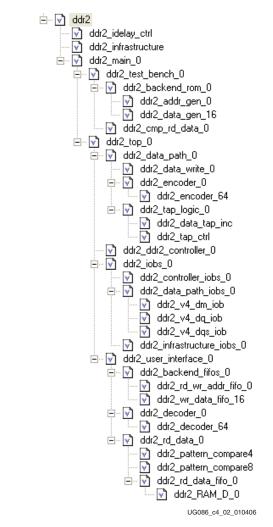

| Hierarchy                              | 46 |

| DDR2 Controller Submodules             | 46 |

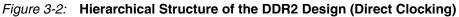

| DDR2 SDRAM User Interface Signals      | 49 |

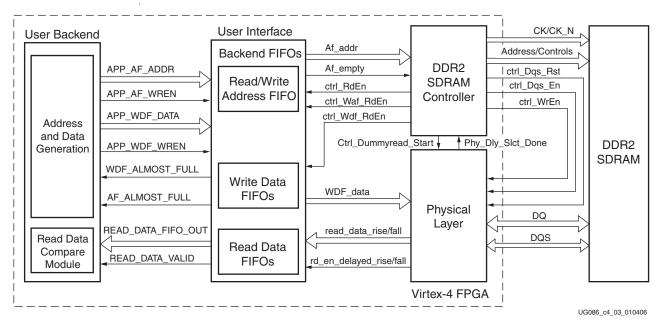

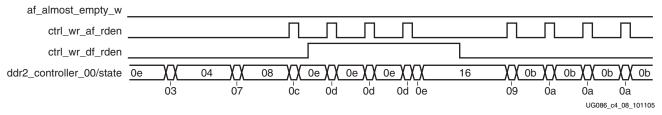

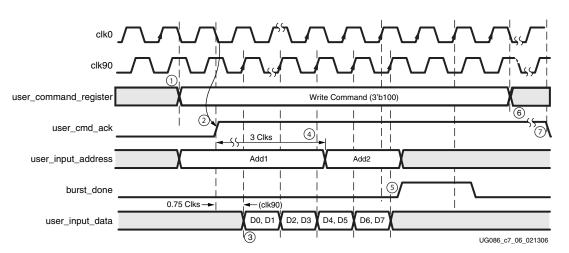

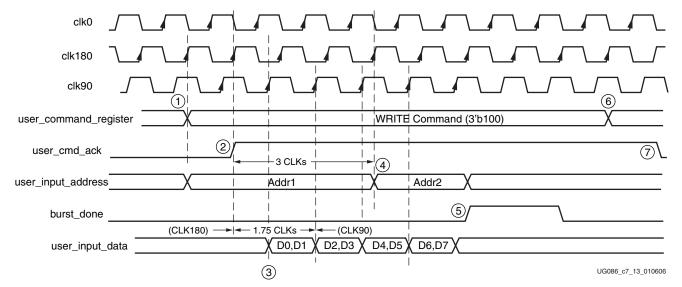

| DDR2 SDRAM Writes                      | 50 |

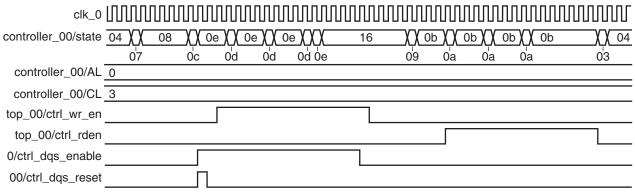

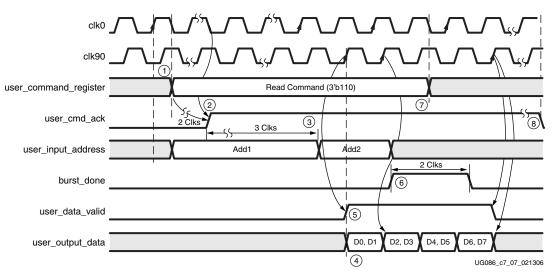

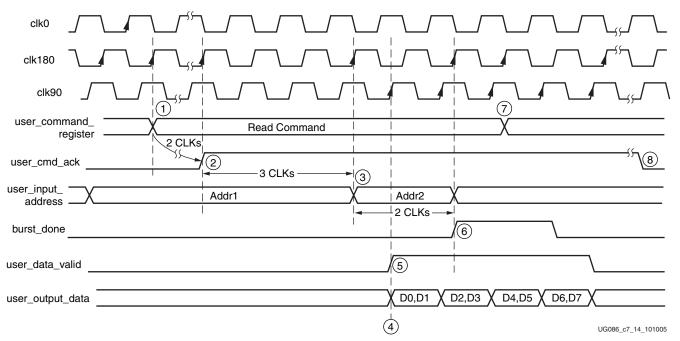

| DDR2 SDRAM Reads                       | 52 |

| User to Controller Interface           | 53 |

| Dynamic Command Request                | 55 |

| Controller to Physical Layer Interface | 56 |

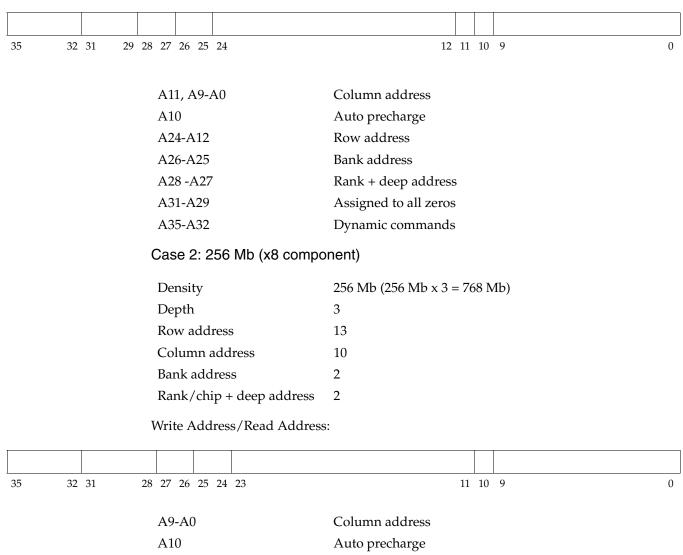

| Deep Memory Configurations             | 58 |

| Components                             | 58 |

| DIMMs                                  | 60 |

| SerDes Clocking Interface              | 61 |

| Feature Summary                        | 62 |

| Supported Features                     | 62 |

| Unsupported Features                   | 62 |

| Architecture                           | 62 |

| Implemented Features                   | 62 |

|                                        |    |

| Hierarchy                                    | 64 |

|----------------------------------------------|----|

| DDR2 Controller Submodules                   | 64 |

| DDR2 SDRAM System and User Interface Signals | 67 |

| DDR2 SDRAM Memory Writes                     | 69 |

| DDR2 SDRAM Memory Reads                      | 71 |

| User to Controller Interface                 | 73 |

| Dynamic Command Request                      | 74 |

| Controller to Physical Layer Interface.      | 75 |

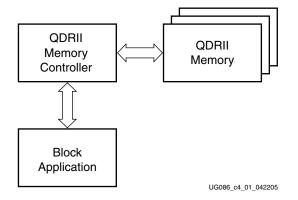

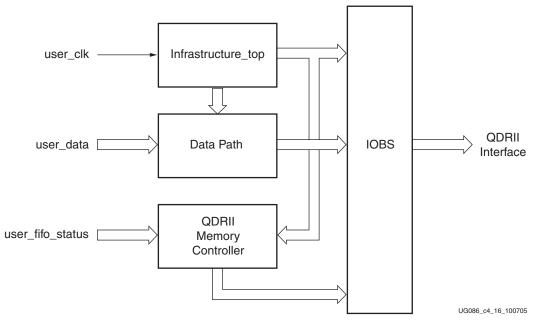

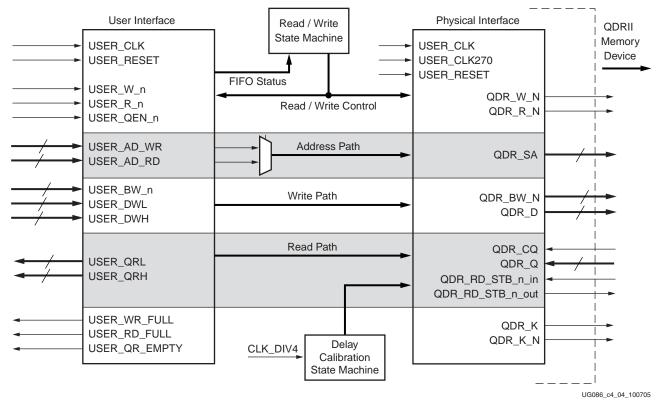

# Chapter 4: Implementing QDRII SRAM Controllers

| Feature Summary                         |    |

|-----------------------------------------|----|

| Supported Features                      | 77 |

| Architecture                            | 77 |

| Interface Model                         | 78 |

| Hierarchy                               | 78 |

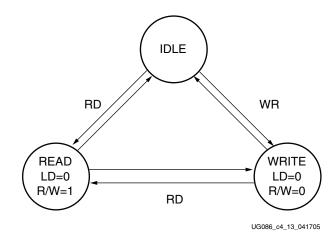

| QDRII Memory Controller Modules         |    |

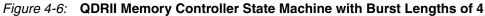

| Controller                              |    |

| Datapath                                | 82 |

| Infrastructure                          |    |

| IOBS                                    | 83 |

| User Interface                          | 83 |

| QDRII Controller User Interface Signals | 84 |

# **Chapter 5: Implementing DDRII SRAM Controllers**

| Feature Summary                         |

|-----------------------------------------|

| Supported Features                      |

| Unsupported Features                    |

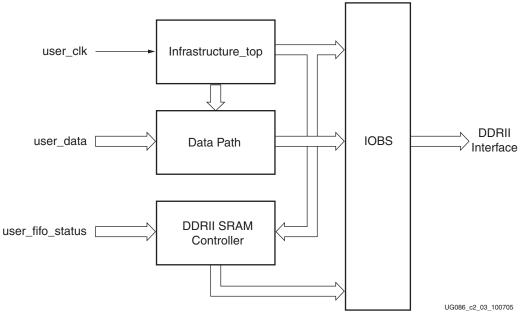

| Architecture                            |

| Interface Model                         |

| Hierarchy                               |

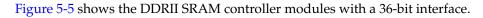

| DDRII SRAM Controller Modules           |

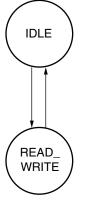

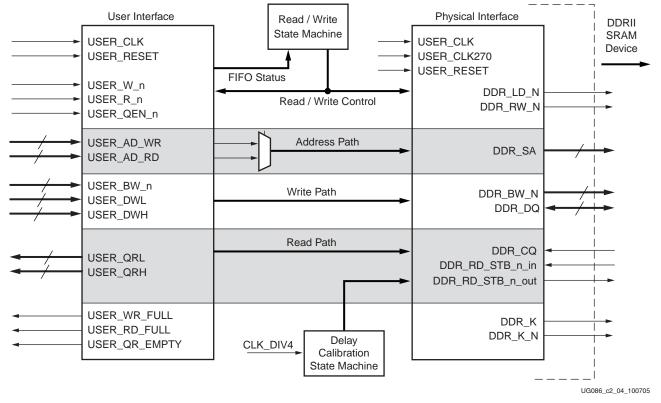

| Controller                              |

| Datapath                                |

| Infrastructure                          |

| IOBS                                    |

| <b>User Interface</b>                   |

| DDRII SRAM Controller Interface Signals |

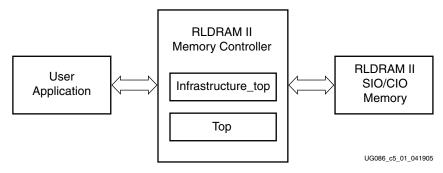

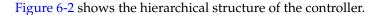

## Chapter 6: Implementing RLDRAM II Controllers

| Feature Summary                                  | 101 |

|--------------------------------------------------|-----|

| Supported Features                               | 101 |

| Unsupported Features                             | 101 |

| Supported RLDRAM II Devices                      | 102 |

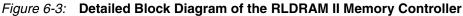

| Architecture                                     | 102 |

| Implemented Features                             | 104 |

| Address Multiplexing                             | 104 |

| CIO/SIO                                          | 104 |

| Data Capture Using the Direct Clocking Technique | 104 |

| Memory Initialization                            | 104 |

|                                                  |     |

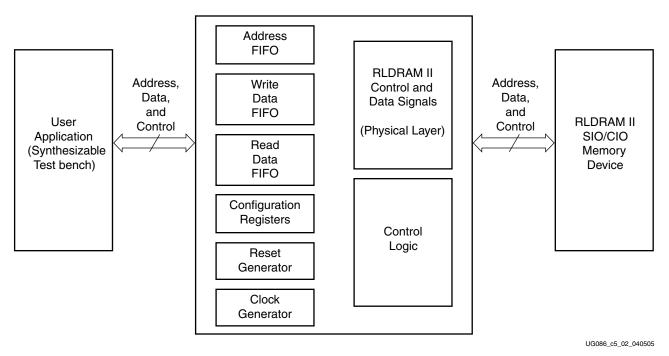

| Block Diagram Description               | 105 |

|-----------------------------------------|-----|

| User Interface                          | 105 |

| Address FIFO                            | 105 |

| Write Data FIFO                         | 106 |

| Read Data FIFO                          | 106 |

| Configuration Registers                 | 107 |

| Clock Generator                         | 107 |

| Reset Generator                         | 107 |

| Control Logic                           | 107 |

| RLDRAM II Control Signal Physical Layer | 108 |

| RLDRAM II Interface Signals             | 108 |

| User Command Interface                  | 111 |

| Write Commands                          | 111 |

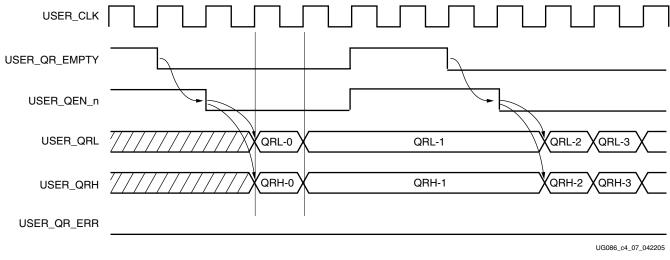

| Read Commands                           | 112 |

| Refresh Commands                        | 113 |

## **SECTION 2: SPARTAN-3 FPGA TO MEMORY INTERFACES**

## **Chapter 7: Implementing DDR SDRAM Controllers**

| Feature Summary 117          |

|------------------------------|

| Controller Architecture      |

| DDR SDRAM Interface 117      |

| Hierarchy                    |

| Controller                   |

| Datapath                     |

| Data Read Controller         |

| Data Read                    |

| Data Write                   |

| Infrastructure               |

| IOBs                         |

| Interface Signals 121        |

| Resource Utilization         |

| DDR SDRAM Initialization 124 |

| DDR SDRAM Write              |

| DDR SDRAM Read 127           |

| Auto_Refresh DDR SDRAM 128   |

| DDR SDRAM Load Mode 128      |

| Constraints                  |

| I/O Clocking Rules           |

| I/O Banking Rules 129        |

| Design Notes                 |

# **Chapter 8: Implementing DDR2 SDRAM Controllers**

| Feature Summary       1         Supported Features       1           | .31<br>.31 |

|----------------------------------------------------------------------|------------|

| Controller Architecture       1         DDR2 SDRAM Interface       1 |            |

| Hierarchy                     |

|-------------------------------|

| Controller                    |

| Datapath                      |

| Data Read Controller 134      |

| Data Read                     |

| Data Write                    |

| Infrastructure                |

| IOBs                          |

| Interface Signals             |

| Resource Utilization          |

| DDR2 SDRAM Initialization 138 |

| DDR2 SDRAM Write 139          |

| DDR2 SDRAM Read 140           |

| Auto_Refresh DDR2 SDRAM 142   |

| DDR2 SDRAM Load Mode 142      |

| Constraints                   |

| I/O Clocking Rules            |

| <b>I/O Banking Rules</b>      |

| <b>Design Notes</b>           |

# Appendix A: Memory Implementation Guidelines

| Generic Memory Interface Guidelines | 145 |

|-------------------------------------|-----|

| Pin Assignments                     | 146 |

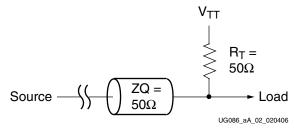

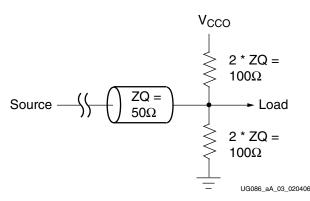

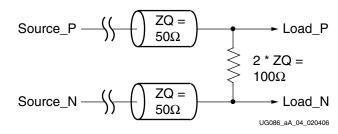

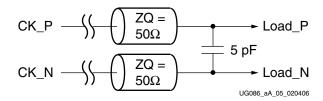

| Termination                         | 146 |

| Memory-Specific Guidelines          | 147 |

| DDR/DDR2 SDRAM                      | 147 |

| Pin Assignments                     | 147 |

| Termination                         | 148 |

| Trace Lengths                       | 148 |

| QDRII SRAM                          | 148 |

| Pin Assignments                     | 148 |

| Termination                         | 149 |

| Trace Lengths                       | 149 |

| RLDRAM II                           | 149 |

| Pin Assignments                     | 149 |

| Termination                         | 149 |

| Trace Lengths                       | 149 |

|                                     |     |

www.xilinx.com

# Preface

# About This Guide

The Memory Interface Generator (MIG) 1.5 tool generates DDRII SRAM, DDR SDRAM, DDR2 SDRAM, QDRII SRAM, and RLDRAM II interfaces for Virtex<sup>TM</sup>-4 FPGAs. It also generates DDR and DDR2 SDRAM interfaces for Spartan<sup>TM</sup>-3 FPGAs and DDR SDRAM interfaces for Spartan-3E FPGAs. The tool takes inputs such as the memory interface type, FPGA family, FPGA devices, frequencies, data width, memory mode register values, and so forth, from the user through a graphical user interface (GUI). The tool generates RTL, SDC, UCF, and document files as output. RTL or EDIF (EDIF is created after running a script file, where the script file is a tool output) files can be integrated with other design files.

## **Guide Contents**

This manual contains the following chapters:

- Chapter 1, "Using the MIG 1.5 Tool," shows how to install and use the MIG 1.5 design tool.

- Section 1: "Virtex-4 FPGA to Memory Interfaces"

- Chapter 2, "Implementing DDR SDRAM Controllers," describes how to implement DDR SDRAM interfaces that the MIG 1.5 tool creates for Virtex-4 FPGAs.

- Chapter 3, "Implementing DDR2 SDRAM Controllers," describes how to implement DDR2 SDRAM interfaces that the MIG 1.5 tool creates for Virtex-4 FPGAs.

- Chapter 4, "Implementing QDRII SRAM Controllers," describes how to implement QDRII SRAM interfaces that the MIG 1.5 tool creates for Virtex-4 FPGAs.

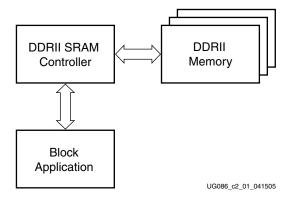

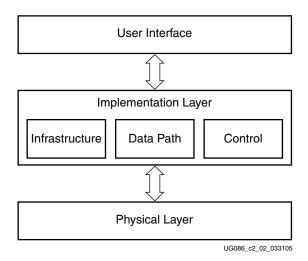

- Chapter 5, "Implementing DDRII SRAM Controllers," describes how to implement DDRII SRAM interfaces that the MIG 1.5 tool creates for Virtex-4 FPGAs.

- Chapter 6, "Implementing RLDRAM II Controllers," describes how to implement RLDRAM II interfaces that the MIG 1.5 tool creates for Virtex-4 FPGAs.

- Section 2: "Spartan-3 FPGA to Memory Interfaces"

- Chapter 7, "Implementing DDR SDRAM Controllers," describes how to implement DDR SDRAM interfaces that the MIG 1.5 tool creates for Spartan-3 FPGAs.

- Chapter 8, "Implementing DDR2 SDRAM Controllers," describes how to implement DDR2 SDRAM interfaces that the MIG 1.5 tool creates for Spartan-3 FPGAs.

• Appendix A, "Memory Implementation Guidelines," provides helpful rules for reference designs.

## References

The following documents provide supplementary material useful with this user guide.

- 1. Samsung Data Sheet k7i321884m\_R04 http://www.samsung.com/Products/Semiconductor/SRAM/SyncSRAM/DDRII\_CIO\_SIO/ 36Mbit/K7I321884M/K7I321884M.htm

- 2. Micron Data Sheet MT47H16M16FG-37E http://www.micron.com/products/dram/ddr2sdram/partlist.aspx

- 3. Samsung Data Sheet k7r323684m <u>http://www.samsung.com/Products/Semiconductor/common/product\_list.aspx?family\_cd</u> <u>=SRM020302</u>

- 4. Micron Data Sheet MT49H16M18FM-25 http://www.micron.com/products/dram/rldram/part.aspx?part=MT49H16M18FM-25

- 5. Micron Data Sheet MT46V16M16FG-5B http://www.micron.com/products/dram/ddrsdram/partlist.aspx

- 6. <u>UG070</u>, Virtex-4 User Guide

- 7. <u>UG072</u>, Virtex-4 PCB Designer's Guide

- 8. UG079, Virtex-4 ML461 Memory Interfaces Development Board User Guide

- 9. XAPP645, Single Error Correction and Double Error Detection

- 10. XAPP701, Memory Interfaces Data Capture Using Direct Clocking Technique

- 11. XAPP702, DDR-2 Controller Using Virtex-4 Devices

- 12. XAPP703, QDR II SRAM Interface

- 13. XAPP709, DDR SDRAM Controller Using Virtex-4 FPGA Devices

- 14. XAPP710, Synthesizable CIO DDR RLDRAM II Controller for Virtex-4 FPGAs

- 15. <u>XAPP721</u>, High-Performance DDR2 SDRAM Memory Interface Data Capture Using ISERDES and OSERDES

- 16. XAPP768c: Interfacing Spartan-3 Devices With 166 MHz or 333 Mb/s DDR SDRAM Memories (available under click license)

- 17. DS099, Spartan-3 FPGA Family: Complete Data Sheet

- 18. DS312, Spartan-3E FPGA Family: Complete Data Sheet

## **Additional Resources**

To search the database of silicon and software questions and answers, or to create a technical support case in WebCase, see the Xilinx website at: http://www.xilinx.com/support.

# **Typographical Conventions**

This document uses the following typographical conventions. An example illustrates each convention.

| Convention      | Meaning or Use                  | Example                                                           |

|-----------------|---------------------------------|-------------------------------------------------------------------|

| Italic font     | References to other documents   | See the Virtex-4 <i>Configuration Guide</i> for more information. |

|                 | Emphasis in text                | The address (F) is asserted <i>after</i> clock event 2.           |

| Underlined Text | Indicates a link to a web page. | http://www.xilinx.com/virtex4                                     |

# Chapter 1

# Using the MIG 1.5 Tool

The MIG 1.5 tool is used to generate memory interfaces for Xilinx FPGAs. This document describes the user interface and various options in the MIG 1.5 tool. The output files are also described.

| FPGA devices and parts     Type       Image: state sta                                                                                                                                                                                                                                                                                     | Module name mem_interface_top Number of controllers 1  Select controller 0 | Select banks                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Memory devices and parts Type<br>DDR2 SDRAM<br>Components<br>- MT47H256M4BT-37E<br>- MT47H256M4BT-37E<br>- MT47H256M4BT-3<br>- MT47H128M8BT-3<br>- MT47H128M8BT-3<br>- MT47H128M8BT-3<br>- MT47H128M8BT-3<br>- MT47H128M8BT-3<br>- MT47H128M4BT-3<br>- MT47H128M4<br>- MT47H128M4<br>- MT47H128M4<br>- | Use clock capable IOs for<br>strobes/read cloocks                          | A<br>B<br>S<br>10<br>0<br>9<br>C<br>4<br>A<br>D<br>S<br>8<br>2<br>7<br>Feserve pins |

| Verify my ucf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Restore                                                                    | Generate ML461 board                                                                |

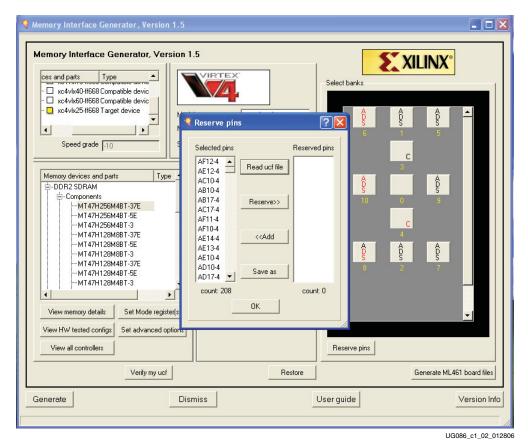

Figure 1-1 is a screen shot of the MIG 1.5 GUI.

UG086\_c1\_01\_02806

Figure 1-1: MIG 1.5 GUI

# MIG 1.5 Tool Changes from MIG 1.4

The new features of the MIG 1.5 design tool are summarized in this section:

- GUI Changes

- Clock capable I/Os for strobes and read clocks for direct clocking method

- Programmable Mode Register options

- Verify my UCF feature

- Programmable pin allocation limit for selected banks

- Reserved Pin list

- Save option to a file

- DDR2 SDRAM Direct clocking (Virtex-4 interfaces) support:

- Synplicity Synplify 8.2 support

- SO DIMM support

- Modified Read Enable implementation

- ISE 8.1.01i support (all MIG 1.5 designs support this ISE version)

- DDR2 SDRAM SerDes clocking (Virtex-4 interfaces) support

- DDR SDRAM for Virtex-4 interfaces:

- Synplicity Synplify 8.2 support

- CL = 2, 2.5, and 4

- BL = 2 and 8

- SO DIMMs

- Support for more memory devices

- Modified Read Enable implementation

- DDR SDRAM for Spartan-3/Spartan-3E devices:

- ◆ CL = 2 and 2.5

- BL = 2 and 8

- Synplicity Synplify 8.2

- Registered DIMMs

- Support for more memory devices

- DDR2 SDRAM for Spartan-3 devices:

- Synplicity Synplify 8.2

- ♦ BL = 8

- Registered DIMMs

- RLDRAM II:

- Synplicity Synplify 8.2 support

- QDRII and DDR2 SRAMs:

- Synplicity Synplify 8.2 support

- Supports skip wait 200 µs delay for Verilog simulations. This feature is not supported for VHDL cases.

- To skip 200 µs initial delay, users should use the following run-time options for Verilog in ModelSim.

• For DDR SDRAM for Virtex-4 interfaces:

vlog +define+simulation modulename\_ddr\_controller\_0.v

Where:

- simulation is the parameter.

- modulename\_ddr\_controller.v is the file with the parameter 'simulation'. The file modulename\_ddr\_controller.v must be present in the sim folder.

- For DDR2 SDRAM for Virtex-4 interfaces:

vlog +define+simulation modulename\_ddr2\_controller\_0.v

• For Spartan-3 interfaces:

vlog +define+simulation modulename\_ddr\_infrastructure\_top.v

## **Tool Features**

The key features of the MIG 1.5 design tool are listed below:

- Supported memory types for Virtex<sup>™</sup>-4 interfaces:

- DDR2 SDRAM components, and registered and unbuffered DIMMs. The DDR2 controller supports deep memory depths from one to four.

- DDR SDRAM components, and registered and unbuffered DIMMs

- QDRII and DDRII SRAM

- RLDRAM II CIO and SIO memories

- Supported memory types for Spartan-3 interfaces:

- DDR SDRAM components, registered and unbuffered DIMMs

- DDR2 SDRAM components, registered and unbuffered DIMMs

- Supported memory types for Spartan-3E interfaces:

- DDR SDRAM components, registered and unbuffered DIMMs

- Supported Virtex-4 Synthesis tools:

- XST and Synplicity Synplify 8.2

- Supported Spartan-3 Synthesis tools:

- Synplicity, XST, and Precision 2005B for the DDR SDRAM Local clocking type

- Supported Spartan-3E Synthesis tools:

- XST and Synplicity Synplify 8.2

- Supported components:

- For DDR2 SDRAM, RLDRAM II SDRAM, and QDRII and DDRII SRAMs, most of the popular components and DIMMs are supported.

- Some DDR SDRAM components and DIMMs are supported.

- An equivalent component can be found for any unsupported component.

- All currently available Virtex-4, Spartan-3, and Spartan-3E FPGAs are supported.

- Direct and SerDes clocking techniques for data capture for Virtex-4 interfaces.

Direct clocking is explained in XAPP701 [Ref 10]. With this technique, it is not necessary to use clock-capable I/Os for strobes or read clocks. SerDes clocking is explained in XAPP721 [Ref 15]. The use of clock-capable I/Os for strobes and read

clocks is recommended for maximum flexibility with higher frequency designs (200 MHz and above).

- Local clocking technique for data capture for all Spartan-3 and Spartan-3E interfaces. The data capture technique using Spartan-3 FPGAs is explained in XAPP768c [Ref 16].

- Both VHDL and Verilog are supported.

- Variable data widths in multiples of 8 up to 144 bits.

The actual width depends upon the selected component. For a 16-bit wide component, data widths of 16, 32, 48, and 64 are supported. For an 8-bit wide component, data widths of 8, 16, 24, 32, 40, 48, 56, 64, and 72 are supported.

For DDR2 SDRAM, most of the components support up to a 144-bit data width.

- User-selectable banks for address, data, system control, and system clock signals.

For QDRII and RLDRAM II memories, the user selects the data banks for reads and RLD (SIO) writes separately.

- Different banks are supported with different I/O standards.

The MIG 1.5 tool uses different banks for groups of signals whose I/O standards are different. If the I/O voltages for different groups (such as address, data, and system control) are different, the user must ensure enough banks are selected for the MIG 1.5 tool to use. If insufficient banks are selected, the tool cannot allocate pins.

- Various configurations are supported through changing bits in the Mode and Extended Mode Registers.

- All fields not highlighted in the GUI either are not supported or are not relevant for that type of memory.

- Only one type of component is supported per interface.

Users cannot mix different components to create an interface.

• Multiple DDR2 interfaces.

Users can select up to eight controllers.

• Pin compatibility.

Users can select multiple devices using the same package to generate compatible pinouts.

• Supported Operating Systems:

The MIG tool is available only on these ISE platforms:

- Windows XP Home

- Professional

## **Xilinx Design Tools Version Requirements**

To use this IP update, ISE 8.1i with Service Pack 1 (8.1.01i) must be installed. ISE 8.1i service packs can be obtained from the Download Center at: http://www.xilinx.com/xlnx/xil\_sw\_updates\_home.jsp

The MIG 1.5 tool requires ISE 8.1i IP Update 1 or later. If not already installed, IP Update 1 is automatically installed by the Updates Installer before the ISE 8.1i MiG 1.5 IP Update is installed. See <u>Xilinx Answer 21938</u> for issues related to ISE 8.1i IP Update 1. Acrobat Reader Version 5 or later must be installed. The latest Acrobat software can be downloaded from the Adobe website at: <u>http://www.adobe.com/products/acrobat/readstep.html</u>.

## Installation

The MIG tool is accessible via the Xilinx CORE Generator<sup>™</sup> System, starting with MIG version 1.3.

There are two ways to install the MIG 1.5 toolset.

#### Method 1

Users who are behind a firewall and do not know their proxy settings use this method.

- Users must verify that they have the latest ISE 8.1i Service Pack and the latest IP Update from the Download Center at: <u>http://www.xilinx.com/xlnx/xil\_sw\_updates\_home.jsp</u>. For ISE, users receive a proper installer. For the IP Update, users receive a ZIP file to unzip into the 8.1i installation. For the MIG 1.5 tool, ISE sp1 and the latest IP Update are required.

- 2. Users who are not registered at the Memory Corner can register at: <u>http://www.xilinx.com/xlnx/xil\_entry2.jsp?sMode=login&group=memory\_customers</u>

- 3. The MIG 1.5 tool is downloaded from: <u>http://www.xilinx.com/support/software/memory/protected/ise\_81i\_mig15.zip</u> (Enter the xilinx.com account name and password when prompted.)

- 4. This ZIP file is unzipped into the root ISE 8.1i installation (C:\Xilinx by default).

#### Method 2

- 1. The CORE Generator system is launched by selecting **Start -> Xilinx ISE 8.1i -> Accessories -> CORE Generator** from the Windows Start menu.

- 2. When the CORE Generator GUI opens, select **Tools -> Updates Installer**.

- 3. The CORE Generator system displays a dialog box with a warning indicating that it will exit after the installation is complete. Click the **Accept** button.

- 4. The CORE Generator system connects to www.xilinx.com and might ask for the user xilinx.com User ID and password. Users who are behind a firewall might have to enter their appropriate proxy settings.

- 5. The IP Updates Installer dialog box opens and displays a panel listing the available updates.

- 6. Select ISE 8.1i MIG 1.5 and click the **Install Selected** button. The program might indicate that other installs are required. These informational messages can be accepted. The CORE Generator system downloads and installs the requested products and exits.

*Note:* The installation process must not be interrupted. During this process, various pop-up messages must be accepted. If other windows are open, the pop-ups might be hidden behind them.

### Getting Started

These steps launch the MIG tool:

- 1. The CORE Generator system is launched by selecting **Start -> Xilinx ISE 8.1i -> Accessories -> CORE Generator**.

- 2. Create a CORE Generator project.

- 3. The Xilinx part must be correctly set because it cannot be changed inside the MIG tool. Virtex-4 and Spartan-3/Spartan-3E devices are supported. Select the part via the part's Project Options menu in the CORE Generator system. The generation tab is used to

select between Verilog or VHDL by "design entry" under "flow". The "flow settings" "vendor" are chosen appropriately.

- 4. Remember the location of the CORE Generator project directory. The "View by Function" tab to the left shows the available cores organized into folders.

- 5. The MIG tool is launched by selecting **Memories & Storage Elements -> MiG -> Memory Interface Generator**.

- 6. The name of the module to be generated is entered in the Module Name text box. Click **Generate** to generate the module files in a directory with the same name as the module name in the CORE Generator project directory.

- 7. After generation, the GUI is closed by selecting the **Dismiss** button.

The "Generated IP" tab to the left lists the generated modules. The generated <code>ise\_flow.bat</code> script or the ISE GUI is used to manually add the generated HDL files to a project.

## **User Options**

This section summarizes the selectable parameters accessible through the GUI.

#### Part Selection – Target and Compatible Part

The CORE Generator system selects the part before invoking the MIG tool. The compatible part can be selected from the MIG tool.

#### **Clocking Type**

The Clocking Type browsing window selects the desired clocking type for the design. DDR2 SDRAM supports all three types of clocking: *direct* and *SerDes* clocking types (for Virtex-4 devices) and *local* clocking types (for Spartan-3 and Spartan-3E devices). The MIG 1.5 tool enables the corresponding clocking types when memory component is selected.

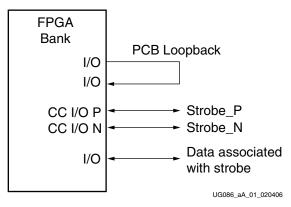

### Use CC (for Direct Clocking)

This option selects clock capable I/Os for strobes and read clocks. Only Virtex-4 Direct clocking designs support this feature.

#### Frequency

The frequency bar selects the desired interface frequency. The desired frequency is limited by factors such as speed grade of the device, the selected memory part, and the design.

The MIG 1.5 tool does not limit the frequency based on CAS latency. For example, DDR SDRAM memory supports a maximum frequency of 167 MHz for CL = 2, but the MIG 1.5 tool can go up to 200 MHz for CL = 2. The user must select the frequency according to the CAS latency.

For Spartan-3E designs, the tool-generated frequency is more than what the stepping 0 devices support. Users must use Spartan-3E stepping 1 devices for frequencies from 90 MHz to 133 MHz.

### Memory

The supported memory components and DIMMs are displayed in this section. In the current tool version, most DDR and DDR2 SDRAM, QDRII and DDR2 SRAM, and RLDRAM II devices are supported. The MIG 1.5 tool automatically identifies the different memory parameters based on the user's selection. The different memory parameters, such as data bits per strobe and address widths, are displayed when the user clicks on the **Memory details** button.

## Data Width and Depth

The user selects the required data width through this menu. The data width selection is overridden by the DIMM selection. In other words, if the user selects a DIMM module, the data width is automatically determined by the width of the DIMM module. The supported data widths depend upon the memory device as well. For instance, it is not possible to create a 72-bit interface using 16-bit wide components. Currently, interfaces cannot consist of mixes of different components.

Depth is relevant only for DDR2 SDRAM devices. The DDR2 SDRAM controller generates different depths. Also, signal integrity is a key concern in deep-memory designs. Users must verify the signal integrity of their boards.

### **View Memory Details**

This option opens a pop-up window to view the details of the selected memory.

## View HW Tested Configs

This option displays the hardware tested configurations for that design.

## Set Mode Register(s)

This option allows users to select various memory options from the Mode and Extended Mode Registers, such as CAS latency and burst length.

### Set Advanced Options

This button has different functionality for Spartan-3 designs and Virtex-4 designs.

For Virtex-4 designs, this button can restrict the number of pins to be allocated in a bank. On clicking this button, a table pops up with the bank number, number of pins in that bank, and a column to select number of pins to allocate in that bank. By default, the tool allocates all the pins for the interface. This feature is implemented only for Virtex-4 designs.

For Spartan-3 designs, the user clicks on this button to select the number of write pipelines in the design. The MIG 1.5 tool supports 0 to 4 pipelines, where the default is 4 pipelines. When the user selects 0 to 3 pipelines, the remaining pipe stages are to be included in the user interface. For example, if the user selects 0 pipelines from the tool, the write data should be passed through a 4-stage pipeline before it is given to the controller user interface.

#### **View All Controllers**

This option shows all the selected parameters for all controllers, either a single controller or multiple controllers.

### **Design Parameters**

This selection allows the user to change the values of the Mode and Extended Mode Registers and other design parameters. This option changes depending upon the selected memory type. The specific memory data sheet contains detailed explanations of the different parameters in the Mode and Extended Mode Registers.

The MIG 1.5 tool supports the direct and SerDes clocking methods for Virtex-4 FPGAs. Direct clocking is explained in detail in XAPP701 [Ref 10]. This method does not require the strobe/read clock to be in a clock capable (\_CC) input/output buffer (IOB). Hence, the tool can select any IOB for strobe/read clocks. SerDes clocking is explained in detail in XAPP721 [Ref 15]. Memory interfaces with Spartan-3 FPGAs use the local clocking method.

VHDL and Verilog are supported for all indicated memory interfaces.

The user can choose to have the digital clock manager (DCM) within the generated design or have all the required clocks as inputs to the design. This option is the function of the DCM check box. This option is available for DDR2 SDRAM and DDR SDRAM Spartan-3 designs.

The error correction code (ECC) check box enables generation of ECC along with the code. ECC is supported in the following configurations:

- 1. 32-bit DDR2 SDRAM with 7 bits of ECC. This option generates a 40-bit design.

- 2. 64-bit DDR2 SDRAM with 8-bit ECC. This option generates a 72-bit design.

- 3. 128-bit DDR2 SDRAM with 16-bit ECC. This option generates a 144-bit design.

Only 40-bit, 72-bit, and 144-bit widths enable the ECC check box. ECC can impact the timing of the design.

The user can chose to have a synthesizable test bench by checking the "test bench" box.

### Add Test Bench

When this box is checked, the design is generated along with test bench. The test bench drives the read and write commands, compares the read data, and generates an error signal if the read data does not match the write data.

#### Use DCM

This option allows the user to generate the design with or without DCM in the design. If the design is generated with the "Use DCM" option enabled, the required clocks are generated from the DCM within the design only, and SYS\_CLK and SYS\_CLKb are to be provided as inputs to the design. If this option is disabled, users must provide the required clocks as inputs.

### **Edit Signal Names**

When this box is checked, before the design is generated, a table is presented with all the top-level signal names. Users can modify the signal names from this table. The tool outputs the design with the modified signal names.

#### **Output Directory**

The desired output directory is selected here. Before clicking the **Generate** button, the user has to select the banks to be used for the data, address, and system control signals (see "Select Banks").

#### Module Name

The MIG 1.5 tool accepts any name that is prepended to all module and RTL file names of the design.

#### Select Banks

On the right side of the GUI, an approximate figure appears with the FPGA I/O banks (see Figure 1-2). The user selects the banks to be used for address, data, system control, and system clock signals by right-clicking on the I/O banks in the figure.

The user selects both read and write data banks for QDRII and RLDRAM II SIO devices.

| 🍕 Memory Interface Generator , Version 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Memory Interface Generator, Version 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| Memory devices and parts       Type         G: DDR2 SDRAM       Type         G: DDR2 SDRAM       Use clock capable IOs for strobes/read clocks         Memory devices and parts       Memory devices and parts         Memory devices and parts       Type         Memory devices and parts       Set Mode register(s)         View all controllers       Set advanced options         View all controllers       System |        |

| Verify my ucf     Restore     Generate ML461 board fr       Generate     Dismiss     User guide     Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| UG086 c1 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 012806 |

Figure 1-2: Bank Selection

www.xilinx.com

### **Reserve Pins**

The user can reserve some FPGA pins from the selected banks by clicking on the **Reserve pins** button. There is also a provision to read the list of reserved pins from a UCF file using the **read ucf file** button. Any LOC constraints in the UCF file are added to the reserved pin list.

A sample UCF file format looks like:

NET "cntrl0\_DDR\_DQ[3]" LOC = AJ4; NET "cntrl0\_DDR\_DQ[2]" LOC = AJ3; NET "cntrl0\_DDR\_DQS[1]" LOC = AH3;

Figure 1-3 shows the window that appears when the **Reserve pins** button is clicked. The user selects the required pins from the Selected pins list and clicks on the **Reserve** button to reserve the pins. To remove some of the pins from the reserved list, the user selects the pins from the Reserved pins list and clicks on the **Add** button, which moves the pins back to the Selected pins list. The **Save as** button allows the user to save the reserved pins into a user-defined file. When the user clicks on the **Save as** button, a browsing window is opened to select the folder and assign a file name that contains the reserved pins. When the user clicks on the **Read ucf file** button, a browsing window is opened to select the UCF file. All the LOC constraints from the UCF file are considered for the Reserve pins.

Figure 1-3: Reserve Pins

## Verify my ucf

This feature allows the user to test whether a given UCF file containing signal names and their corresponding pin names comply with the pin allocation rules for the selected options from the tool. The user first inputs all the standard information, such as part/package, banks for address, and data. All the user inputs that are required for generating a UCF/design are required for verification. The verification is performed only for the I/O signals required for the memory design (in other words, other user signals in the UCF are ignored).

This feature verifies:

- Whether all the dq bits are allocated in the selected banks.

- The associated groups are allocated in the same bank. For example dq bits corresponding to a dqs are treated as a group. All the signals within the same group should be in the same bank.

- The I/O banking rules. In a given bank, all the signals should have the I/O standard with the same I/O voltage.

- The signal names

- The selected data width. For example if the data width is 32 bits and the reference UCF has more bits, the tool verifies the required bits and ignores the excess data.

- The uniqueness of the pins. It flags an error if two signals are allocated to the same pin or vice versa, or if the same signal is allocated to more than one pin.

- The strobe signals are allocated to the CC pins when the CC pins option is enabled.

- The signals are allocated within the selected banks.

#### Error Messages

This section describes the different error messages that can be generated when verifying the UCF file.

The reference UCF must follow the MIG naming conventions (refer to the UCF files generated by the MIG tool).

The *Edit signal names* option is not supported for the Verify my ucf mode.

For example, DDR2 SDRAM controller 0 should have cntrl0\_DDR2\_DQ[0] for data bits, and RLDRAM controller 0 should have cntrl0\_RLD2\_DQ[0] for data bits.

1. Uniqueness

If two signals are allocated to the same pins in the reference UCF, an error message is listed in the directed file with a user-assigned name.

The error message format is "<signal\_name1> and <signal\_name2> are allocated to the same pins."

For example, if cntrl0\_DDR2\_DQ[0] and cntrl0\_DDR2\_DQS[0] are allocated to the same pin, such as:

NET "cntrl0\_DDR2\_DQ[0]" LOC = "D12" ; NET "cntrl0\_DDR2\_DQS[0]" LOC = "D12" ;

#### Then the following error message is printed:

ERROR: cntrl0\_DDR2\_DQ[0] and cntrl0\_DDR2\_DQS[0] are allocated to the same pins.

Pins are not unique.

2. Association

Signals in the same group (for example, assume DQS[0] and DQ[0:7] form the same group) should go to the same bank, otherwise an error message is printed in the same user directed file.

The error message format is "<signal\_name1> and <signal\_name2> are not allocated in the same banks."

For example:

| NET | "cntrl0_DDR2_DQ[0]" | LOC = "D12" ; #bank 6        |

|-----|---------------------|------------------------------|

| NET | "cntrl0_DDR2_DQ[1]" | LOC = "C12" ; #bank 6        |

| NET | "cntrl0_DDR2_DQ[2]" | LOC = "B10" ; <b>#bank 6</b> |

| NET | "cntrl0_DDR2_DQ[3]" | LOC = "C10" ; <b>#bank 7</b> |

Assume cntrl0\_DDR2\_DQ[3] and cntrl0\_DDR2\_DQ[2] are allocated to pins of different banks, such as bank 7 and bank 6, respectively. The following error messages are printed:

ERROR: cntrl0\_DDR2\_DQ[0](6) and cntrl0\_DDR2\_DQ[3](7) are not allocated in the same banks ERROR: cntrl0\_DDR2\_DQ[1](6) and cntrl0\_DDR2\_DQ[3](7) are not allocated in the same banks ERROR: cntrl0\_DDR2\_DQ[2](6) and cntrl0\_DDR2\_DQ[3](7) are not allocated in the same banks

These types of error messages are printed for each pair of signals of same group, but are allocated to different banks.

3. I/O Voltage

The signals allocated to the same bank should have the same I/O voltage. If not, an error message is printed in the same user directed file.

The error message format is "<signal\_name1> and <signal\_name2> have different I/O Voltages."

For example, cntrl0\_DDR2\_DQ[2] and cntrl0\_DDR2\_DQ[4] are allocated to the same bank (expected because they are from the same group). If these pins have different I/O voltages, the following error message is printed:

```

ERROR: cntrl0_DDR2_DQ[2] and cntrl0_DDR2_DQ[4] have different I/O Voltages.

```

4. Clock Capable I/Os for strobes/read clock

Check for CC pins if Use CC for direct clocking is clicked. In this case, the strobe/read\_clock signals should be allocated to the CC pins only. If not, an error message is displayed.

The error message format is "<signal\_name> should be allocated to the CC Pins."

For example, cntrl0\_DDR2\_DQS[0] is a strobe. Assume it is allocated to the K12 pin, which is not a clock capable I/O pin. The following error message is printed:

ERROR: cntrl0\_DDR2\_DQS[0 should be allocated to the CC Pins.

5. Absence of signals

If one or more signal-pin pair is missing and/or commented in the given UCF file against the selected inputs, the verification result indicates the absence of those signal-pin pairs as a warning.

The warning message format is" <signal\_name> is forbidden in the given UCF File against the selected inputs."

For example, assume the reference UCF file has 8 bits DQ[0:7] and the selected data width in the GUI is 16 bits. While checking, the MIG tool verifies only eight bits, and reports the other bits as forbidden as follows:

WARNING : cntrl0\_DDR2\_DQ[8] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[9] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[10] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[11] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[12] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[13] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[14] is forbidden in the given UCF File against the selected inputs. WARNING : cntrl0\_DDR2\_DQ[15] is forbidden in the given UCF File against the selected inputs.

6. Bank selection

If one or more banks are not selected and one or more pins from that (those) bank(s) is (are) used for some purpose, an error message is printed.

The error message format is "<signal\_name> (<signal\_group>) is not allowed to be allocated in Bank (<bank\_number>) against the selected inputs."

For example:

NET "cntrl0\_DDR2\_DQS[0]" LOC = "D12" ;#bank 6

belonging to bank 6. The following error message is printed:

Bank 6 is not selected for Data (as cntrl0\_DDR2\_DQS[0] from Data). Assume that cntrl0\_DDR2\_DQS[0], which belongs to the strobe group is allocated to a pin

ERROR: cntrl0\_DDR2\_DQS[0] (*strobe*) is not allowed to be allocated in bank 6 against the selected inputs.

## Generate SL361/ML461 Board Files

The **Generate SL361/ML461 board files** button allows users to generate the hardware board files for the selected boards. Most of the designs that the MIG 1.5 tool supports are hardware tested. The board files generated out of the tool have the bit files. The bit files can be programmed onto the reference boards for demonstration purposes.

#### Restore

Users click on the **Restore** button to restore the default options.

### Generate

After selecting all the design options, the user clicks on the **Generate** button to generate the design files. The MIG 1.5 tool generates an output directory with a name and location specified by the user. The following files and directories are created under the top-level directory:

• usr

This directory contains the outputs generated by the MIG 1.5 tool.

• datasheet

This is a brief data sheet of the generated interface.

• log

This is a log file.

The usr directory contains the following subdirectories:

• docs

Any relevant documents, such as application notes and timing analysis spreadsheets, are in this directory.

• par

Contains the UCF file with constraints for the design. A script file called ise\_flow is generated.

The user can double-click on the ise\_flow script file to run the design through synthesis, build, map, and par. This script file sets all the required options.

• rtl

Contains all the RTL files (Verilog and VHDL) for the generated design.

• synth

Contains the SDC file for Synplify pro with the design constraints. This folder also has the script files, which set various tool options. There is also a project file, through which the RTL files are passed for synthesis.

• sim

Contains the sample files required for simulation. Users modify the test bench files according to their designs.

#### Dismiss

When the user clicks on the **Dismiss** button, the tool is closed.

#### **User Guide**

When the user clicks on this button, the user guide is opened in PDF format.

### Version Info

This option shows the MIG release version, the date of release, the simulator version, the synthesis tool versions, and the ISE version.

# Section 1: Virtex-4 FPGA to Memory Interfaces

"Implementing DDR SDRAM Controllers" "Implementing DDR2 SDRAM Controllers" "Implementing QDRII SRAM Controllers" "Implementing DDRII SRAM Controllers" "Implementing RLDRAM II Controllers"

# Chapter 2

# Implementing DDR SDRAM Controllers

This chapter describes how to implement DDR SDRAM interfaces for Virtex-4 FPGAs created with the MIG 1.5 design tool. This design is based on XAPP701 [Ref 10] and XAPP709 [Ref 13].

## **Feature Summary**

The DDR SDRAM controller design supports:

- Burst lengths of two, four, and eight

- Sequential and interleaved burst types

- CAS latencies of 2, 2.5, and 3

- Precharge based on the row to be accessed or the user input

- Registered DIMMs

- Different memories (density/speed)

- Auto refresh

- VHDL and Verilog

The supported features are described in more detail in "Architecture."

## Architecture

#### **Interface Model**

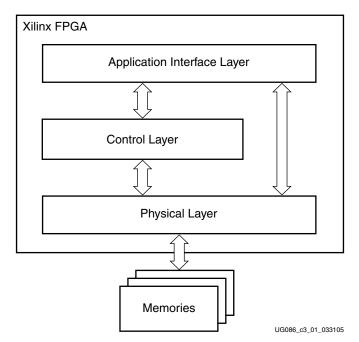

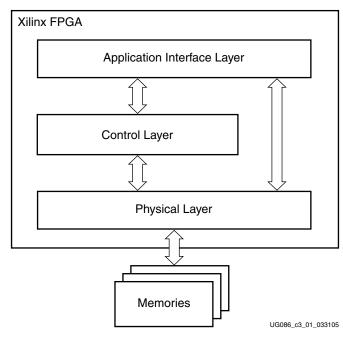

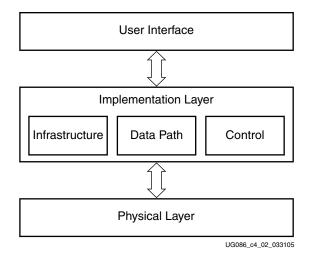

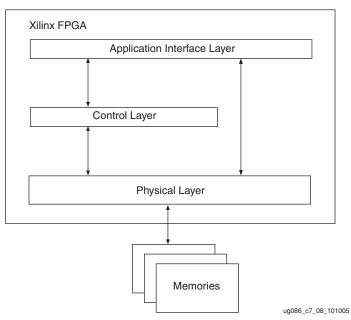

DDR SDRAM interfaces are source-synchronous and double data rate. They transfer data on both edges of the clock cycle. A memory interface can be modularly represented as shown in Figure 2-1. A modular interface has many advantages. It allows designs to be ported easily and also makes it possible to share parts of the design across different types of memory interfaces.

Figure 2-1: Modular Memory Interface Representation

## Implemented Features

This section provides details on the supported features of the DDR SDRAM controller. Based on user selection, the tool generates a parameter file, which is used to program various features of the memory and to generate the control signals accordingly.

The parameter file provides the settings for burst length, CAS latency, sequential or interleaved addressing, number of row address bits, number of column address bits, bank address, and the timing parameters based on the frequency and the speed grade selected by the user in the GUI tool. The controller takes these parameters directly.

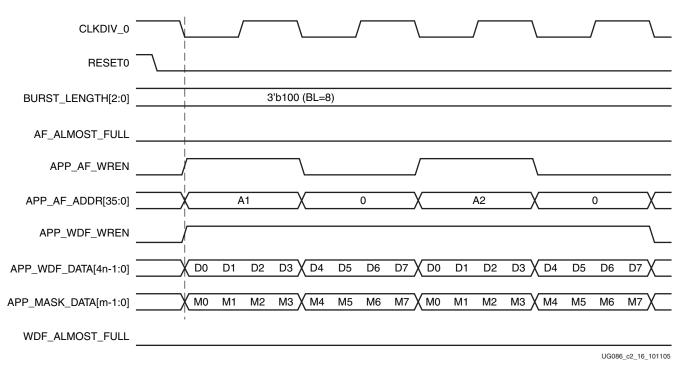

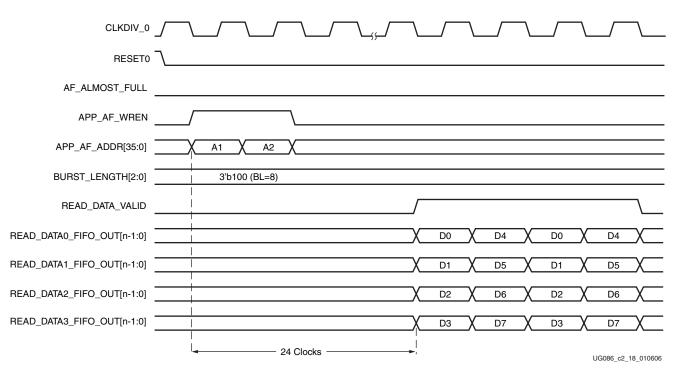

The user can also issue a command through the FIFOs (user\_interface). The user address (i.e., APP\_AF\_ADDR that is written into the FIFO as shown in Figure 2-6) is decoded in a sequence. The total width is 32 bits consisting of column address (least-significant), row address, bank address, chip address, command to be issued, and whether the row to be accessed is same as that of the previous row. The controller takes the row and column address bits based on the selected component. Table 2-1 lists the commands that the user can issue through the User interface.

| Command            | APP_AF_ADDR[34:32] |

|--------------------|--------------------|

| READ               | 101                |

| WRITE              | 100                |

| LOAD MODE REGISTER | 000                |

| REFRESH            | 001                |

| PRECHARGE          | 010                |

Table 2-1: User Commands

#### **Burst Length**

Bits M0:M3 of the Mode Register define the burst length and burst type. Read and write accesses to the DDR SDRAM are burst-oriented. The burst length is programmable to either 2, 4, or 8 through the GUI tool. It determines the maximum number of column locations accessed for a given READ or WRITE command.

The DDR SDRAM ddr\_controller module implements a burst length that is programmed via the generated parameter file based on the user selection from the tool.

#### CAS Latency

Bits M4:M6 of the Mode Register define the CAS latency (CL). CL is the delay in clock cycles between the registration of a READ command and the availability of the first bit of output data. CL can be set to 2, 2.5, or 3 clocks through the GUI tool from the parameter file. CAS latency is implemented in the ddr\_controller module.

During read data operations, the generation of the read\_en signal varies according to the CL in the ddr\_controller module.

#### **Registered DIMMs**

DDR SDRAM supports registered DIMMs. This feature is implemented in the ddr\_controller module. For registered DIMMs, the READ and WRITE commands have one additional clock latency than unbuffered DIMMs. Also for registered DIMMs, the controller delays the data and the strobe by one clock because the command has one clock latency due to the register in the DIMM.

#### Precharge

The PRECHARGE command is issued before the next read or write is issued for another row or bank, but not if the read or write is in the same row and bank. The AUTO PRECHARGE command via the A10 column bit is not supported because it can cause the controller to get into an unexpected state.

#### Auto Refresh

The DDR SDRAM controller issues AUTO REFRESH commands at specified intervals for the memory to refresh the charge required to retain the data in the memory. The user can also issue a REFRESH command through the user interface by setting bits 34, 33, and 32 of the app\_af\_addr signal in the user\_interface module to 3'b001. If the REFRESH command is issued within a read or a write burst, the controller issues the REFRESH command and then returns to the ongoing READ or WRITE command.

#### Different Memories (Density/Speed)

This feature supports different memory components and DIMMs. The component densities can vary from 128 Mb to 1 Gb, and the DIMM densities can vary from 128 MB to 1 GB. To support this feature, the design can decode write and read addresses from the user in the DDR SDRAM controller module. The user address consists of row, column, bank, and chip addresses, and the user command. Apart from the address decoding, timing parameters vary according to the density and speed grade.

Table 2-2 lists the timing parameters for components, and Table 2-3 lists the timing parameters for DIMMs.

| Parameter        | Description                             |           | Micron 128 Mb Micron 256 Mb |                     | Micron 512 Mb       |                     | Micron 1 Gb         |                     |                     |                     |

|------------------|-----------------------------------------|-----------|-----------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Farameter        |                                         |           | -5                          | -75                 | -5                  | -75                 | -5                  | -75                 | -5                  | -75                 |

| T <sub>CK</sub>  | Clock Cycle                             | CL = 3    | 5 ns                        | NA                  | 5 ns                | NA                  | 5 ns                | NA                  | 5 ns                | NA                  |

|                  | Time                                    | CL = 2.5  | 6 ns                        | 7.5 ns              | 6 ns                | 7.5 ns              | 6 ns                | 7.5 ns              | 6 ns                | 7.5 ns              |

|                  |                                         | CL = 2    | 7.5 ns                      | 10 ns               | 7.5 ns              | 10 ns               | 7.5 ns              | 10 ns               | 7.5 ns              | 10 ns               |

| T <sub>MRD</sub> | LOAD MODE<br>Command Cycle Time         |           | 10 ns                       | 15 ns               | 10 ns               | 15 ns               | 10 ns               | 15 ns               | 10 ns               | 15 ns               |

| T <sub>RP</sub>  | PRECHARGE<br>Command Period             |           | 15 ns                       | 20 ns               | 15 ns               | 20 ns               | 15 ns               | 20 ns               | 15 ns               | 20 ns               |

| T <sub>RFC</sub> | REFRESH Time                            |           | 70 ns                       | 75 ns               | 70 ns               | 75 ns               | 70 ns               | 75 ns               | 120 ns              | 120 ns              |

| T <sub>RCD</sub> | ACTIVE to READ or<br>WRITE Delay        |           | 15 ns                       | 20 ns               | 15 ns               | 20 ns               | 15 ns               | 20 ns               | 15 ns               | 20 ns               |

| T <sub>RAS</sub> | ACTIVE to<br>PRECHARGE<br>Command       |           | 40 ns                       | 40 ns               | 40 ns               | 40 ns               | 40 ns               | 40 ns               | 40 ns               | 40 ns               |

| T <sub>RC</sub>  | ACTIVE to ACTIVE<br>(Same Bank) Command |           | 55 ns                       | 65 ns               | 55 ns               | 65 ns               | 55 ns               | 65 ns               | 55 ns               | 65 ns               |

| T <sub>WTR</sub> | WRITE to READ<br>Command Delay          |           | 2*T <sub>CK</sub>           | 1 * T <sub>CK</sub> | 2 * T <sub>CK</sub> | 1 * T <sub>CK</sub> | 2 * T <sub>CK</sub> | 1 * T <sub>CK</sub> | 2 * T <sub>CK</sub> | 1 * T <sub>CK</sub> |

| T <sub>WR</sub>  | WRITE Recov                             | very Time | 15 ns                       | 15 ns               | 15 ns               | 15 ns               | 15 ns               | 15 ns               | 15 ns               | 15 ns               |

| Table 2-2: | Timing Parameters | for Components |

|------------|-------------------|----------------|

|------------|-------------------|----------------|

#### Table 2-3: Timing Parameters for DIMMs (Unbuffered and Registered)

| Deremeter        | Description                      |                                         | Micron 128 MB | Micron 256 MB | Micron 512 MB | Micron 1 GB |

|------------------|----------------------------------|-----------------------------------------|---------------|---------------|---------------|-------------|

| Parameter        |                                  |                                         | -40           | -40           | -40           | -40         |

| T <sub>CK</sub>  | Clock Cycle                      | CL = 3                                  | 5 ns          | 5 ns          | 5 ns          | 5 ns        |

|                  | Time                             | CL = 2.5                                | 6 ns          | 6 ns          | 6 ns          | 6 ns        |

|                  |                                  | CL = 2                                  | 7.5 ns        | 7.5 ns        | 7.5 ns        | 7.5 ns      |

| T <sub>MRD</sub> | LOAD MODE Command<br>Cycle Time  |                                         | 10 ns         | 10 ns         | 10 ns         | 10 ns       |

| T <sub>RP</sub>  | PRECHARGE Command<br>Period      |                                         | 15 ns         | 15 ns         | 15 ns         | 15 ns       |

| T <sub>RFC</sub> | REFRESH Time                     |                                         | 70 ns         | 70 ns         | 70 ns         | 70 ns       |

| T <sub>RCD</sub> | ACTIVE to READ or WRITE<br>Delay |                                         | 15 ns         | 15 ns         | 15 ns         | 15 ns       |

| T <sub>RAS</sub> | ACTIVE to PRECHARGE<br>Command   |                                         | 40 ns         | 40 ns         | 40 ns         | 40 ns       |

| T <sub>RC</sub>  |                                  | ACTIVE to ACTIVE (Same<br>Bank) Command |               | 55 ns         | 55 ns         | 55 ns       |

| Parameter        | Description                 | Micron 128 MB       | Micron 256 MB       | Micron 512 MB       | Micron 1 GB         |

|------------------|-----------------------------|---------------------|---------------------|---------------------|---------------------|

| rarameter        | Description                 | -40                 | -40                 | -40                 | -40                 |

| T <sub>WTR</sub> | WRITE to READ Command Delay | 2 * T <sub>CK</sub> |

| T <sub>WR</sub>  | WRITE Recovery Time         | 15 ns               | 15 ns               | 15 ns               | 15 ns               |

| Table 2-3: | Timing Parameters for DIMMs | (Unbuffered and Registered) (C | Continued) |

|------------|-----------------------------|--------------------------------|------------|

|------------|-----------------------------|--------------------------------|------------|

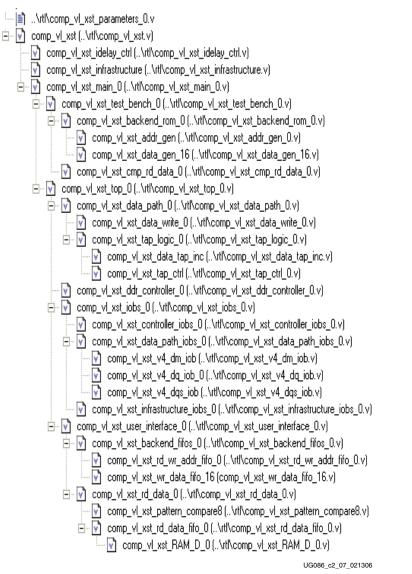

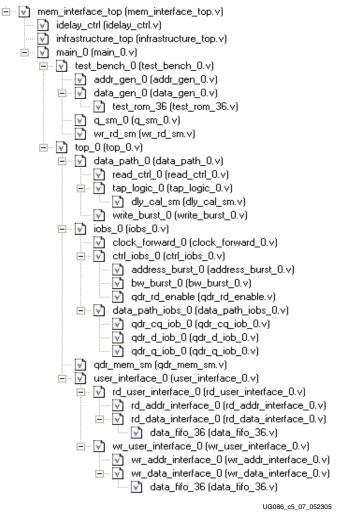

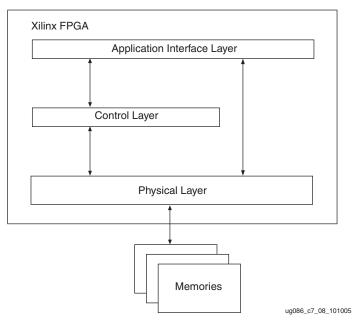

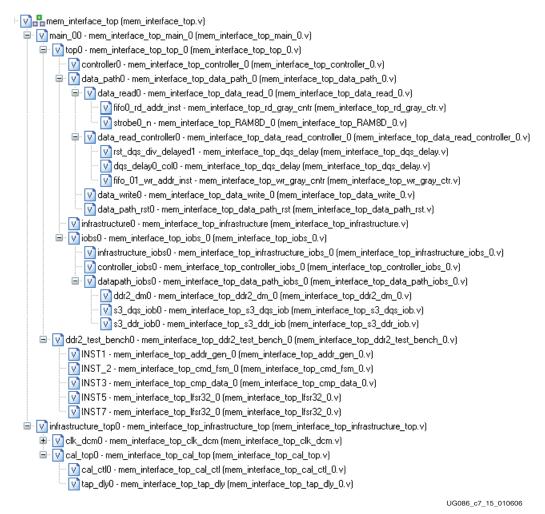

## Hierarchy

Figure 2-2 shows the hierarchical structure of the modular design. The physical and control layers are clearly separated in this figure. The MIG 1.5 tool generates the entire DDR SDRAM controller as shown in this hierarchy, including the test bench.

*Figure 2-2:* **Hierarchical Structure of the DDR SDRAM Virtex-4 Design**

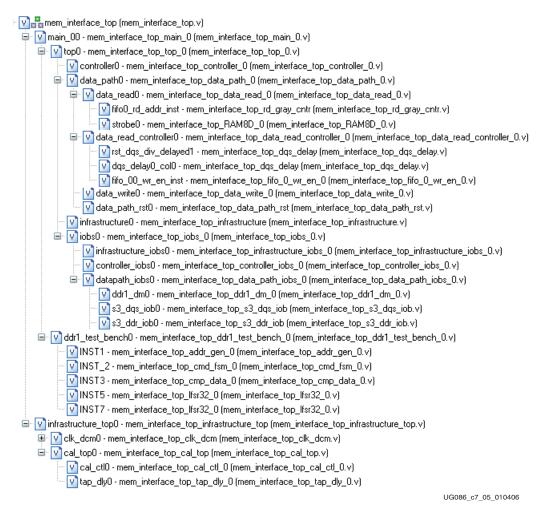

## **DDR Controller Submodules**

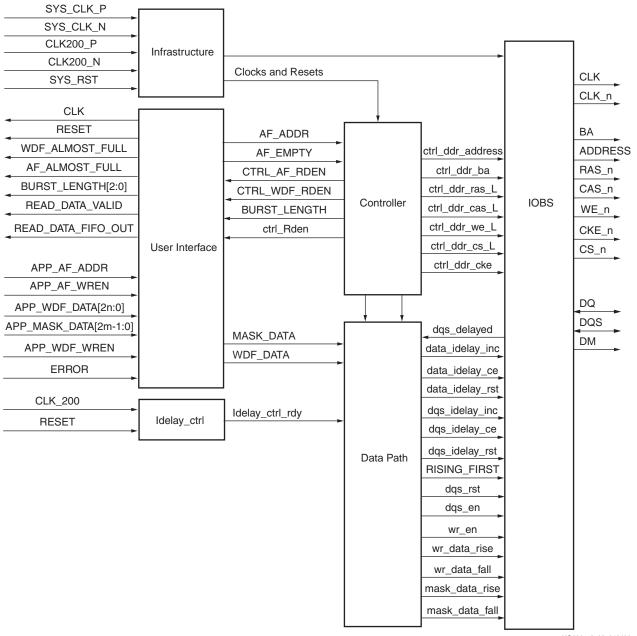

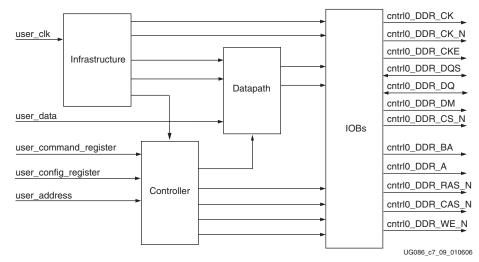

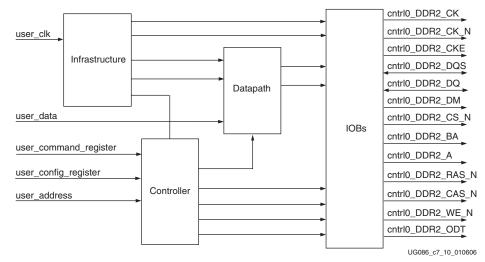

Figure 2-3 is a detailed block diagram of the DDR SDRAM controller. The six blocks shown in this figure are the sub-blocks of the top module. The functions of these blocks are explained in the subsections following the figure.

UG086\_c2\_08\_010406

Figure 2-3: DDR SDRAM Controller Block Diagram

#### Controller

The DDR SDRAM controller initializes the memory, accepts and decodes user commands, and generates READ, WRITE, and REFRESH commands. The DDR SDRAM controller also generates signals for other modules. The memory is initialized and powered-up using a defined process. The controller state machine handles the initialization process upon

power-up. If the AUTO REFRESH command is to be issued between any user read or write commands, then the read or write command will be suspended until the ar\_done flag is deasserted. The user must not issue any other command until the ar\_done flag is deasserted.

#### Datapath

This module transmits data to the memories. Its major functions include storing the write data and calculating the tap value for the read datapath. The data\_write and data\_path\_IOBs modules do the actual write functions. The Idelay\_ctrl, tap\_ctrl and data\_tap\_inc modules do the calibration.

#### User Interface

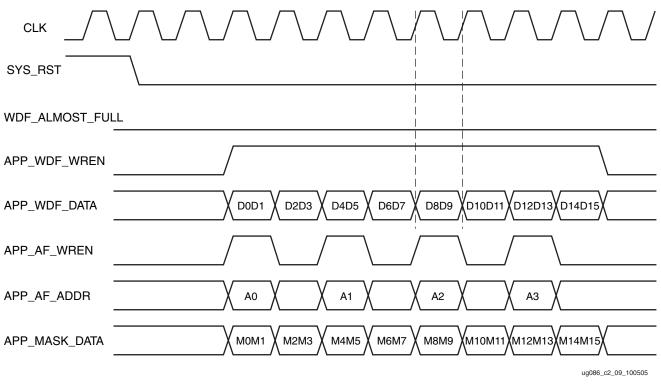

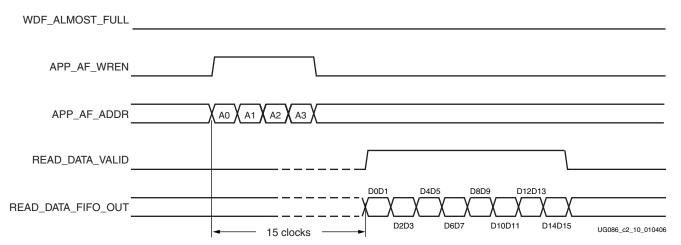

This module stores write data in its Write Data FIFO (wr\_data\_fifo), stores write and read addresses in its Read/Write Address FIFO (rd\_wr\_addr\_fifo), and stores received read data from memory in its Read Data FIFO (rd\_data\_fifo). The width of the Write Data FIFO is twice the data width and mask width of the memory. For example, for a 16-bit width, the width of the FIFO is 36 because the data width is 32 and the mask width is 4. The rd\_wr\_addr\_fifo and wr\_data\_fifo modules store the data and address in block RAMs. The rd\_data\_fifo module captures the data in the LUT-based RAMs.

The controller also generates user commands, such as READ and WRITE. To execute a WRITE command, the user loads both READ and WRITE commands. The controller starts a WRITE operation only when both READ and WRITE commands are loaded into their corresponding FIFOs. The controller processes all subsequent commands alternately (READ, WRITE, READ, WRITE, and so forth).

The pattern\_compare module registers the delay between the command and the data received from the IOBs. This delay is then applied to the Rden signal generated from the ddr\_controller module during the actual read to register the valid data in the internal FIFOs.

#### Infrastructure

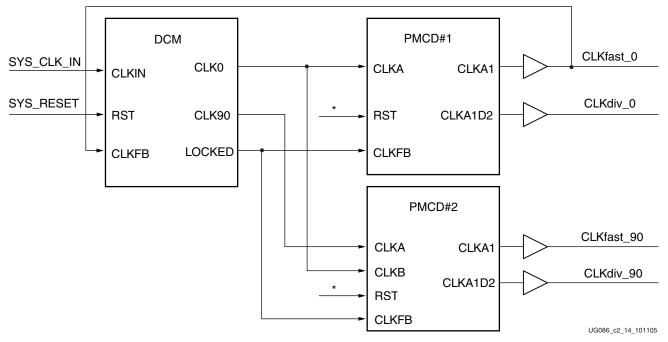

The infrastructure module generates the FPGA clocks and reset signals. A DCM generates the phase-shifted clocks (clk0, clk90), refresh clock, and calibration clock. All the reset signals required for the design are also generated.

#### **IOBS Module**

All DDR SDRAM address, control, and data signals are transmitted and received in the through the input and output buffers.

# **DDR SDRAM Memory Initialization and Calibration**

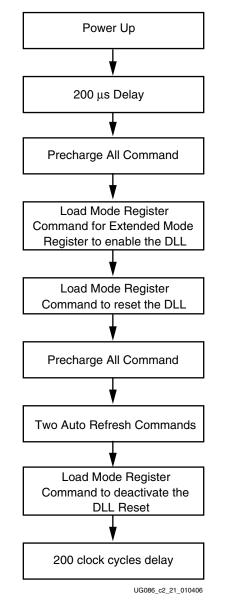

DDR memory is initialized through a specified sequence as shown in Figure 2-4. Following the initialization, the relationship between the data and the FPGA clock is calculated using the TAP logic. The controller issues a dummy read command to the memory. As the data and the memory strobe are edge-aligned, the strobe is passed through the IDELAY elements of the Virtex-4 device and the taps are adjusted to find the center of the strobe pulse. The number of taps is then used to delay the data during normal reads to register the valid data in the FPGA. XAPP701 [Ref 10] provides more information.

Following the strobe detection, the controller does a pattern write and then a pattern read to find the delay of the data it takes from the IOBs. As soon as the read command is issued, the data from the IOB is registered at every clock cycle and is checked for the fixed pattern written. The number of clocks required for the valid data is registered and used during normal reads to capture valid data in the internal block RAM.

Figure 2-4: DDR Memory Initialization Sequence

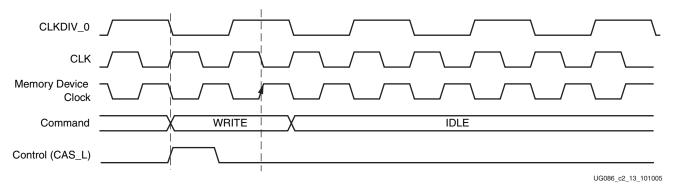

# **DDR SDRAM System and User Interface Signals**

Table 2-4 describes the DDR SDRAM system interface signals. The system interface signals are the clocks and the reset signals given by the user to the FPGA. SYS\_CLK\_P and SYS\_CLK\_N are the two clocks to be provided to the design. These two clocks must have a phase difference of 180 degrees with respect to each other. SYS\_RST resets all the logic.

Table 2-4: DDR SDRAM System Interface Signals

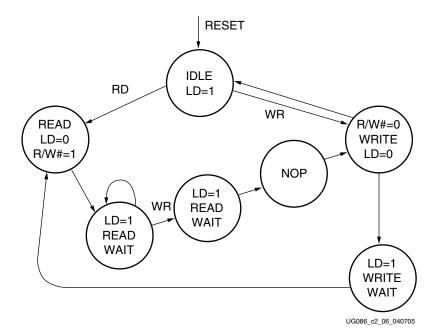

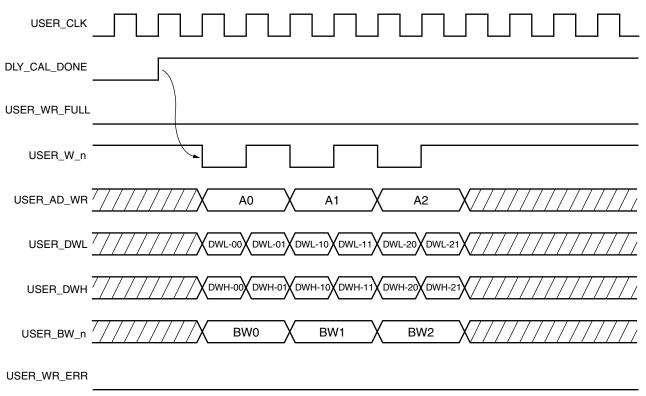

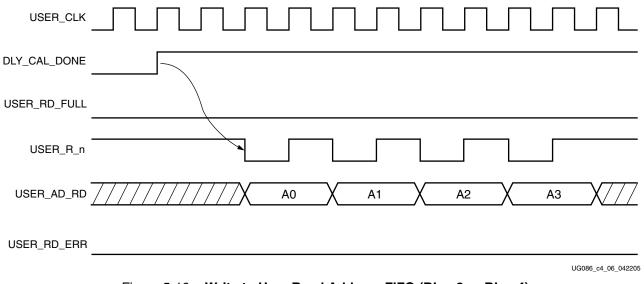

| Signal Name          | Direction | Description                                                                                         |