# UVM Layering for Protocol Modeling Using State Pattern

Tony George – Samsung Semiconductor, Inc. Girish Gupta – Samsung Semiconductor India R&D, Bangalore Shim Hojun - Samsung Semiconductor Co., Ltd. Byung C. Yoo - Samsung Semiconductor Co., Ltd.

# **Layered Protocol and verification**

- Layering protocol are similar to Open System Interconnect (OSI) models

- Each layer has its own set of functionality and features which needs to be verified

- Control of the functional flow at each layer anc error injection is also part of verification

SYSTEMS INITIATIVE

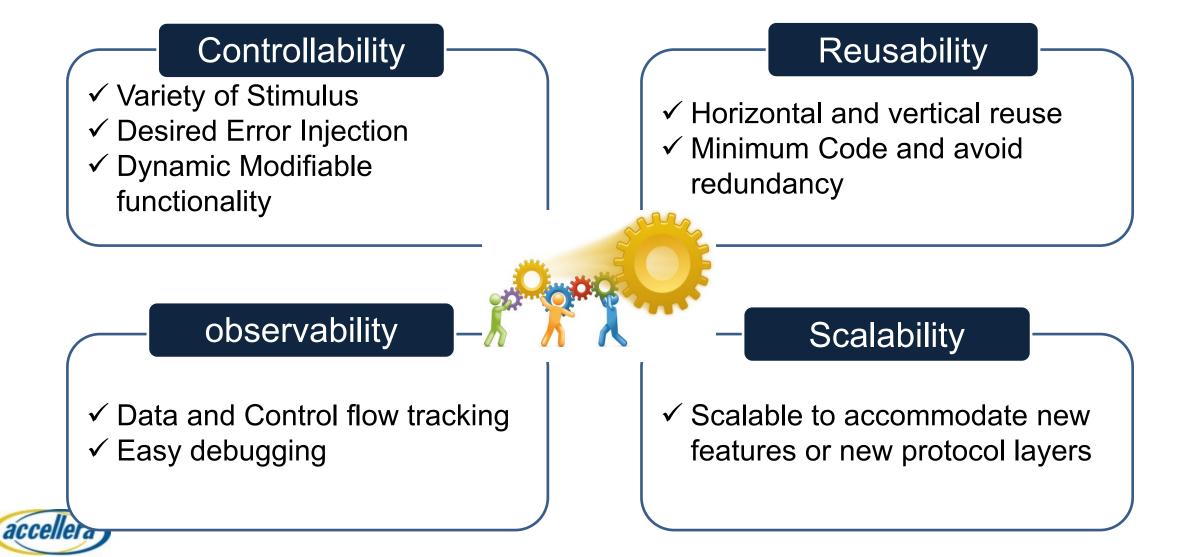

# **Expectations from Verification IP**

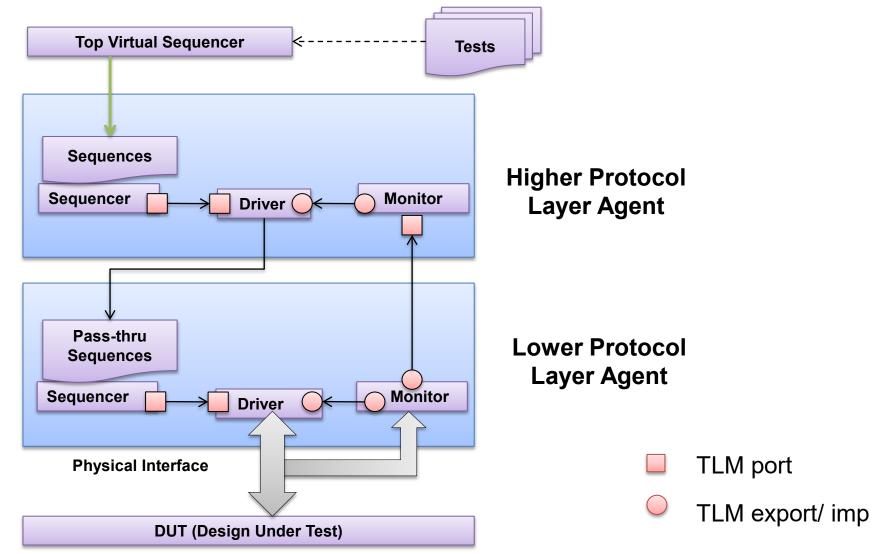

# **Existing Approach – Layered Sequencer**

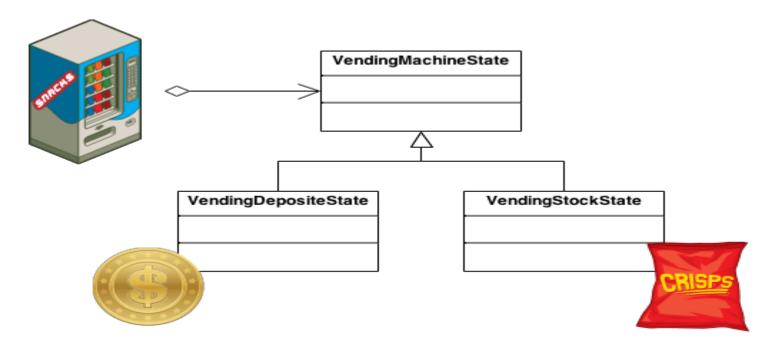

# What is state pattern ?

• The **state pattern** is a behavioral software design **pattern** that allows an object to alter its behavior when its internal **state** changes.

Image Source : sourcemaking.com

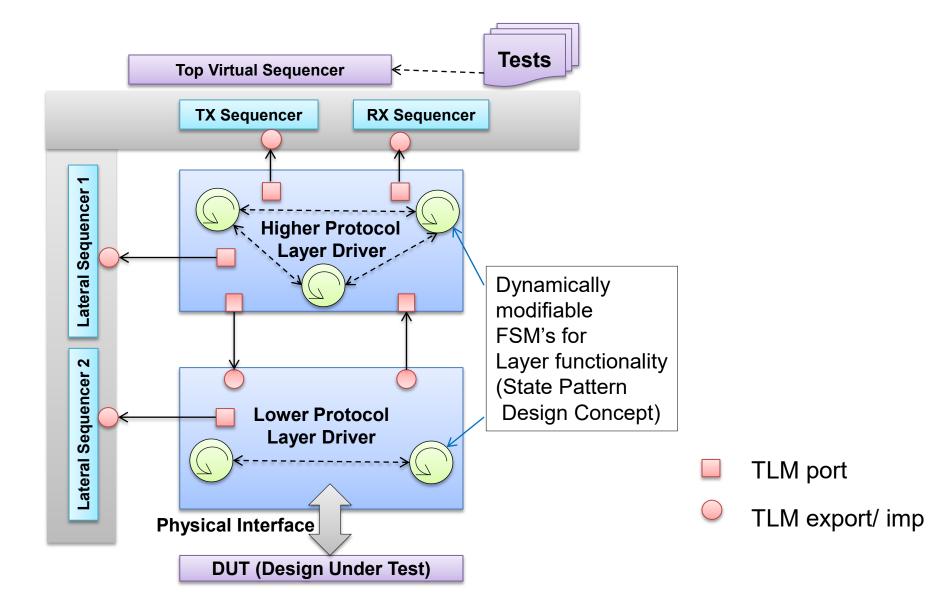

## **Proposed Approach using State Pattern**

accelle

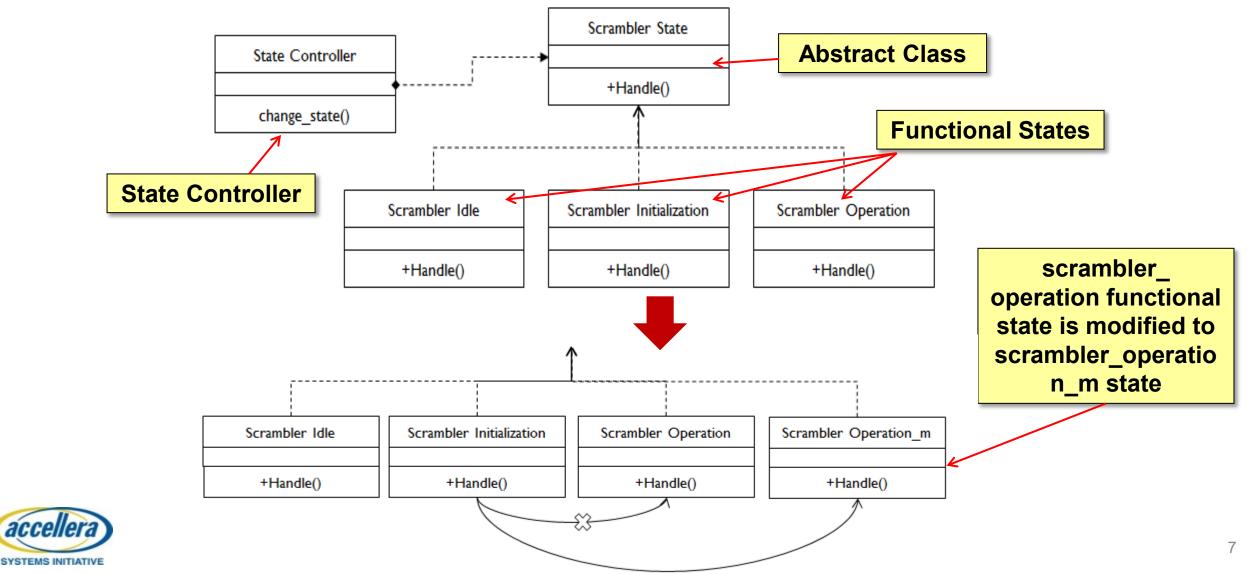

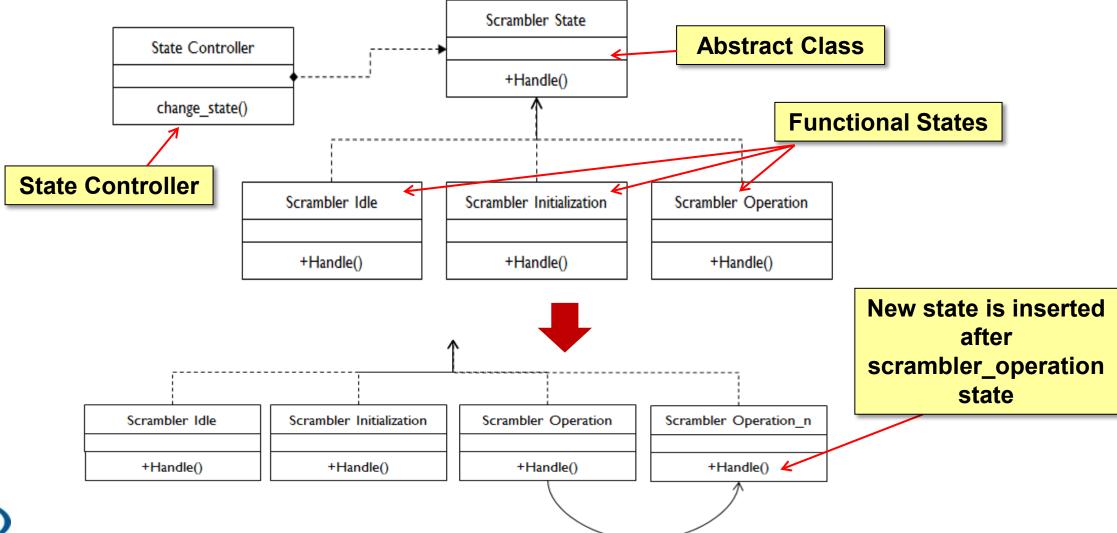

## **State Pattern : New State insertion**

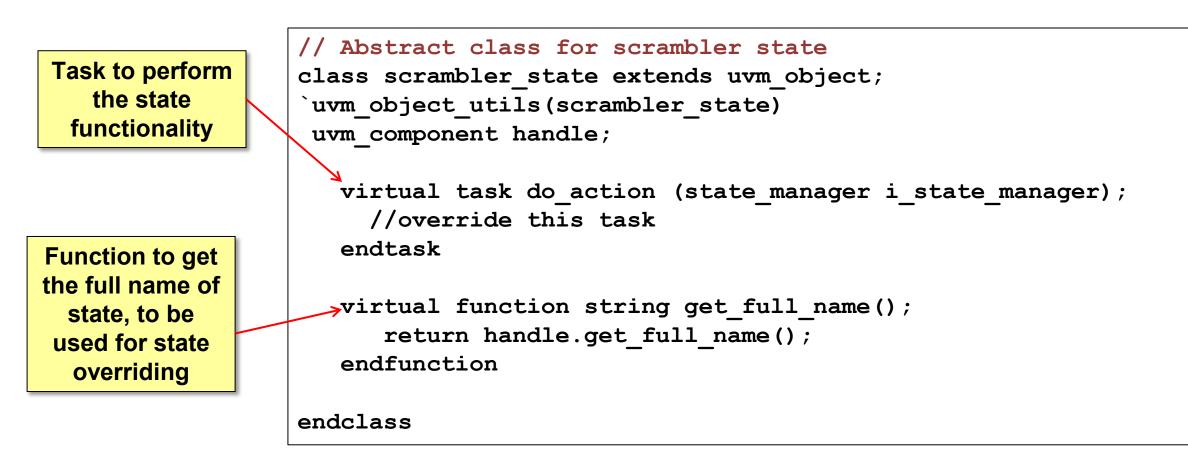

## **Code Snippet : Abstract Class**

## **Code Snippet : State Controller**

// State Controller

```

class state_controller extends uvm_component;

`uvm_component_utils(state_controller)

```

Building the Idle Scrambler State

#### //Build\_phase

Casting the state handle into new state handle

```

i state.do action(this);

```

scrambler state i state;

i state.handle = this;

```

virtual task change_state (string state_name);

//Casting state handle into new state handle

$cast(i_state,factory.create_object_by_name(state_name,

get_full_name()))

i_state_handle = this;

endtask

endclass

```

i state = idle scrambler state::type\_id::create();

### **Code Snippet : State Behavior modification**

Instead of moving to Ifsr\_operation\_state, moving to modified Isfr\_operation\_state (Modified state)

```

// scrambler LFSR Initialization state

```

```

class lfsr_init_state extends scrambler_state;

`uvm_object_utils(lfsr_init_state)

```

virtual task do\_action (state\_manager i\_state\_manager);

//Perform Scrambler LFSR Init state functionality

```

/ Move to next state -> MODIFIED LFSR Operation

```

```

i_state_manager.change_state("mod_lfsr_operation_state);

```

endtask endclass

# **Code Snippet : New State Insertion**

Instead of moving to Ifsr\_idle\_state, moving to new functional state new\_lsfr\_operation\_st ate (new state) // scrambler LFSR Operation state

class lfsr\_operation\_state extends scrambler\_state; `uvm\_object\_utils(lfsr\_operation\_state)

virtual task do\_action (state\_manager i\_state\_manager);

//Perform Scrambler LFSR Operation state functionality

// Move to next state -> NEW LFSR Operation State

i\_state\_manager.change\_state("new\_lfsr\_operation\_state); endtask

endclass

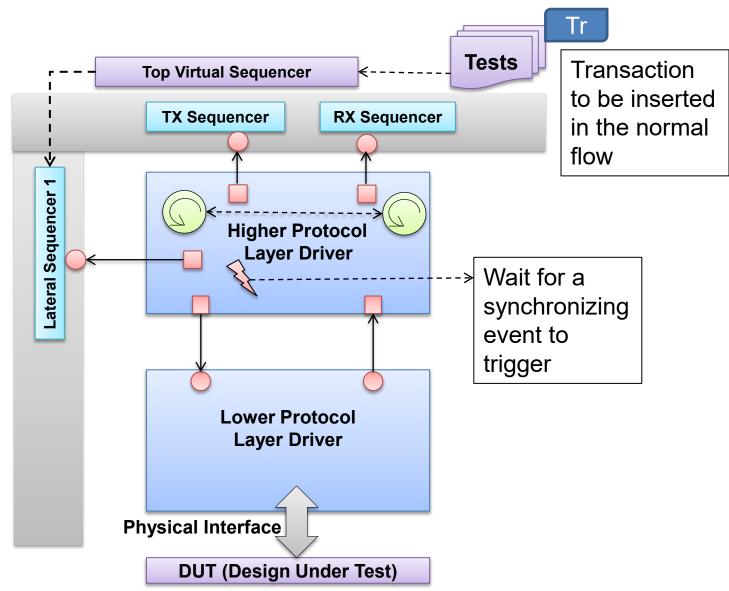

## **Error Injection using Lateral Sequencer**

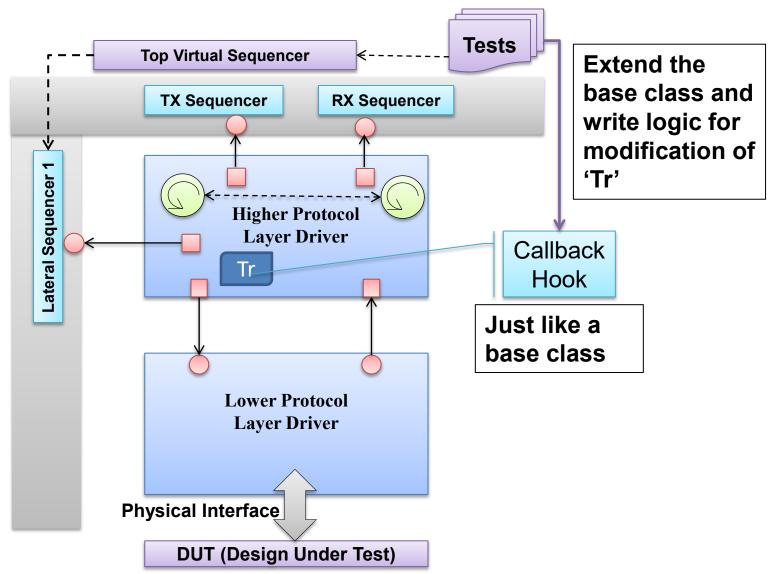

# **Error Injection using Callback**

# State Pattern Vs Finite State Machine

• The State Pattern abstract the states and decouple them from each other

- Example : you can easily replace one particular state with another. Yet you will not be happy rewriting all the states when it is time to add a new one and/or a new transition

• The state machine abstracts the state diagram itself and decouples it from the transition payloads.

- Example : To change a particular state, you have to fix the whole diagram

## **Observation & Results**

| Parameters     | Traditional (Existing<br>approach) VIP | <b>Proposed VIP (Layered<br/>State pattern)</b>                        |

|----------------|----------------------------------------|------------------------------------------------------------------------|

| Bugs found     | 35, before design went into silicon    | Additional 10 Major bugs<br>and 5 minor bugs found in<br>the design    |

| Test Scenarios | 250                                    | Additional 40 (targeting error<br>scenarios and exception<br>handling) |

# Conclusion

- The motivation for this paper is to analyze and conclude on a Verification IP Architecture which provides full-fledged control without compromising on the simplicity of model development.

- Dynamically modifiable functionality of all layers along with complex test scenario generation is achieved using this methodology.

- The proposed architecture has been deployed for live verification project on UniPro and PCIe protocols.

# Thank You !.