# **Vivado Design Suite Tutorial**

## Model-Based DSP Design Using System Generator

UG948 (v2016.4) November 30, 2016

This tutorial was validated with 2016.3. Minor procedural differences might be required when using later releases.

## **Revision History**

11/30/2016: Released with Vivado® Design Suite 2016.4 without changes from 2016.3.

| Date       | Version | Changes                                                                                                                                                                                              |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/28/2016 | 2016.3  | Recaptured screen displays throughout manual to reflect changes to GUI or changes in results displayed.                                                                                              |

|            |         | In Lab 2: Working with Data Types, added procedural step to specify the number of input ports on the Scope block, allowing the block to be properly connected to other blocks in the Simulink model. |

| 06/20/2016 | 2016.2  | No technical updates. Re-release only.                                                                                                                                                               |

| 05/23/2016 | 2016.1  | Recaptured screen displays throughout manual to reflect changes to GUI or changes in results displayed.                                                                                              |

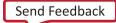

|            |         | In design used in Lab 1_1 and 1_2, replaced FIR Compiler 7.2 block with Digital FIR Filter block.                                                                                                    |

## **Table of Contents**

| Revision History                                           | 2 |

|------------------------------------------------------------|---|

| System Generator for DSP Overview                          | 5 |

| Introduction                                               | 5 |

| Software Requirements                                      | 7 |

| Configuring MATLAB to the Vivado <sup>®</sup> Design Suite | 7 |

| Locating and Preparing the Tutorial Design Files           | 8 |

| Lab 1: Introduction to System Generator                    | 9 |

| Introduction                                               | 9 |

| Step 1: Creating a Design in an FPGA                       |   |

| Step 2: Creating an Optimized Design in an FPGA            |   |

| Step 3: Creating a Design Using Discrete Resources         |   |

| Summary                                                    |   |

| Lab 2: Working with Data Types                             |   |

| Introduction                                               |   |

| Step 1: Designing with Floating-Point Data Types           |   |

| Step 2: Designing with Fixed-Point Data Types              |   |

| Summary                                                    |   |

| Lab 3: Working with Multi-Rate Systems                     |   |

| Introduction                                               |   |

| Step 1: Creating Clock Domain Hierarchies                  |   |

| Step 2: Creating Asynchronous Channels                     |   |

| Step 3: Specifying Clock Domains                           |   |

| Summary                                                    |   |

| Lab 4: Working with Workspace Variables                    |   |

| Introduction                                               |   |

| Step 1: Using Workspace Variables                          |   |

| Summary                                                    |   |

| Lab 5: Modeling Control with M-Code                                 |     |

|---------------------------------------------------------------------|-----|

| Introduction                                                        |     |

| Step 1: Designing Padding Logic                                     |     |

| Summary                                                             |     |

| Lab 6: Modeling Blocks with HDL                                     |     |

| Introduction                                                        |     |

| Step 1: Import RTL as a Black Box                                   |     |

| Summary                                                             |     |

| Lab 7: Modeling Blocks with C Code                                  |     |

| Introduction                                                        |     |

| Step 1: Creating a System Generator Package from Vivado HLS         |     |

| Step 2: Including a Vivado HLS Package in a System Generator Design |     |

| Summary                                                             |     |

| Lab 8: Using AXI Interfaces and IP Integrator                       |     |

| Introduction                                                        |     |

| Step 1: Review the AXI Interfaces                                   |     |

| Step 2: Create a Vivado Project using System Generator IP           |     |

| Step 3: Create a Design in IP Integrator (IPI)                      |     |

| Step 4: Implement the Design                                        | 108 |

| Summary                                                             | 109 |

| Lab 9: Using a System Generator Design with a Zynq-7000 AP SoC      | 110 |

| Introduction                                                        | 110 |

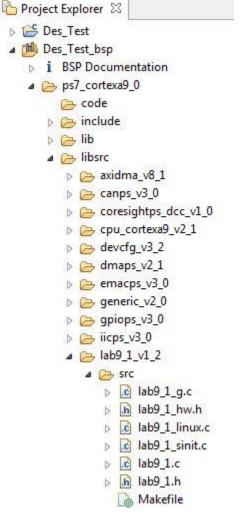

| Step 1: Review the AXI4-Lite Interface Drivers                      | 111 |

| Step 2: Developing Software and Running it on the ZYNQ-7000 System  | 114 |

| Summary                                                             | 120 |

| Legal Notices                                                       | 121 |

| Please Read: Important Legal Notices                                | 121 |

## System Generator for DSP Overview

#### Introduction

System Generator for DSP is a design tool in the Vivado<sup>®</sup> Design Suite that enables you to use the MathWorks<sup>®</sup> model-based Simulink® design environment for FPGA design. Previous experience with Xilinx<sup>®</sup> FPGA devices or RTL design methodologies is not required when using System Generator. Designs are captured in the Simulink<sup>™</sup> modeling environment using a Xilinx-specific block set. Downstream FPGA steps including RTL synthesis and implementation (where the gate level design is placed and routed in the FPGA) are automatically performed to produce an FPGA programming bitstream.

Over 80 building blocks are included in the Xilinx-specific DSP block set for Simulink. These blocks include common building blocks such as adders, multipliers and registers. Also included are complex DSP building blocks such as forward-error-correction blocks, FFTs, filters, and memories. These complex blocks leverage Xilinx LogiCORE<sup>™</sup> IP to produce optimized results for the selected target device.

**VIDEO:** The <u>Vivado Design Suite Quick Take Video Tutorial</u>: <u>System Generator Multiple</u> <u>Clock Domains</u> describes how to use Multiple Clock Domains within System Generator, making it possible to implement complex DSP systems.

**VIDEO:** The <u>Vivado Design Suite QuickTake Video Tutorial: Generating Vivado HLS block</u> for use in System Generator for DSP describes how to generate a Vivado HLS IP block for use in System Generator, and ends with a summary of how the Vivado HLS block can be used in your System Generator design.

**VIDEO:** The <u>Vivado Design Suite Quick Take Video: Using Vivado HLS C/C++/System C</u> <u>block in System Generator</u> describes how to incorporate your Vivado HLS design as an IP block into System Generator for DSP.

VIDEO: The Vivado Design Suite Quick Take Video: Specifying AXI4-Lite Interfaces for your

<u>Vivado System Generator Design</u> describes how System Generator provides AXI4-Lite abstraction making it possible to incorporate a DSP design into an embedded system. Full support includes integration into the IP Catalog, interface connectivity automation, and software APIs.

VIDEO: The Vivado Design Suite QuickTake Video Tutorial: Using Hardware Co-Simulation

<u>with Vivado System Generator for DSP</u> describes how to use Point-to-Point Ethernet Hardware Co-Simulation with Vivado System Generator for DSP. Hardware co-simulation makes it possible to incorporate a design running in an FPGA directly into a Simulink simulation.

In this tutorial, you will do the following:

- Lab 1: Understand how to create and validate a model using System Generator, synthesize the model into FPGA hardware, and then create a more optimal hardware version of the design.

- Lab 2: Learn how fixed-point data types can be used to trade off accuracy against hardware area and performance.

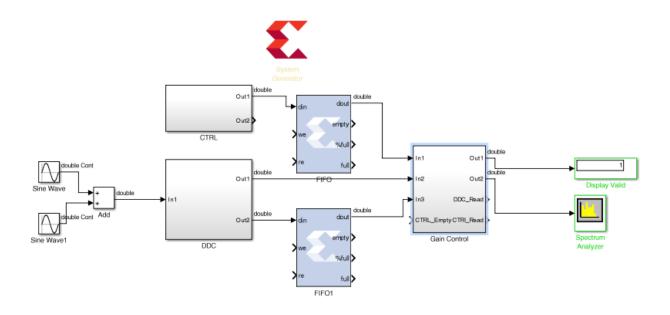

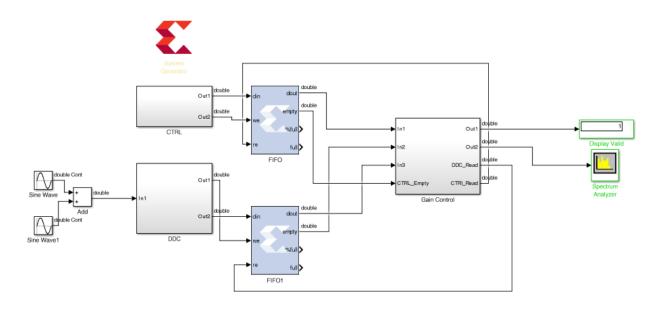

- Lab 3: Learn how to create an efficient design using multiple clock domains.

- Lab 4: Make use of workspace variables to easily parameterize your models.

- Lab 5: Model a control system using M-code.

- Lab 6: Learn how to incorporate existing RTL designs, written in Verilog or VHDL, into your design.

- Lab 7: Import C/C++ source files into a System Generator model by leveraging the tool integration with Vivado High-Level Synthesis (HLS).

- Lab 8: Use AXI interfaces and Vivado IP integrator to easily include your model into a larger design.

- Lab 9: Integrate your design into a larger system and operate the design under CPU control.

#### **Software Requirements**

The lab exercises in this tutorial require the installation of MATLAB R2015b, R2015a, R2014b, or R2014.a.

See the *Vivado Design Suite User Guide: Release Notes, Installation, and Licensing* (UG973) for a complete list and description of the system and software requirements.

#### **Configuring MATLAB to the Vivado® Design Suite**

Before you begin, you should verify that MATLAB is configured to the Vivado Design Suite. Do the following:

- 1. Configure MATLAB.

- On Windows systems:

- a. Select Start > All Programs > Xilinx Design Tools > Vivado 2016.3 > System Generator > System Generator 2016.3 MATLAB Configurator.

**IMPORTANT:** On Windows systems you may need to launch the MATLAB configurator as Administrator. When **MATLAB Configurator** is selected in the menu, use the mouse right-click to select **Run as Administrator**.

| 😣 Select a MATLA    | B installation for Syste | em Generator Vivado 2016.3     |  |

|---------------------|--------------------------|--------------------------------|--|

| Choose MATLAB for S | ystem Generator Vivado 2 | 2016.3                         |  |

| MATLAB Version      | Status                   | Location                       |  |

| 🔲 📣 R2015b          | Configured               | C:\Program Files\MATLAB\R2015b |  |

| Fir                 | nd MATLAB Remove         | e Apply Ok Help                |  |

Figure 1: Select MATLAB Installation

- b. Click the check box of the version of MATLAB you want to configure and then click **OK**.

- On Linux systems:

Launching System Generator under Linux is handled via a shell script called sysgen located in the <Vivado install dir>/bin directory. Before launching this script, you must make sure the

MATLAB executable can be found in your Linux system's \$PATH environment variable. When you execute the sysgen script, it will launch the first MATLAB executable found in \$PATH and attach System Generator to that session of MATLAB. Also, the sysgen shell script supports all the options that MATLAB supports and all options can be passed as command line arguments to the sysgen script.

When the System Generator opens, you can confirm the version of MATLAB to which System Generator is attached by entering the version command in the MATLAB Command Window.

```

>> version

ans =

8.6.0.267246 (R2015b)

```

#### Locating and Preparing the Tutorial Design Files

There are separate project files and sources for each of the labs in this tutorial. You can find the design files for this tutorial under **Error! Hyperlink reference not valid.** on the www.xilinx.com website.

- 1. Download the <u>Reference Design Files</u> (ug948-design-files.zip) from the Xilinx website.

- 2. **Extract** the zip file contents into any write-accessible location on your hard drive or network location.

**RECOMMENDED:** You will modify the tutorial design data while working through this tutorial. You should use a new copy of the *SysGen\_Tutorial* directory extracted from ug948-design-files.zip each time you start this tutorial.

**TIP:** This document assumes the tutorial files are stored at C:\SysGen\_Tutorial. All pathnames and figures in this document refer to this pathname. If you choose to store the tutorial in another location, adjust the pathnames accordingly.

## Lab 1: Introduction to System Generator

#### Introduction

In this lab exercise, you will learn how use System Generator to specify a design in Simulink and synthesize the design into an FPGA. This tutorial uses a standard FIR filter and demonstrates how System Generator provides you the design options that allow you to control the fidelity of the final FPGA hardware.

#### Objectives

After completing this lab, you will be able to:

- Capture your design using the System Generator Blocksets.

- Capture your designs in either complex or discrete Blocksets.

- Synthesize your designs in an FPGA using the Vivado Design Environment.

#### Procedure

This lab has three primary parts:

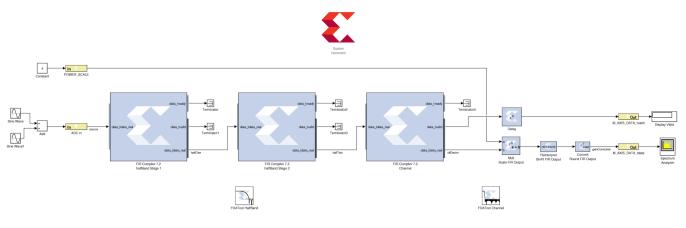

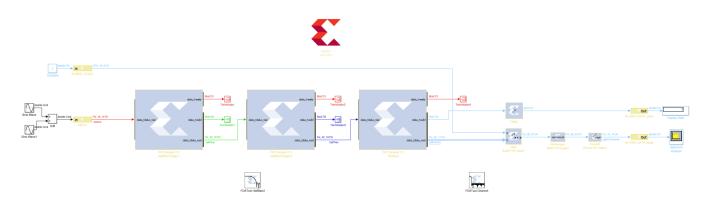

- In Step 1, you will review an existing Simulink design using the Xilinx FIR Compiler block, and review the final gate level results in Vivado.

- In Step 2, over-sampling is used to create a more efficient design.

- In Step 3, the same filter is designed using standard discrete blockset parts.

#### Step 1: Creating a Design in an FPGA

In this step you learn the basic operation of System Generator and how to synthesize a Simulink design into an FPGA.

- 1. Invoke System Generator.

- On Windows systems select Start > All Programs > Xilinx Design Tools > Vivado 2016.3 > System Generator > System Generator 2016.3.

- On Linux Systems, type sysgen at the command prompt.

- 2. Navigate to the Lab1 folder: cd C:\SysGen\_Tutorial\Lab1.

You can view the directory contents in the MATLAB **Current Folder** browser, or type ls at the command line prompt.

- 3. Open the Lab1\_1 design as follows:

- At the MATLAB command prompt, type open Lab1\_1.slx

OR

• Double-click Lab1 1.slx in the Current Folder browser.

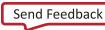

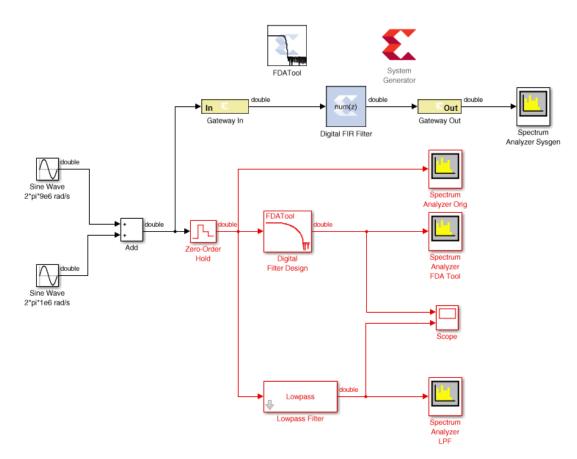

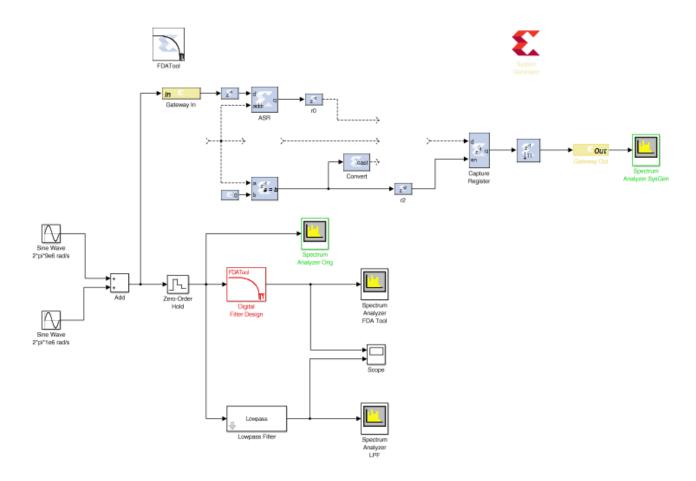

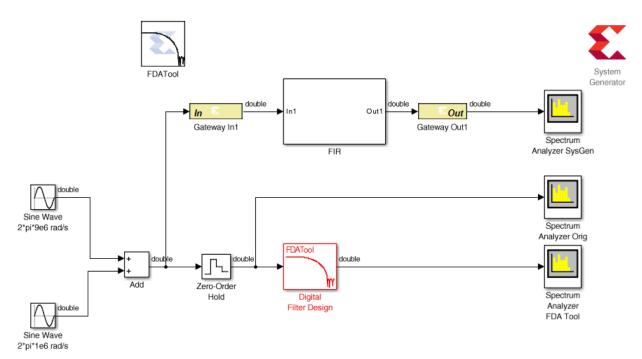

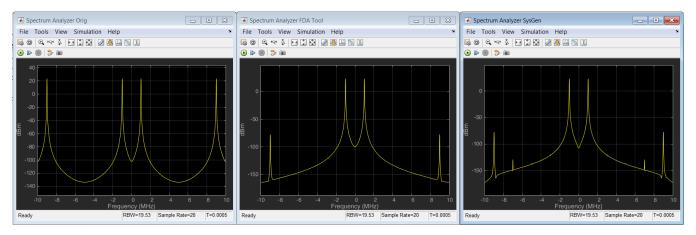

The Lab1\_1 design opens, showing two sine wave sources being added together and passed separately through two low-pass filters. This design highlights that a low-pass filter may be implemented using the Simulink **FDATool** or **Lowpass Filter** blocks.

Figure 2: Introduction Step 1 Design

4. From your Simulink project worksheet, select **Simulation > Run** or click the **Run** simulation button.

Figure 3: Run Simulation Button

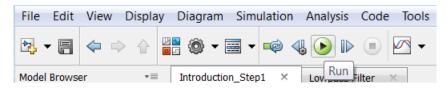

When simulation completes you can see the spectrum for the initial summed waveforms, showing a 1 MHz and 9 MHz component, and the results of both filters showing the attenuation of the 9 MHz signals.

**Figure 4: Initial Results**

You will now create a version of this same filter using System Generator blocks for implementation in an FPGA.

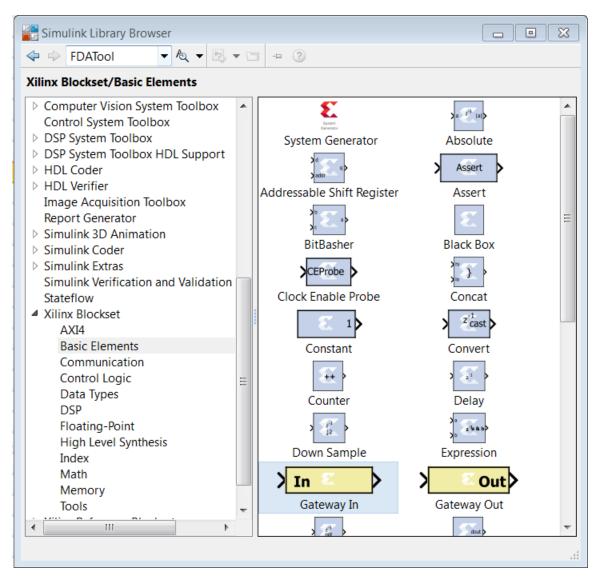

5. Click the Library Browser button in the Simulink toolbar to open the Simulink Library Browser.

Figure 5: Simulink Library Browser

When using System Generator, the Simulink library includes specific blocks for implementing designs in an FPGA. You can find a complete description of the blocks provided by System Generator in the *Vivado Design Suite Reference Guide: Model-Based DSP Design Using System Generator* (UG958).

- 6. Expand the Xilinx Blockset menu, select DSP, then select Digital FIR Filter.

- 7. Right-click the **Digital FIR Filter** block and select **Add block to model Lab1\_1**.

| 🛛 🖒 Enter search term 🔹 🍖 👻                                                                                                                                                                                                                                                                                                                                                                                                                                                        | , - 🔄 💣 + 🤅      |                                                                                                                                                                            |                       |                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|

| 1x Blockset/DSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                                                                                                                                                                            |                       |                  |

| Simulink Communications System Toolbox Communications System Toolbox HDL Support Computer Vision System Toolbox DSP System Toolbox DSP System Toolbox HDL Support HDL Coder HDL Verifier Image Acquisition Toolbox Phased Array System Toolbox Simulink 3D Animation Simulink Coder Simulink Extras Stateflow Xilinx Blockset AXI4 Basic Elements Communication Control Logic Data Types DSP Floating-Point Index Math Memory Tools Xilinx Reference Blockset Recently Used Blocks | CIC Compiler 4.0 | Complex Multiplier 6.0<br>Divider Generator 5.1<br>Add block to model L<br>Help for the Digital Fl<br>Go to parent<br>Block parameters<br>Sort in library model<br>Product | R Filter block<br>Esc | DDS Compiler 6.0 |

Figure 6: Add Digital FIR Filter Block

You can define the filter coefficients for the Digital FIR Filter block by accessing the block attributes – double-click the **Digital FIR Filter** block to view these – or, as in this case, they may be defined using the FDATool.

8. In the same DSP blockset as the previous step, select **FDATool** and add it to the Lab1\_1 design.

An FPGA design requires three important aspects to be defined:

- The input ports

- The output ports

- The FPGA technology

The next three steps show how each of these attributes is added to your Simulink design.

**IMPORTANT:** If you fail to correctly add these components to your design, it cannot be implemented in an FPGA. Subsequent labs will review in detail how these blocks are configured; however, they must be present in all System Generator designs.

9. In the Basic Elements menu, select **Gateway In** and add it to the design.

Figure 7: Adding a Gateway In

- 10. Similarly, from the same menu add a **Gateway Out** block to the design.

- 11. Similarly, from the same menu add the **System Generator** token used to define the FPGA technology.

- 12. Finally, make a copy of one of the existing Spectrum Analyzer blocks and rename the instance to Spectrum Analyzer SysGen by clicking the instance name label and editing the text.

- 13. Connect the blocks as shown in the following figure. Use the left-mouse key to make connections between ports and nets.

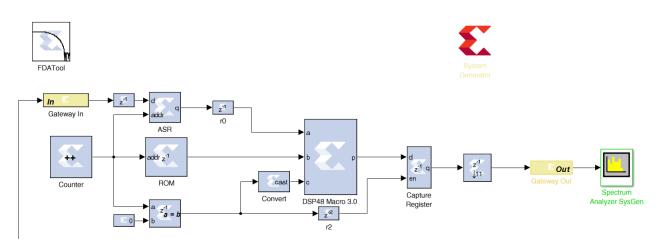

Figure 8: Initial System Generator Design

The next part of the design process is to configure the System Generator blocks.

#### Configure the System Generator Blocks

The first task is to define the coefficients of the new filter. For this task you will use the Xilinx block version of FDATool. If you open the existing FDATool block, you can review the existing Frequency and Magnitude specifications.

1. Double-click the **Digital Filter Design** instance to open the Properties Editor.

This allows you to review the properties of the existing filter.

| 🔺 Block Parameters: Digital Filter Desi                                    | gn                                            |                            |                          |

|----------------------------------------------------------------------------|-----------------------------------------------|----------------------------|--------------------------|

| File Edit Analysis Targets View                                            | Window Help                                   |                            |                          |

| 🗅 🖨 🖶 🚭 💽 🔍 🔍 🖄                                                            | 10 🔜 💽 💀 😫 🕻                                  | 1 - 🌐 😡 🛈 🔽 🖃              |                          |

| Current Filter Information                                                 | Magnitude Response (dB)                       |                            |                          |

| Structure: Direct-Form FIR<br>Order: 10<br>Stable: Yes<br>Source: Designed | (g) -20 -<br>entropy -40 -<br>-60 -<br>-100 - |                            |                          |

| Store Filter<br>Filter Manager                                             | 0 2                                           | 4 6<br>Frequency (MHz)     | 8                        |

| Response Type                                                              | Filter Order                                  | Frequency Specifications — | Magnitude Specifications |

| Lowpass                                                                    | Specify order: 10                             | Units: MHz 💌               | Units: dB                |

| <ul> <li>◯ Highpass</li> <li>▼</li> <li>◯ Bandpass</li> </ul>              | Minimum order                                 | Fs: 20                     | Apass: 0.01              |

| ● Bandstop                                                                 | - Options                                     | Fpass: 1.5                 | Astop: 100               |

| Differentiator     Differentiator     Design Method                        | Density Factor: 16                            | Fstop: 8.5                 | Astop.                   |

| IIR Butterworth                                                            |                                               |                            |                          |

| FIR Equiripple                                                             |                                               |                            |                          |

| Input processing: Colur                                                    | nns as channels (frame based)                 |                            | sign Filter              |

| Ready                                                                      |                                               |                            |                          |

#### **Figure 9: Filter Specifications**

- 2. Close the Properties Editor for the **Digital Filter Design** instance.

- 3. Double-click the **FDATool** instance to open the Properties Editor.

- 4. Adjust the filter specifications to the following values (shown in the figure above):

- Frequency Specifications

- Units = MHz

- **Fs** = 20

- **Fpass** = 1.5

- **Fstop** = 8.5

- Magnitude Specifications

- **Units** = dB

- **Apass** = 0.01

- **Astop** = 100

- 5. Click the **Design Filter** button.

- 6. Close the Properties Editor.

Now, associate the filter parameters of the FDATool instance with the Digital FIR Filter instance.

- 7. Double-click the **Digital FIR Filter** instance to open the Properties Editor.

- 8. In the **Filter Parameters** section, replace the existing coefficients (**Coefficient Vector**) with xlfda numerator('FDATool') to use the coefficients defined by the **FDATool** instance.

| 🔀 Digital FIR Filter (Xilinx FIR Block)                                                      |

|----------------------------------------------------------------------------------------------|

| Filter Parameters<br>Coefficient Vector<br>Use FDA Tool as Coefficient source                |

| xlfda_numerator('FDATool') FDA Tool                                                          |

| Coefficient Precision Optimal values Coefficient Width : 19 Coefficient Fractional Bits : 19 |

| Interpolation Rate       1         Decimation Rate       1                                   |

| OK Cancel Help Apply                                                                         |

Figure 10: Digital FIR Filter Specifications

9. Click **OK** to exit the Digital FIR Filter Properties Editor.

In an FPGA, the design operates at a specific clock rate and using a specific number of bits to represent the data values.

The transition between the continuous time used in the standard Simulink environment and the discrete time of the FPGA hardware environment is determined by defining the sample rate of the **Gateway In**

blocks. This determines how often the continuous input waveform is sampled. This sample rate is automatically propagated to other blocks in the design by System Generator. In a similar manner, the number of bits used to represent the data is defined in the **Gateway In** block and also propagated through the system.

Although not used in this tutorial, some Xilinx blocks enable rate changes and bit-width changes, up or down, as part of this automatic propagation. More details on these blocks are found in the *Vivado Design Suite Reference Guide: Model-Based DSP Design Using System Generator* (UG958).

Both of these attributes (rate and bit width) determine the degree of accuracy with which the continuous time signal is represented. Both of these attributes also have an impact on the size, performance, and hence cost of the final hardware.

System Generator allows you to use the Simulink environment to define, simulate, and review the impact of these attributes.

10. Double-click the **Gateway In** block to open the Properties Editor.

Because the highest frequency sine wave in the design is 9 MHz, sampling theory dictates the sampling frequency of the input port must be at least 18 MHz. For this design, you will use 20 MHz.

- 11. At the bottom of the Properties Editor, set the Sample Period to 1/20e6.

- 12. For now, leave the bit width as the default fixed-point 2's complement 16-bits with 14-bits representing the data below the binary point. This allows us to express a range of -2.0 to 1.999, which exceeds the range required for the summation of the sine waves (both of amplitude 1).

| 🔀 Gateway In (Xilinx Gateway In)                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Gateway in block. Converts inputs of type Simulink integer, single, double and fixed-point to Xilinx fixed-point or floating-point data type. |

| Hardware notes: In hardware these blocks become top level input ports.                                                                        |

| Basic Implementation                                                                                                                          |

| Output Type                                                                                                                                   |

| 🔘 Boolean 💿 Fixed-point 🔘 Floating-point                                                                                                      |

| Arithmetic type Signed (2's comp) 🔻                                                                                                           |

| Fixed-point Precision                                                                                                                         |

| Number of bits 16 Binary point 14                                                                                                             |

| Floating-point Precision                                                                                                                      |

| Single Double Custom                                                                                                                          |

| Exponent width 8 Fraction width 24                                                                                                            |

| Quantization:                                                                                                                                 |

| Orruncate Round (unbiased: +/- Inf) Overflow:                                                                                                 |

| 🔘 Wrap 💿 Saturate 🔘 Flag as error                                                                                                             |

| Sample period 1/20e6                                                                                                                          |

|                                                                                                                                               |

|                                                                                                                                               |

|                                                                                                                                               |

|                                                                                                                                               |

|                                                                                                                                               |

|                                                                                                                                               |

| OK Cancel Help Apply                                                                                                                          |

Figure 11: Gateway In Properties

13. Click **OK** to close the **Gateway In** Properties Editor.

This now allows us to use accurate sample rate and bit-widths to accurately verify the hardware.

14. Double-click the **System Generator** token to open the Properties Editor.

Because the input port is sampled at 20 MHz to adequately represent the data, you must define the clock rate of the FPGA and the Simulink sample period to be at least 20 MHz.

- 15. Select the **Clocking** tab.

- a. Specify an FPGA clock Period of 50 ns (1/20 MHz).

- b. Specify a **Simulink system period** of 1/20e6 seconds.

| 承 System G            | enerator: Lab1_   | 1       |                 |             |

|-----------------------|-------------------|---------|-----------------|-------------|

| 110<br>101300<br>0001 |                   |         |                 |             |

| Compilation           | Clocking          | General |                 |             |

| Enable m              | ultiple clocks    |         |                 |             |

| FPGA clos             | ck period (ns     | ):      | Clock pin locat | tion :      |

| 50                    |                   |         |                 |             |

|                       | lock enable clear |         |                 |             |

| 1/20e6                |                   |         |                 |             |

| Perform a             | nalysis :         |         | Analyzer type   | :           |

| None                  |                   | •       | Timing          | ▼ Launch    |

| Performance           | 9 Tips Gene       | rate OK | Apply           | Cancel Help |

Figure 12: Lab1\_1 Clocking

- 16. Click **OK** to exit the **System Generator** token.

- 17. Click the **Run** simulation button to simulate the design and view the results, as shown in Figure 13: FIR Compiler Results.

Because the new design is cycle and bit accurate, simulation may take longer to complete than before.

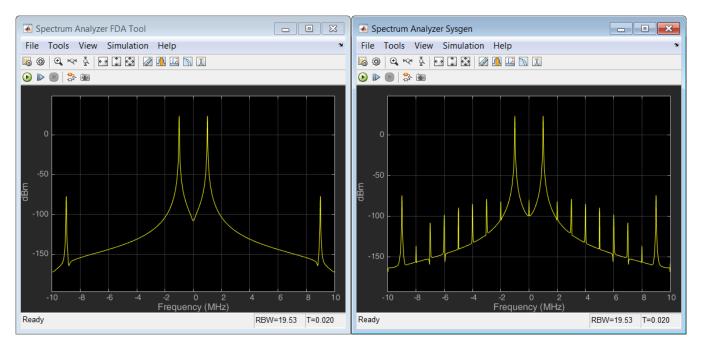

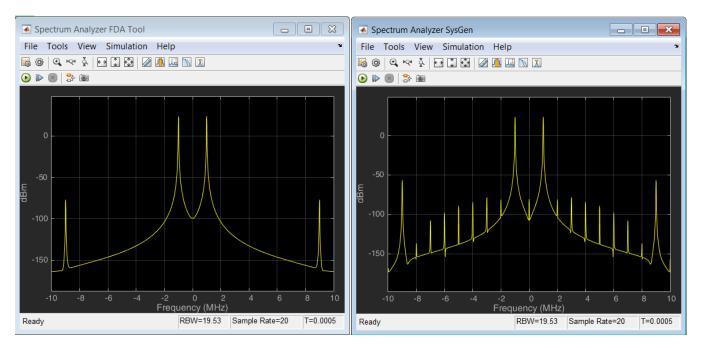

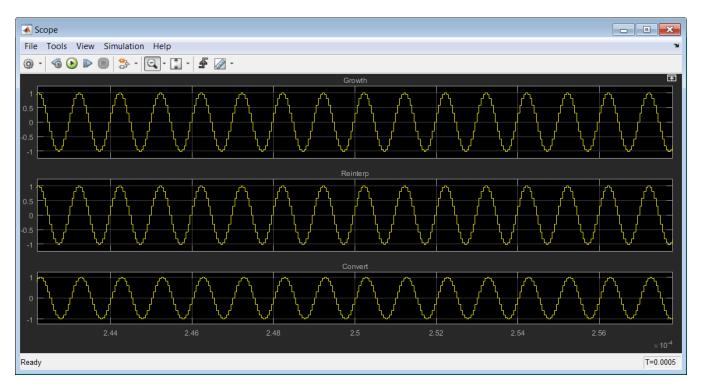

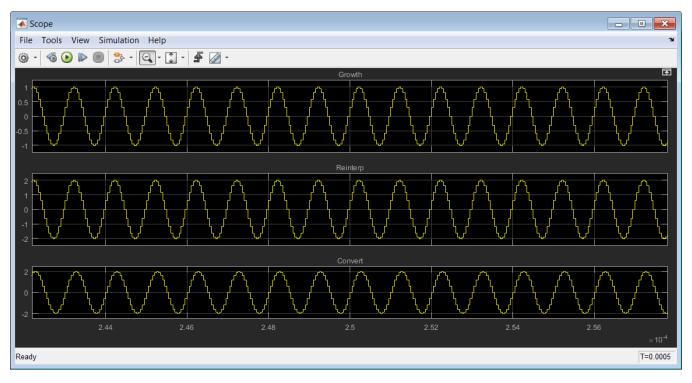

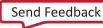

Figure 13: FIR Compiler Results

The results are shown above, on the right hand side (in the Spectrum Analyzer SysGen window), and differ slightly from the original design (shown on the left in the Spectrum Analyzer FDA Tool window). This is due to the quantization and sampling effect inherent when a continuous time system is described in discrete time hardware.

The final step is to implement this design in hardware. This process will synthesize everything contained between the Gateway In and Gateway Out blocks into a hardware description. This description of the design is output in the Verilog or VHDL Hardware Description Language (HDL). This process is controlled by the **System Generator** token.

- 18. Double-click the System Generator token to open the Properties Editor.

- 19. Select the **Compilation** tab to specify details on the device and design flow.

- 20. From the **Compilation** menu, select the **IP Catalog** compilation target to ensure the output is in IP Catalog format. The **Part** menu selects the FPGA device. For now, use the default device. Also, use the default hardware description language, VHDL.

| 承 System Ge    | enerator: Lab  | 1_1          |          |                |           |      | • 🗙        |

|----------------|----------------|--------------|----------|----------------|-----------|------|------------|

| 101300<br>0001 |                |              |          |                |           |      |            |

| Compilation    | Clocking       | General      |          |                |           |      |            |

| Board :        |                |              |          |                |           |      |            |

| > None         |                |              |          |                |           |      |            |

| Part :         |                |              |          |                |           |      |            |

| > Kintex7      | xc7k325t-3fbg6 | 576          |          |                |           |      |            |

| Compilatio     | on :           |              |          |                |           |      |            |

| > IP Catalo    | g              |              |          |                |           |      | Settings   |

| Hardware       | description    | language     | :        | VHDL libra     | ry :      |      |            |

| VHDL           |                |              | •        | xil_defaultlib |           |      |            |

| Use STD_       | LOGIC type for | Boolean or 1 | bit wide | gateways       |           |      |            |

| Target dire    | ectory :       |              |          |                |           |      |            |

| ./netlist      |                |              |          |                |           |      | Browse     |

| Synthesis      | strategy :     |              | Impler   | nentation s    | trategy : |      |            |

| Vivado Synth   | esis Defaults  | -            | Vivado   | mplementation  | Defaults  | •    |            |

| Create inte    | erface docume  | nt           | Crea     | te testbench   | [         | Mode | el upgrade |

| Performance    | e Tips Ger     | ierate       | ОК       | Apply          | Cance     | el   | Help       |

Figure 14: System Generator Token for Lab 1 Step 1

21. Click **Generate** to compile the design into hardware.

The compilation process transforms the design captured in Simulink blocks into an industry standard RTL (Register Transfer Level) design description. The RTL design can be synthesized into a hardware design. The Compilation status dialog box appears when the hardware design description has been generated.

Figure 15: Generation Complete

- 22. Click **OK** to dismiss the Compilation status dialog box.

- 23. Click **OK** to dismiss the **System Generator** token.

The final step in the design process is to create the hardware and review the results.

#### Create the Hardware and Review the Results

The output from design compilation process is written to the netlist directory. This directory contains three subdirectories:

- **sysgen**: This contains the RTL design description written in the industry standard VHDL format. This is provided for users experienced in hardware design who wish to view the detailed results.

- **ip**: This directory contains the design IP, captured in Xilinx IP Catalog format, which is used to transfer the design into the Xilinx Vivado Design Suite. Lab 8: Using AXI Interfaces and IP Integrator, presented later in this document, explains in detail how to transfer your design IP into the Vivado Design Suite for implementation in an FPGA.

- **ip\_catalog**: This directory contains an example Vivado project with the design IP already included. This project is provided only as a means of quick analysis.

You will now review the results in hardware by using the example Vivado project in the **ip\_catalog** directory.

**IMPORTANT:** The Vivado project provided in the *ip\_catalog* directory does not contain top-level I/O buffers. The results of synthesis provide a very good estimate of the final design results; however, the results from this project cannot be used to create the final FPGA.

- 24. Invoke the Vivado Design Suite: **Start > All Programs > Xilinx Design Tools > Vivado 2016.3 > Vivado 2016.3**.

- 25. Click Open Project and then navigate to the folder

C:\SysGen\_Tutorial\Lab1\netlist\ip\_catalog.

- 26. Select file lab1\_1.xpr and the Vivado IDE invokes the generated project file.

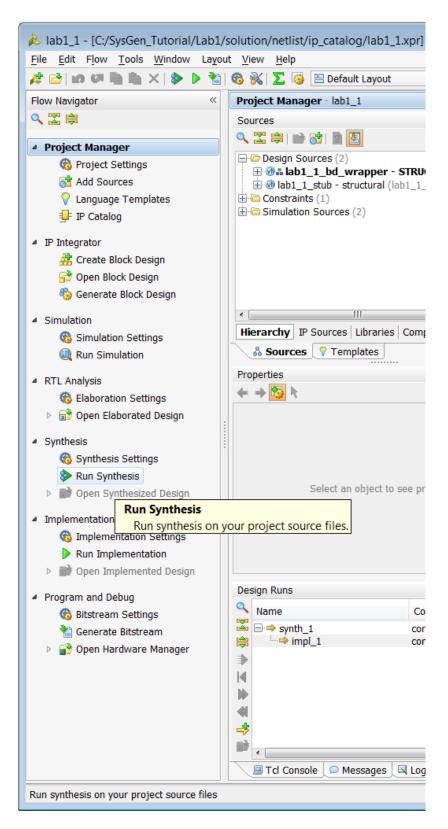

- 27. Click the **Run Synthesis** button to synthesize the design into hardware.

Figure 16: Vivado Project for Design Lab1\_1

To get an exact confirmation of the final resources and timing, you could select **Run Implementation** when the synthesis finishes. However, the results after synthesis provide a very good approximation of the final results without the additional run time of implementing a fully placed and routed design and is recommended early in the design cycle.

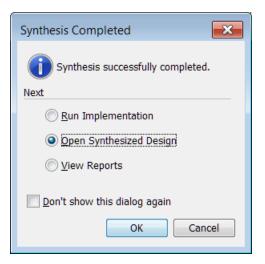

28. When synthesis completes, select **Open Synthesized Design** in the Synthesis Completed dialog box and click **OK**.

Figure 17: Synthesis Completed Dialog Box

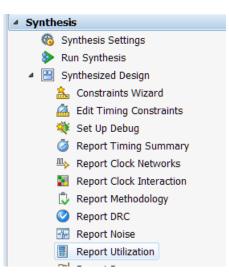

29. In the Flow Navigator, select **Synthesized Design > Report Utilization**.

Figure 18: Report Utilization in Flow Navigator

30. In the Report Utilization dialog box, click **OK**.

| 🍐 Report Utilizat     | tion          | <b>×</b>  |

|-----------------------|---------------|-----------|

| Report resource ut    | lization.     | A         |

| Results <u>n</u> ame: | utilization_1 |           |

| 🔽 Open in a new       | ta <u>b</u>   |           |

| ?                     |               | OK Cancel |

Figure 19: Report Utilization Dialog Box

31. In the **Utilization** tab of the results windows area, click **Summary** to view a summary of the resources used after the design is synthesized.

| ् 🔀 🖨 🔶 🕅 🗸          | Summary  |             |           |               |

|----------------------|----------|-------------|-----------|---------------|

| Hierarchy<br>Summary | Resource | Utilization | Available | Utilization % |

| Slice LUTs (<1%)     | LUT      | 294         | 203800    | 0.14          |

| LUT as Memory (<1%)  | LUTRAM   | 161         | 64000     | 0.25          |

| LUT as Shift Regist  | FF       | 403         | 407600    | 0.10          |

| LUT as Distributed   | DSP      | 6           | 840       | 0.71          |

| LUT as Logic (<1%)   | IO       | 53          | 400       | 13.25         |

|                      |          |             |           |               |

| utilization_1        |          |             |           |               |

Figure 20: Lab1\_1 Synthesis Results

- 32. Exit the Vivado Design Suite.

- 33. Exit the Lab1 1.slx Simulink worksheet.

### Step 2: Creating an Optimized Design in an FPGA

In this step you will see how an FPGA can be used to create a more optimized version of the same design used in Step 1, by oversampling.

- 1. At the command prompt, type open Lab1\_2.slx.

- From your Simulink project worksheet, select Simulation > Run or click the Run simulation button

to confirm this is the same design used in Step 1: Creating a Design in an FPGA.

3. Double-click the **System Generator** token to open the Properties Editor.

As noted in Step 1, the design requires a minimum sample frequency of 18 MHz and it is currently set to 20 MHz (a 50 ns **FPGA clock period**).

| 承 System Ge | enerator: Lab1_  | 2       |              |          |        |

|-------------|------------------|---------|--------------|----------|--------|

| Compilation | Clocking         | General |              |          |        |

|             |                  |         |              |          |        |

| Enable m    | ultiple clocks   |         |              |          |        |

| FPGA cloc   | k period (ns)    | :       | Clock pin lo | cation : |        |

| 50          |                  |         |              |          |        |

| Provide cl  | ock enable clear | nin     |              |          |        |

|             | system period    |         |              |          |        |

| 1/20e6      |                  |         |              |          |        |

| Perform a   | nalysis :        |         | Analyzer typ | e :      |        |

| None        |                  | •       | Timing       | •        | Launch |

|             |                  |         |              |          |        |

|             |                  |         |              |          |        |

Figure 21: Initial Lab1\_2 Clocking

The frequency at which an FPGA device can be clocked easily exceeds 20 MHz. Running the FPGA at a much higher clock frequency will allow System Generator to use the same hardware resources to compute multiple intermediate results.

4. Double-click the **FDATool** instance to open the Properties Editor.

5. Click the **Filter Coefficients** button ball to view the filter coefficients.

| Block Parameters: FDATool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Block Parameters: FDATool                                                                                                                                                                                                                                                           |                          |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| File Edit Analysis Targets View Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Help                                                                                                                                                                                                                                                                                |                          |  |  |  |

| 다 🛩 🖬 🚳 🖪   역. 🔍 호 🖾   🏗   ኬ   🕟 🖬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 🗙 🚓 🗅 🖵 🌐 🛄 💿 🔽 📉 🕅                                                                                                                                                                                                                                                                 |                          |  |  |  |

| Current Filter Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | efficients Filter Coefficients                                                                                                                                                                                                                                                      |                          |  |  |  |

| Structure: Direct-Form FIR<br>Order: 10<br>Stable: Yes<br>Source: Designed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Numerator:<br>0.0019067134188906437<br>-0.011075239432874705<br>-0.041151591448130125<br>0.03513056753261963<br>0.28878278461128692<br>0.45093247976035494<br>0.28878278461128692<br>0.03513056753261963<br>-0.041151591448130125<br>-0.011075239432874705<br>0.0019067134188906437 |                          |  |  |  |

| Store Filter<br>Filter Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                     |                          |  |  |  |

| Response Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | er — Frequency Specifications —                                                                                                                                                                                                                                                     | Magnitude Specifications |  |  |  |

| Lowpass Specific S | fy order: 10 Units: MHz 💌                                                                                                                                                                                                                                                           | Units: dB                |  |  |  |

| Bandpass   Minim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rum order Fs: 20                                                                                                                                                                                                                                                                    | Apass: 0.01              |  |  |  |

| Options -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fpass: 1.5                                                                                                                                                                                                                                                                          | Astop: 100               |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Factor: 16 Fstop: 8.5                                                                                                                                                                                                                                                               |                          |  |  |  |

| Design Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                     |                          |  |  |  |

| IIR Butterworth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                     |                          |  |  |  |

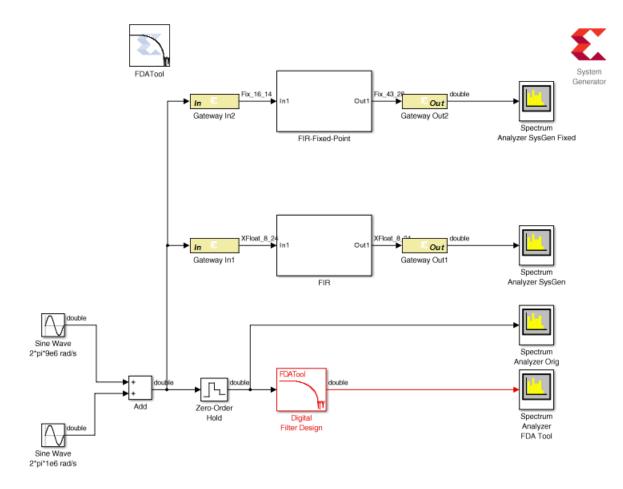

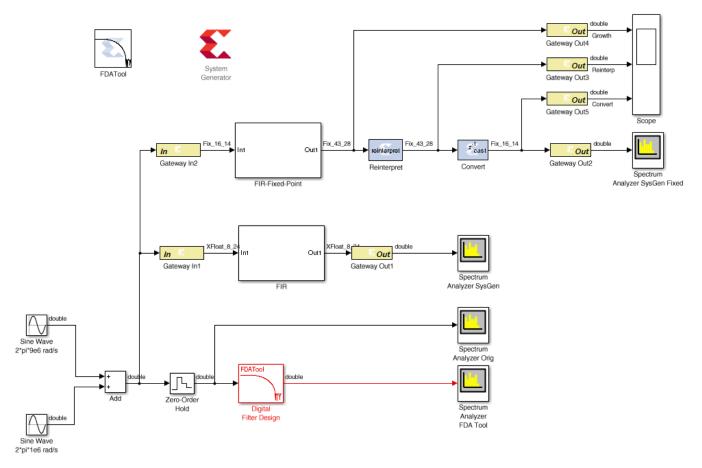

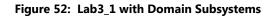

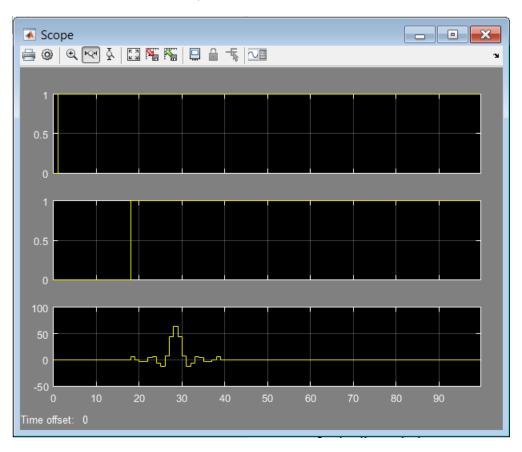

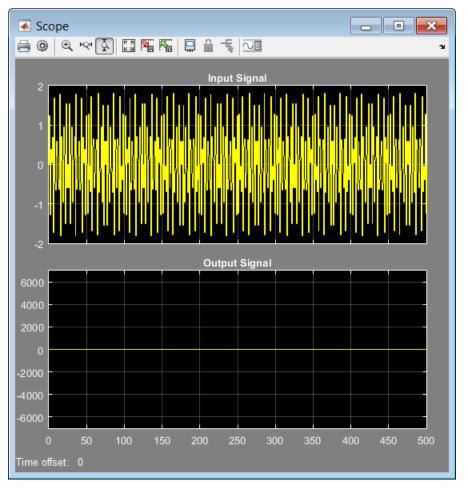

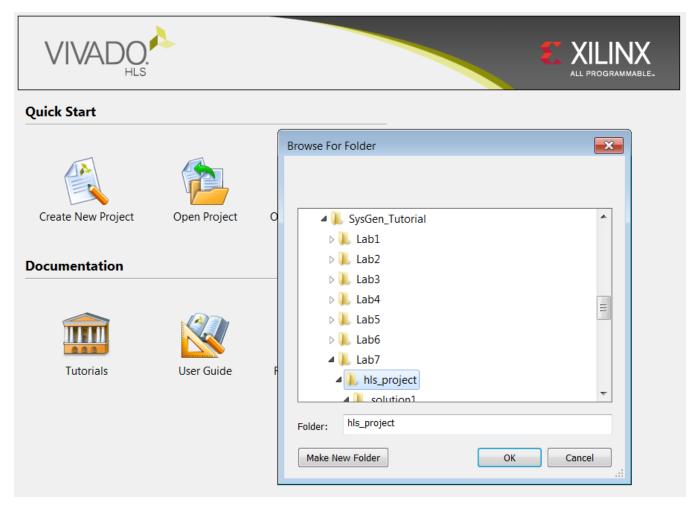

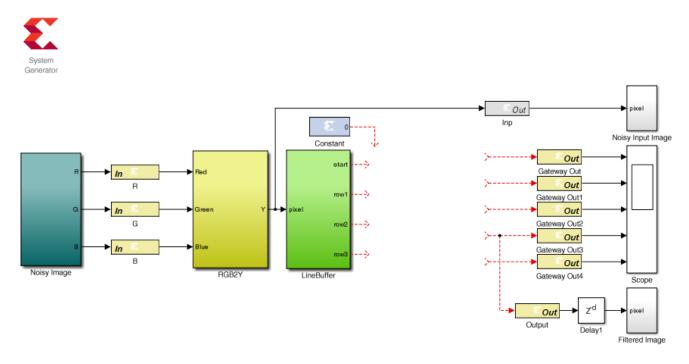

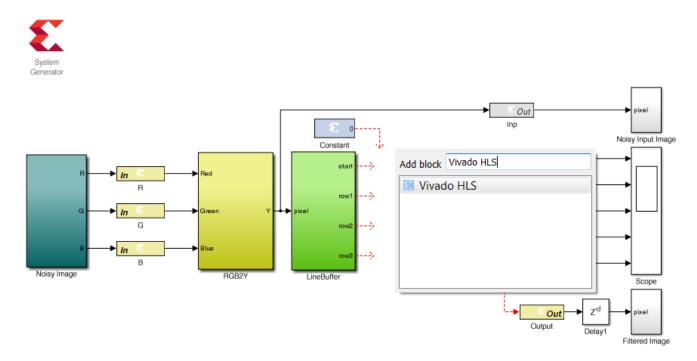

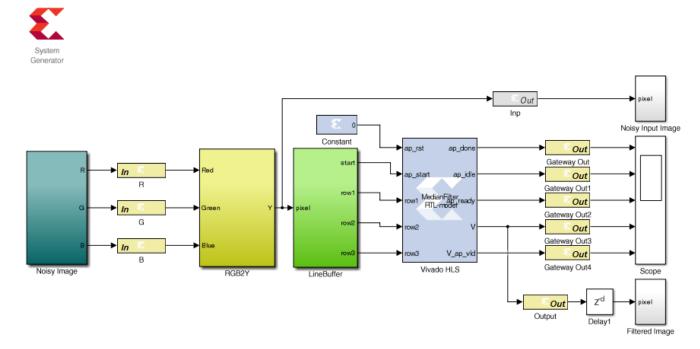

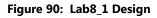

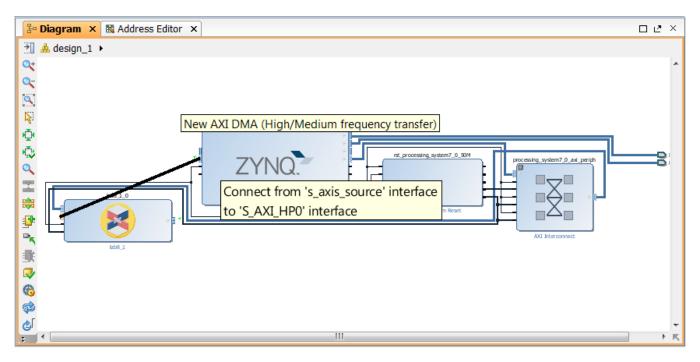

| FIR Equiripple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                     |                          |  |  |  |