# **VLSI Circuits and Systems Letter**

Volume 3, Issue 2, June 2017

# **Editorial**

#### **Feature Member**

Nagarajan Ranganathan, Distinguished University Professor Emeritus, University of South Florida

#### **Feature Articles**

- Abir J Mondal, Alak Majumder, Bidyut K bhattacharyya and Pinaki Chakraborty, A Process Aware Delay Circuit with Reduce Impact of Input Switching at GHz Frequencies

- Bipasha Nath, Alak Majumder, Monalisa Das, Abir J Mondal, Pinaki Chakraborty, Bidyut K Bhattacharyya, Voltage Keeper Based 28.27μW New Frequency Divider Circuit in 90nm Technology for Gigascale SerDes Application

- Sandeep Kakde, Yashika Gaidhani, Tejas Thubrikar, Shailesh Kamble, Nikit Shah, Power Efficient Test Pattern Generator Using Bit-Swapping LFSR Technique

- Sunil Kumar and Balwinder Raj, Estimation of Stability and Performance metric for Inward Access Transistor based 6T SRAM Cell Design using n-type/p-type DMDG-GDOV TFET

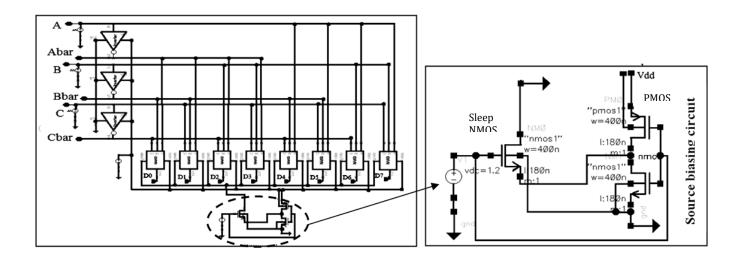

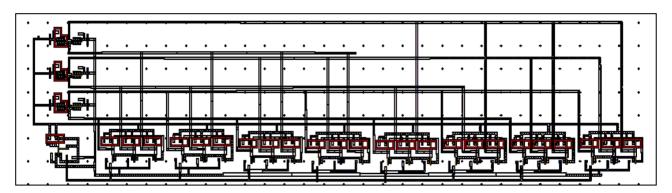

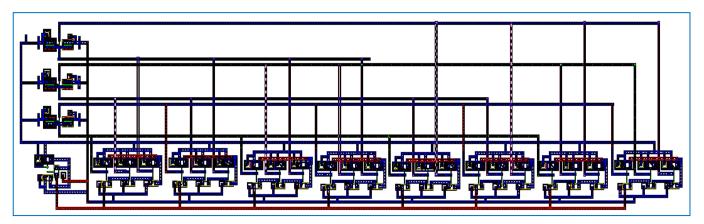

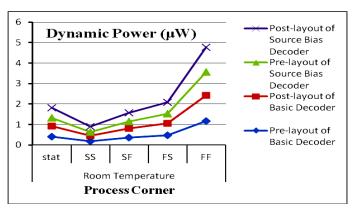

- Neha Gupta and Vaibhav Neema, Design and Analysis of DECODER circuit with Source biasing Technique for Memory array application

# **Updates**

- Upcoming conferences and workshops

- Call for papers and proposals

- TCVLSI Awards

- Funding Opportunities

- Job Openings

- Ph.D. Fellowships Available

# **Outreach and Community**

## **Call for Contributions**

# **Editorial**

The VLSI Circuits and Systems Letter is affiliated with the Technical Committee on VLSI (TCVLSI) under the IEEE Computer Society. It aims to report recent advances in VLSI technology, education and opportunities and, consequently, grow the research and education activities in the area. The letter, published twice a year, covers the design methodologies for advanced VLSI circuit and systems, including digital circuits and systems, analog and radio-frequency circuits, as well as mixed-signal circuits and systems. The emphasis of TCVLSI falls on integrating the design, computer-aided design, fabrication, application, and business aspects of VLSI while encompassing both hardware and software.

TCVLSI sponsors a number of premium conferences and workshops, including, but not limited to, ASAP, ASYNC, ISVLSI, IWLS, SLIP, and ARITH. Emerging research topics and state-of-the-art advances on VLSI circuits and systems are reported at these events on a regular basis. Best paper awards are selected at these conferences to promote the high-quality research work each year. In addition to these research activities, TCVLSI also supports a variety of educational activities related to TCVLSI. Several student travel grants are sponsored by TCVLSI in the following meetings: ASAP 2017, ISVLSI 2017, IWLS 2017, and SLIP 2017. Funds are provided to compensate student travels to these meetings as well as attract more student participation. The organizing committees of these meetings undertake the task of selecting right candidates for these awards.

This issue of the VLSI Circuits and Systems Letter highlights Prof. Nagarajan Ranganathan, Distinguished University Professor Emeritus at University of South Florida, as our "Feature Member". It also showcases the state-of-the-art developments covering several emerging areas: low-power and robust circuit design and test, emerging devices and circuits, etc. Professional articles are solicited from technical experts to provide an in-depth review of these areas. The articles can be found in the section of "Features Articles". In the section of "Updates", upcoming conferences/workshops, call for papers and proposals, funding opportunities, job openings and Ph.D. fellowships are summarized. Finally, a dedicated section of "Outreach and Community" summarizes our outreach activities.

We would like to express our great appreciation to all Associate Editors (Hideharu Amano, Mike Borowczak, Prasun Ghosal, Shiyan Hu, Michael Hübner, Helen Li, Anirban Sengupta, Jawar Singh, Saket Srivastava, Yiyu Shi, Yasuhiro Takahashi, Jun Tao, Himanshu Thapliyal and Qi Zhu) for their dedicated effort and strong support in organizing this letter. The complete editorial board information is available at: <a href="https://www.computer.org/web/tcvlsi/editorial-board">https://www.computer.org/web/tcvlsi/editorial-board</a>. We are thankful to our web chair Mike Borowczak, for his professional service to make the letter publicly available on the Internet. We wish to thank all authors who have contributed their professional articles to this issue. We hope that you will have an enjoyable moment when reading the letter! The call for contributions for the next issue is available at the end of this issue and we encourage you to submit articles, news, etc. to an associate editor covering that scope.

Saraju Mohanty Chair TCVLSI and Editor University of North Texas

Xin Li TCVLSI Editor Duke University and Duke Kunshan University

# **Feature Member**

Nagarajan Ranganathan Distinguished University Professor Emeritus Computer Science and Engineering Department College of Engineering University of South Florida

Nagarajan "Ranga" Ranganathan (S'81-M'88-SM'92-F'02) received the B.E. (Honors) degree in Electrical and Electronics Engineering from National Institute of Technology, Trichy, India, 1983, and the Ph.D. degree in Computer Science from the University of Central Florida, Orlando in 1988. He is a Distinguished University Professor Emeritus of Computer Science and Engineering at the University of South Florida, Tampa. During 1998-99, he was a Professor of Electrical and Computer Engineering at the University of Texas at El Paso. His research interests include VLSI System Design, VLSI Design Automation, Multimetric optimization in Hardware and Software Systems, Computer Architecture, Reversible Logic and Quantum Computing. He has developed many special purpose VLSI circuits and systems for computer vision, image and video processing, pattern recognition, data compression and signal processing applications. He has developed several VLSI CAD algorithms based on decision theory, game theory, auction theory and Fuzzy modeling. He has co-authored over 310 publications in refereed journals and conferences, five book chapters and co-owns twelve U.S. patents and three pending. He mentored and served as major professor for 27 PhD and 69 MS theses students to graduation. He has edited three books titled VLSI Algorithms and Architectures: Fundamentals, VLSI Algorithms and Architectures: Advanced Concepts, IEEE CS Press, 1993, VLSI for Pattern Recognition and Artificial Intelligence, World Scientific Publishers, 1995 and co-authored a book titled, Low Power High Level Synthesis for Nanoscale CMOS Circuits, Springer, June 2008.

Dr. Ranganathan was elected as a Fellow of IEEE in 2002 for his contributions to algorithms and architectures for VLSI systems. He was elected Fellow of AAAS in 2012. He is a member of the IEEE, IEEE Computer Society, IEEE Circuits and Systems Society and the VLSI Society of India. He has served on the editorial boards for the journals: Pattern Recognition (1993-97), VLSI Design (1994-1998), IEEE Transactions on VLSI Systems (1995-97), IEEE Transactions on Circuits and Systems (1997-99), IEEE Transactions on Circuits and Systems for Video Technology (1997-00), IEEE Transactions on Computers (2008-12), IEEE Transactions on CAD (2008-10) and ACM Transactions on Design Automation of Electronic Systems (2007-09). He was the chair of the IEEE Computer Society Technical Committee on VLSI during 1997-01, served on the steering committee of the IEEE Transactions on VLSI Systems during 1999-01 and 2007-2010, the steering committee chair during 2002-03 and the Editor-in-Chief (EiC) for two consecutive terms during 2003-07. He served as the program co-chair for ICVLSID'94, ISVLSI'96, ISVLSI'05, and ICVLSID'08 and as general co-chair for ICVLSID'95, IWVLSI'98, ICVLSID'98, ISVLSI'05, ISVLSI'09 and ISVLSI'12. He served on technical program committees of international conferences including ICCD, ICPP, IPPS, SPDP, ICHPC, HPCA, GLSVLSI, ASYNC, ISQED, ISLPED, CAMP, ISCAS, VLSID, MSE and ICCAD.

Dr. Ranganathan received the USF Outstanding Research Achievement Award (2002), USF President's Faculty Excellence Award (2003), USF Theodore-Venette Askounes Ashford Distinguished Scholar Award (2003), SIGMA XI Scientific Honor Society Tampa Bay Chapter Outstanding Faculty Researcher Award (2004), Distinguished University Professor honorific title and the university gold medallion honor (2007), USF Outstanding Undergraduate Teaching Award (2009), Recipient of three Best Paper Awards at the Intl. Conf. on VLSI Design (1995, 2004 and 2006) and the IEEE Circuits and Systems Society VLSI Transactions Best Paper Award (2009). He was elected as the Fellow of Academy of Advances in Science (AAAS) in 2013. Dr. Ranganathan Served as the Faculty Liaison on the Academics and Campus Environment (ACE) Group of the University of South Florida Board of Trustees (2011-2013) and retired with Emeritus status in 2016.

# Q1. Tell us a little about your research area and what motivated you to get into it?

With a bachelor degree in electrical and electronics engineering, I had developed strong interest in logic design and circuit theory. Although I did my Ph.D. in computer science in a program that was basically theoretical computer science located in the College of Arts and Sciences while the computer engineering department was housed in College of Engineering, I was fascinated by VLSI circuits and systems. This was in early 1980's as VLSI was becoming mainstream technology. On the other hand, theory of algorithms and automata theory were favorites while as student. The introduction to Professor Amar Mukherjee just made the clear decision to work in VLSI algorithms and architectures for specific applications that were purely implemented as software algorithms for applications needing intensive and on-the-fly computations in real-time. The field of ASICS was just then emerging with very little work published. At the time CMOS was just emerging and nMOS was still the common technology. The idea was from implementing algorithms for processing in programmable machines coded in high level languages and as assembler routines on microcontroller and microprocessors based on CISC towards implementing compute intensive software algorithms as hardware algorithms mapped onto application specific integrated circuits and systems.

My initial goal was to implement an operating system as hardwired ASIC in 1984, at a time when researchers were still working on hardware memory management controllers. When approached Professor Manichandy at UTA at that time for his opinion he said, "it is a great idea but not for a single person attempting to accomplish such a massive task within Ph.D research", warning that one could get stuck without completing the degree for many years. Thus, the dissertation research was narrowed down to designing hardware algorithms for data compression. After starting my faculty career, I worked on VLSI algorithms, architectures, circuits and systems for image processing, computer vision, signal processing and communications, neural networks and expert systems etc. The strategy was to convert software algorithms into circuits and where possible develop new algorithms that more naturally allowed hardware design. The mapped algorithms had to use extensive pipelining and parallelism for speed and maximum possible logic minimization at minimal power and energy consumption. The objective was to get rid of the overheads involved in the traditional software having to be compiled and run on programmable processors and realize those as special purpose VLSI circuits. Such a circuit for a single application is possible to obtain the maximum possible speed and avoids the complex control in needed in programmable processors and microcontrollers. This field of ASICs was redefined as embedded circuits and systems since ASICs were primarily embedded within application systems in the 90's.

In 1993, Professor Don Bouldin started the IEEE Transactions on VLSI systems and a few of my papers appeared in the early issues in that year. TVLSI became the primary platform for reporting my works in that appropriate journal for VLSI design of circuits and systems. The VLSI mainstream community was focused on CAD with TCAD, and grew into a massive field. Before TVLSI, I was trying hard to find suitable conferences and journals to publish our work. Having worked with students on a huge number of problems in a wide variety of applications and with computer science background I started working in CAD area, being late in the game, found it hard to obtain grants in CAD, but continued to work on problems like gate as well as wire sizing and optimization, synthesis, power estimation and optimization, leakage reduction etc., applying modeling techniques from decision theory, game theory, auction theory, Bayesian networks etc. As speculations indicated towards quantum computing, reversible logic was my next interest and at the time only reversible logic designs for some logic functions and adders were found in the literature. Thus, our group focused and developed novel reversible logic gates and circuits for a wide variety of arithmetic functions like multipliers, dividers, shifters and circuits for smartcards etc. Most recent work has focused on techniques for data security in clouds and big data systems and the pending patents are currently getting attention from the industry.

#### Q2. What are some of your proudest accomplishments?

I think the biggest accomplishment is the mentoring of research students and seeing them establish significantly in their chosen fields. Examples in academia are Professors Vijaykrishnan Narayanan at Penn State, Saraju Mohanty at University of North Texas, Rajarathnam Chandramouli at Stevens Institute of Technology, Matt Morrison at Ole Mississippi, Sanjukta Bhanja now an Associate Dean at USF etc. In the industry, many including Ashok Murugavel at Intel, Shankar Arumugavelu now CIO and Chief Executive Vice President at Verizon and several CTO's of small companies. Several

students were employed in various industries including Intel, Samsung, TI, LSI logic, Fujitsu, Cadence, Synopsys, Juniper and the like. Thus, training students towards successful careers is the most rewarding accomplishment as part of the academic profession. The Best Paper awards won by my students come to my mind. In terms of my research all the credit can be attributed to my <u>96 research students</u>. The application of modeling techniques from vastly different other fields to VLSI CAD and developing novel VLSI circuits and systems for pattern matching and recognition, development of a lossless data compression method that outperformed all the versions of the original JPEG standard within months after it was released and further the VLSI circuit for JPEG standard named JAGUAR can be considered as significant accomplishments. The idea of applying game theory to VLSI CAD won several best paper awards.

#### Q3. How do you see your research field shaping up and what are the major directions?

The future is promising due to the proliferation of applications needing real time responses and the progress in nanotechnology from materials to devices is key to designing new hardware circuits and systems based on those devices. New architectures and circuits as well as CAD will need to be realized to suit and exploit the advantages of nano devices towards nano computing systems.

### Q4. Can you talk a little about the history of TCVLSI? What motivate you to initialize TCVLSI?

IEEE-CS Annual workshop on VLSI was initiated due to researchers like Don Bouldin, Amar Mukherjee, Richard Newton, Jan Rabaey, P. A. Subramanyam of Bell Labs etc. Since the mid-eighties, while as a student, I began volunteering in this workshop every year. A few years this workshop was dormant. In 1988, I approached Professor Amar Mukherjee and we jointly revived this annual meeting and later renamed it as ISVLSI. Around 2012, my former student Prof. Vijay Narayanan at Penn State took over as the steering committee chair. TCVLSI was formed around late eighties with its major activities being ISVLSI, IEEE Transactions on VLSI systems, etc. Thus. I have been involved with and played leadership role in TCVLSI and ISVLSI for over 25 years.

### Q5. What advice would you give to junior researchers and graduate students?

In general, it is important to keep abreast of the latest advances in the research field through regularly attending internationally reputed major conferences and reading journals. It is important to watch out for emerging trends. The right approach is to choose problems that have impact in the future, at least in the next ten years. This allows for the research to be relevant also for seeking sponsorship funding. In academia, it is important to involve graduate students with fresh minds and mentor them to become future researchers. Certainly, they can be encouraged and inspired through making sure their papers are well written and they are the primary authors. This is a fundamental responsibility of an academic researcher. Based on the students' goals about academia or industry, the research area and problems should be defined differently and the nature of entire research should be tuned accordingly. Strict discipline and following milestones are key to success. The graduate students should be trained to work well in a team as well as being a self-starter of research initiatives. Any researcher needs passion for chosen field, strong focus, willingness to learn, acceptance of intermediary failures such as rejection of a submission and concentrated hard work to achieve success. Also, quality assurance is to be verified through publishing only in topmost journals such IEEE and ACM transactions. And avoiding secondary ones. Also, a graduate student must learn the entire current state-of-the-art in the entire chosen field.

### O6. What profession would you be in if you weren't in this field?

I entered electrical engineering and computer science being attracted to mathematics and technology at a time when NASA was accomplishing landing on the moon and the space shuttle programs. If that was not my path, I would have pursued medical research which is a major need to be constantly advancing the field of medicine to solve health problems vital to human life.

## Q7. Any final thoughts?

I loved my academic career of research and teaching that I have pursued for about 30 years but it came to an abrupt ending due to accidents resulting in major health issues. Else I have no regrets about my career. My former students that I mentored and trained to be researchers have been turning out to be outstanding successful researchers and hold important positions and status in their careers. They keep in touch with me and keep me informed of their progress in life and career. It has been a very rewarding and satisfying experience to have mentored 96 graduate students in research. The University of South Florida has grown from not being ranked to get within the top 30 research institutions as ranked by the National Research Council during my tenure and thus I enjoyed being a part of it. I became one of the youngest Distinguished University Professor at USF. Thus, I have always strived to do my best at USF.

# **Feature Articles**

# A Process Aware Delay Circuit with Reduce Impact of Input Switching at GHz Frequencies

Abir J Mondal<sup>1</sup>, Alak Majumder<sup>1</sup>, Bidyut K bhattacharyya<sup>2</sup> and Pinaki Chakraborty<sup>3</sup>

- <sup>1</sup> Department of Electronics and Communication Engineering, National Institute of Technology, Arunachal Pradesh, India

- <sup>2</sup> Department of Electronics and Communication Engineering, National Institute of Technology, Agartala, India

- <sup>3</sup> Department of Basic and Applied Science, National Institute of Technology, Arunachal Pradesh, India

**Abstract** – Conventional delay circuits with one input cannot perform the task of generating delay between the input and output while operated at GHz frequencies. In addition, by switching 1 GHz signal at the input of conventional delay circuits, the signal suffers from distortion inside the chip. Whereas, the use of a resistance can control the delay and so becomes the cause of voltage loss inside the chip. The resistance also acts as a filter, which eliminates higher frequency signals and suppresses the operating frequency of a signal. Considering all these pros and cons, this work suggests a method of designing a differential scheme made of two identical drivers and a comparator for generation of delay signal from the original signal, thus enhancing the operating frequency from 1 Gbps to 4 Gbps at 180 nm process technologies.

#### 1. Introduction

The sensitivity of the signal delay due to varying voltage at the input pin of I/C chip is significant while designing delay circuit for application. Later, the advancement of VLSI technology does not allow the data rate for server to increase dramatically in terms of Gbit/sec while communicating between two chips using copper interconnect (channel) [1]. The use of such interconnects results in insertion losses in the channel [2] thereby causing signal distortion. In order to reconstruct signal, one requires generation of various delay schemes inside the chip [3] at higher speed. It has been observed that even inside the chip the signal strength gets destroyed because of the metal line resistance and the input capacitance of the device the signal is driving. Use of additional resistance for the generation of signal delay destroys the signal integrity and reduces the amplitude of a signal propagating inside a chip. On the contrary, the conventional delay circuits which are designed inside the chip suffer from distortions and significant signal loss when operated at gigahertz ranges. Such deterioration occurs due to fluctuating voltage at the input of a chip, resulting from an external source using another chip.

Inverter chains and RC circuits [4] are often used in peripheral circuit design in order to generate a desired time delay though suffering from large die area and severe switching power loss [5]. On the other hand, current starved delay [6] controls the delay time by manipulating charge/discharge current, thus providing an advantageous longer delay time. Bazes [7] uses voltage source to control the delay time. A thyristor based delay element [8] is similar to current starved one and uses current mirror to adjust delay time. However, by changing the position of current controlling transistor in the current starved circuit, it is possible to have an alternative delay gate, which is called output split [9]. The tunable delay element [10] turns to be low power in nature. In all the above stages, the problem is to control the delay, since the signal strength reduces and makes such delay control difficult for input to switch at gigahertz ranges. As a remedial measure, the authors have described and analyzed an alternate structure of delay circuit based on differential signaling approach. The simulation set up described ultimately provides a precise delay time following elimination of signal distortions and loss associated with the conventional delay circuits.

#### 2. Conventional Delay Circuits

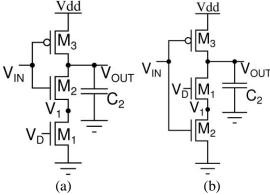

The increase in data rate to gigahertz ranges makes it difficult to design circuits to operate at higher frequencies inside as well as outside the chip. Externally it is controlled by the channel characteristics and inside the chip it is controlled by RC delays, both generating a loss in the range of 60-120 db while operating at 1-10 Gbit/sec data rate. When the slew rate at input is fast or switched at 1 GHz, the delay circuits shown in Figure 1 [6, 9] suffer from significant signal losses. Depending on the channel characteristics, the edge rate of the input,  $V_{IN}$  in Fig. 1 emerging from another chip may vary. The rise time for the signal entering  $V_{IN}$  has to be smaller than 100 ps in order to operate at 1 GHz and that causes

problem for a conventional delay circuit. When the pulse at the input switches from low to high,  $M_2$  turns on and starts discharging the load capacitance,  $C_2$ . The on resistance,  $R_1$  of  $M_1$  controls the discharging capacity by controlling the discharge current. But the charging time of the capacitor is not controlled by

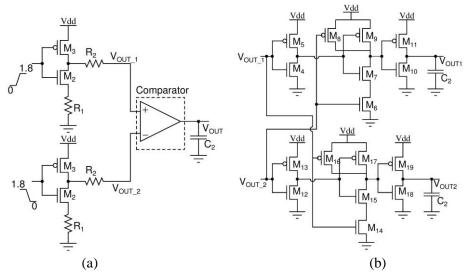

Figure 1: Schematic diagram of the delay gate.

any current control transistor like  $M_1$ .  $R_1$  is controlled by varying the input voltage  $V_D$  at the transistor  $M_1$  in Figure 1. Therefore, designing of such chip requires two sources of power supply, one Vdd and the other  $V_D$  (variable) for controlling the effective " $R_1$ ".

To estimate the effective  $R_1$ , the discharging current is first obtained using simulation. Thereafter, Eq. (1) is used to determine the switching time.

$$\frac{dI}{dt} + \frac{I}{R_1 \times C_2} = 0 \tag{1}$$

where  $C_2$  denotes the load capacitance and I(t) depicts the discharging current at a given time t through  $R_1$ . Once the current vs. time is plotted,  $R_1$  is determined from the time constant  $(\tau)$  of the said plot using Eq. (2)

$$R_1 \times C_2 \approx \tau$$

(2)

For  $C_2=1$  fF and Vdd=1.8 V, the value of  $R_1$  using Eq. (2) and Eq. (1) from data fit, appears to be 360 k $\Omega$ . Now, the effect of high value of  $R_1$  is noted when the signal arrived at the input pad with some slew rate which may be expressed as  $\frac{dV_{IN}}{dt}$ . Since the pulse arises at the input, current flows towards supply voltage followed by a gradual charging and discharging. On the other hand, when  $\frac{dV_{IN}}{dt}$  is high and  $R_1$  approaches infinity,  $C_2$  instead of being discharged gets charged by a current flowing through input capacitance. Thus, the generation of the delay by controlling the current through the ground path using the NMOS gate and using a separate power supply happens to be a problem.

#### 3. Proposed Delay Circuit

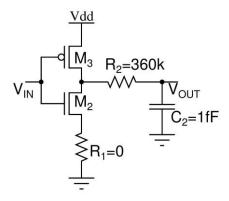

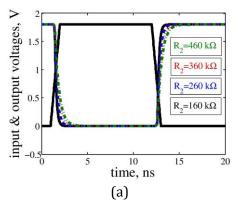

To counter the problematic issues associated with [6, 9] at higher frequencies, the authors propose to design a circuit as described in Figure 2. Here, the extra power supply is discarded and the NMOS gate is connected directly to the ground, which translate to  $R_1$ =0 or no transistor, to control the ground current. Introduction of an additional resistance  $R_2$  shows that the delay is possible with larger values of  $R_2$ . But the signal amplitude reduces drastically as  $R_2 \rightarrow$  infinity. Therefore, it is irrelevant whether a transistor or a pure resistor is included in the conventional delay circuit in Figure 1. In Fig. 2 when the input switches from high to low  $C_2$  gets charged though PMOS  $M_3$ . During low to high switching,  $M_2$  turns on creating a conducting path from output to ground, but  $C_2$  remains charged for a moment. The resistance  $R_2$  controls the discharging rate through  $M_2$  and provides protection during switching without overcharging the load capacitance. The resistor actually prevents the flow of current towards supply when switching occurs rapidly.

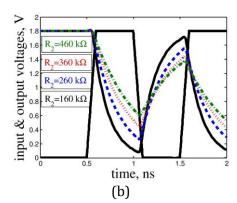

Further to address an additional issue, an initial pulse having a switching frequency of 20 ns (50 MHz) is applied at the input of Figure 2 and the value of  $R_2$  is taken same as  $R_1$ . Keeping all the transistor dimensions identical, Figure 3a illustrates that the input/output waveform corresponding to 20 ns (0.1 Gbit/sec) switching frequency changes with the

change in  $R_2$ , thereby causing a precise delay. Whereas, by reducing the switching frequency to 1 ns (equivalent to approximately 1 Gbit/sec data rate), the corresponding output waveforms, as shown in Figure 3b, suffer from significant signal distortion. The distortion is much more significant for higher  $R_2$  because  $C_2$  does not charge and discharge completely due to large RC time constant  $(\tau)$ .

Figure 2 Schematic of the proposed delay circuit.

Figure 3 a) Plot of input and output voltages corresponding to 20 ns switching frequency and different R<sub>2</sub> and b) Plot of input and output voltages corresponding to 1 ns switching frequency and different R<sub>2</sub>.

To avoid signal loss inside the chip due to fast switching and to have full voltage swing at output, Figure 4a suggests a differential signaling technique consisting of two identical driver blocks and a comparator and aiming to generate delay between two signals. The driver blocks correspond to the design block shown in Figure 2 and the comparator is realized using the circuit given in Figure 4b. At first, input pulses switching at gigahertz frequencies are applied to the two driver blocks in low to high and high to low form. The corresponding outputs though suffering from significant losses acts as an input to the comparator. An ideal comparator outputs logic 1 if  $V_{out_{-1}} - V_{out_{-2}} > 0$  or else logic 0. On comparing the two inputs, the resulting outputs are displayed at  $V_{out_{-1}}$  and  $V_{out_{-1}}$ . Further, the resulting outputs at  $V_{out_{-1}}$  and  $V_{out_{-2}}$  generate an eye, the amplitude of which decides the correctness of the comparator output. The comparator circuit compares the inputs in the form of eye and gives full voltage swing. The proposed approach also eliminates the common mode noise appearing in the input, thus even operating at gigahertz ranges removes the aberrations at the output. This allows input of small amplitude to get sampled accurately as long as the eye generated at the output of two drivers has a voltage swing of 0.5 V. Finally, irrespective of the previous pulse whether appearing as 1 or 0, evaluating signal integrity of thousand of pulses at a glance is no problem.

#### 4. Results and Analysis

The proposed delay circuit and the circuit developed using differential signalling approach are simulated using TSMC 180 nm technology in LT spice. Although, the use of PTM [11] transistor models results in better performances compared to the 180 nm technology, the authors aim at acquiring maximum operating frequency as well as performance achievable with 180 nm technology. The delay circuit in Fig. 2 is simulated to obtain the discharging current  $5 \times 10^{-6} \, \mu A$ .

Thereafter, Eq. (1) and Eq. (2) are used along with the estimated current to determine the effective resistance  $R_1$  i.e. 360  $k\Omega$ . To get rid of the problems associated with the conventional delay circuit,  $R_1$  is fixed at zero and a resistance  $R_2$  of 360  $k\Omega$  is inserted between output and load capacitance. Using Eq. (3), the total resistance offered during discharging becomes 400  $k\Omega$ . Since the initially chosen  $R_2$  is 360  $k\Omega$ , the resistance offered by  $M_2$  ( $R_T$ ) comes out to be 40  $k\Omega$ .

Figure 4 Schematic of the a) proposed delay circuit using differential signalling approach and b) conventional comparator circuit

$$V = V_0 \left\{ 1 - e^{\frac{-t}{\tau}} \right\} \tag{3}$$

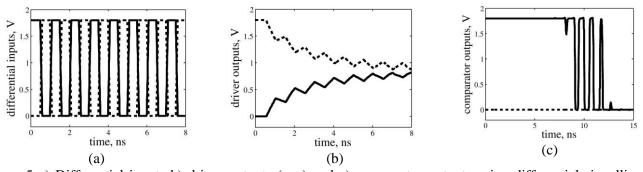

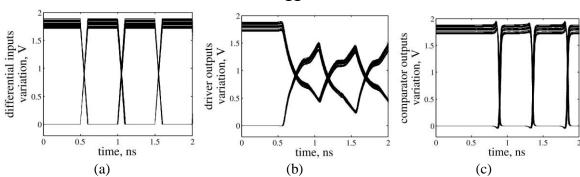

To remove the signal loss associated with 1 GHz switching frequency and to attain full voltage swing at the output, differential inputs are applied to the driver blocks of Figure 4a in a manner shown in Figure 5a. Thus, Figure 5b depicts that with  $R_2$ =360 k $\Omega$  the driver outputs do not overlap. Further, there is no eye and the comparator outputs in Figure 5c get corrupted. Under this circumstance, the amplitude of the eye needs to be adjusted to develop full and correct voltage swing at the comparator outputs. So, the value of  $R_2$  is carefully adjusted and it is observed from Figure 6a that with 1 gigahertz switching frequency and  $R_2$ =100 k $\Omega$  an eye with certain amplitude is appearing at the driver outputs.

Figure 5 a) Differential inputs b) driver outputs (eye) and c) comparator outputs using differential signalling approach with  $R_2$ =360 k $\Omega$ .

Figure 6 Plot of a) driver outputs (eye), b) comparator outputs using differential signaling approach with  $R_2=100 \text{ k}\Omega$ , c) driver outputs (eye) and d) comparator outputs using differential signaling approach with  $R_2=30 \text{ k}\Omega$

As illustrated in Figure 6b, the eye amplitude is not enough for the comparator to generate correct and full voltage swing. The value of  $R_2$  is again adjusted and Figure 6c depicts that with  $R_2$ =30 k $\Omega$  an eye with appropriate amplitude is formed at the driver outputs. Figure 6d illustrates the corresponding full voltage swing at the comparator outputs. It is also apparent from the above that the generated eye must have a voltage drop of 0.5 V so that the comparator gives full voltage swing. The signals that are studied and sampled are S = 10101010... and  $\overline{S} = 0101010...$

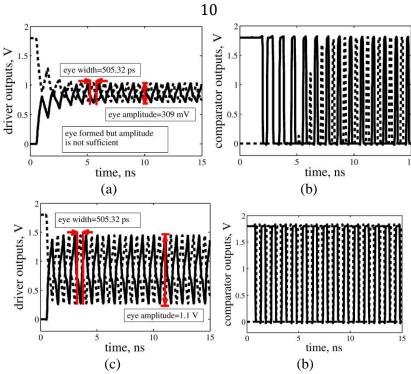

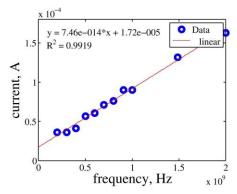

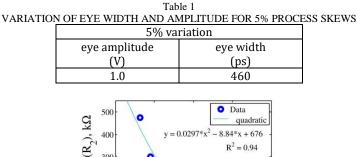

The power drawn by the proposed delay circuit in Fig. 4a as a function of frequency is shown in Figure 7. It is interesting to note that the dynamic current for the proposed device, designed at 180 nm process technology and operating at 1.8 V, comes out to be around 74.4  $\mu A$  for 20 transistors accommodated in about 39.2  $\mu m^2$  area. The intercept of about 17.7  $\mu A$ , corresponds to the leakage current for this set-up.

The input signal at the receiver due to process skew is shown in Figure 8a. It has been assumed that the power supply is fluctuating between 5 % of the allowed Vdd specification. Further, there are jitter also appearing within 5% due to crosstalk and other issues involving the rise and fall time of the signal. Using Monte Carlo experiment, the eye diagram is plotted in Figure 8b to indicate that the eye is still open with some marginal loss. Following noise and jitter, eye height and eye width varies in a manner given in Table 1. In spite of marginal loss, a clear comparator output is evident in Figure 8c.

Figure 7 Plot of current drawn by all devices inside the silicon chip, for different switching frequencies

Figure 8 Plot of a) differential inputs b) driver outputs and c) comparator outputs variation for process skew of 5%

Figure 9 Plot showing the change in R<sub>2</sub> with scaling of process file

The plot of resistance ( $R_2$ ) versus channel length in Figure 9 illustrates how the resistance value changes as a function of various process files, while keeping the operating frequency fixed at 1 GHz. It is important to note that as the channel length is reducing, the value of  $R_2$  is increasing and this attributes to larger current being drawn here. Therefore, an increase in  $R_2$  is essentially required to keep the delay time fixed. On the other hand, to reduce the delay time  $R_2$  has to be fixed. Thus, with various channel lengths one requires different values of resistances to obtain a constant delay of 310 ps as reported in the Table 2. The curve in Figure 9 portrays a constant delay of 310 ps, which is independent of the channel length or the scaling of process file.

$\begin{array}{c} \text{Table 2} \\ \text{CHANGE IN } R_2 \text{ WITH TECHNOLOGY SCALING} \end{array}$

| technology | process       | delay | R <sub>2</sub> | eye   | eye       |

|------------|---------------|-------|----------------|-------|-----------|

| (nm)       | & temperature | (ps)  | $(k\Omega)$    | width | amplitude |

|            | (°C)          |       |                | (ps)  | (V)       |

| 180        | TT at 27      | 310   | 30             | 498.4 | 1.1       |

| 130        | TT at 27      | 310   | 98             | 457.6 | 0.75      |

| 90         | TT at 27      | 310   | 130            | 421   | 0.68      |

| 65         | TT at 27      | 310   | 180            | 418.5 | 0.52      |

| 45         | TT at 27      | 310   | 300            | 419.5 | 0.54      |

| 32         | TT at 27      | 310   | 475            | 368   | 0.40      |

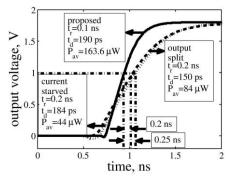

### 5. Comparison with Conventional Circuits

In order to compare the proposed delay circuit with CSI and OSI circuits discussed in Figure 1, the three delay circuits are simulated using TSMC 180 nm technology in Lt spice. The W/L ratios of the transistors,  $R_1$  and  $R_2$  of all three circuits are chosen with an aim to develop approximately equal delay. Figure 10 shows the output of the three delay circuits. Though the performance of a delay circuit is temperature dependent, in most applications a very precise and stable delay is always desirable. Accordingly, the three delay circuits are simulated at two different temperatures and the corresponding results are given in Table 3. Data reported in this table clearly indicate that the proposed circuit has least sensitivity to temperature variation.

# Table 3 EFFECTS OF TEMPERATURE ON THE THREE DELAY CIRCUITS

| methodology     | TT at 27°C | TT at 90°C | % of change |

|-----------------|------------|------------|-------------|

| Current starved | 299.62 ps  | 320.7 ps   | 6.5         |

| inverter        |            |            |             |

| Output split    | 302.77 ps  | 311.8 ps   | 2.9         |

| inverter        |            |            |             |

| Proposed        | 310 ps     | 315.0 ps   | 1.5         |

Figure 10 Output of the three different delay circuit

Further to compare with CSI and OSI, the proposed delay circuit consumes higher power which appears to be around  $163.6~\mu W$  at 250~MHz. The dynamic and static power components constitute  $133~\mu W$  and  $30.6~\mu W$ , respectively. With regard to estimation of delay time, reference may be drawn to Figure 10 again, which shows that the time to reach 1 V is 0.95~ns for the proposed circuit in comparison to nearly 1.1~ns for CSI and OSI. Thus the proposed method achieves a gain of about 0.25~ns, which may cause the dynamic power to increase marginally. The rise time of the proposed design is much less and corresponds to operating frequency increase by 14%, i.e. from 1.05~GHz to 0.91~GHz.

### 6. Conclusions

At high speed, the non-differential signal lines due to channel characteristics when arrives at the receiver, the signal amplitude gets distorted. Further, considering arrival of a signal of reduced magnitude at the input and its spread occurring due to dispersion, introducing differential signal lines along with designing a delay circuit to match the input signals is proposed. The results of Monte Carlo analysis with 5% variation in process file for both active and passive components of design indicate a negligible impact on the outputs of the proposed circuit. The empirical relation between the channel length and resistance gives rise to a fixed delay of 310 ps, which happens to be independent of the channel length or the scaling of process file.

#### Reference

- [1] B. Bhattacharyya, B. S. Xu and S. Bhattacharyya, "Impact on inter symbol interference (isi) noise due to simulation error," *IEEE 14<sup>th</sup> Topical Meeting on Electrical Performance of Electronics Packaging*, 2005, pp.221-224.

- [2] V. Stojanovic, and M. Horowitz, "Modeling and analysis of high speed link," *Proc. Custom Integrated Circuits Conference*, 2003, pp. 589-594.

- [3] Agilent, "Agilent N5461A Infiniium Serial Data Equalization," 2009.

- [4] J. Rabaey, A. Chandrakasan, and B. Nikolic, "Digital Integrated Circuits: A Design Perspective," *Prentice-Hall*, 2002, 2nd ed.

- [5] A. Nabavi-Lishi, and N.C. Rumin, "Inverter models of CMOS gates for supply current and delay evaluation," IEEE *Trans. Computer-Aided Design*, vol. 13, no. 10, pp. 1271-1279, 1994.

- [6] Y. W Pang, W. Y Sit, C. S Choy, C. F Chan, and W. K Chan, "An asynchronous cell library for self timed system designs," *IEICE Transactions on Information and Systems*, E80-D, no. 3, pp.296-307, 1997.

- [7] M. Bazes, "A novel precision MOS synchronous delay line," *IEEE Journal of Solid State Circuits*, vol. 20, no. 6, pp. 1265-127, 1985.

- [8] J. Zhang, S. R. Cooper, A. R. Lapietra, M. W. Mattern, R. M. Guidash, and E. G. Friedman, "A low power thyristor based CMOS programmable delay element," *Proc. ISCAS*, 2004, vol. 1, pp. 769-772.

- [9] P. Mroszczyk, and P. Dudek, "Tunable CMOS Delay Gate with Reduced Impact of Fabrication Mismatch on Timing Parameters," *IEEE International Conference on New Circuits and Systems*, 2013, pp. 1-4.

- [10] Jung. Lin Yang, C. Wei Chao, Sung Min Lin, "Tunable Delay Element for Low Power VLSI Circuit Design," *IEEE Region 10 Conference*, *TENCON*, 2006, pp. 1-4.

- [11] ASU, "PTM transistor model," 2008, http://ptm.asu.edu/

# Voltage Keeper Based 28.27µW New Frequency Divider Circuit in 90nm Technology for Gigascale SerDes Application

Bipasha Nath<sup>1</sup>, Alak Majumder<sup>1</sup>, Monalisa Das<sup>1</sup>, Abir J Mondal<sup>1</sup>, Pinaki Chakraborty<sup>1</sup>, Bidyut K Bhattacharyya<sup>2</sup>

Abstract- Frequency divider circuit, used in different applications such as RF and microwave, is very much essential when individual components of a system are to be driven at different operating frequencies. Though Current Mode Logic (CML) based frequency divider runs at higher switching frequency, it is still a point of concern due to large power, larger area and low output swing. This paper presents an ultra-low power frequency divider circuit using hybrid logic. It uses a voltage keeper to refresh the dynamic node so as to hold the output logic level undistorted and to obtain a full swing at the output. The simulation is carried out at 6.66 GHz switching frequency with a supply voltage of 1.1 Volt using 90nm Predictive Technology Model (PTM) in LTspice IV. The proposed circuit is also tested on a 4:1 Serializer, an important segment of transmitter module in high speed serial link systems.

#### 1. Introduction

Frequency divider plays a vital role in RF and microwave systems, such as in phase-locked loop frequency synthesizers to generate multiple ranges of frequencies from a reference frequency. Microwave frequency division is a novel approach that employs sub harmonic generation without the use of oscillators. Further, as each successive stage divides the frequency into half, it can be termed as 'mapping of wideband input into narrowband output', which makes them useful in signal processing applications. They are also used at the Defence Research Organizations for ultra-broadband counter measures system, digital signal manipulation and frequency multiplication [1].

Basically, it is classified as analogue and digital dividers. Analogue divider includes the regenerative or Miller frequency divider and the injection-locked frequency divider. Regenerative frequency divider uses a low pass filter followed by an amplifier and the output feedback using a mixer. Thus it removes the higher frequency noise, making it useful as low-phase-noise frequency synthesizers. Injection locked frequency divider [2] uses the concept of forced oscillation in non-linear oscillators having self-oscillation (free-running) frequency and works at high frequency and speed. In contrast to these, digital dividers has simple structures, large bandwidth and good robustness over process variations, but undergoes higher power consumption with frequencies beyond GHz.

It is found that CML based divider is a better choice for very high frequency operation. But due to its reduced output swing, large size and the presence of high static current, the power consumption is large. Thus, for low power applications CML cannot be considered rather it is replaced with static CMOS / hybrid logic. In 2001, Wu et. al. [3] presented a 19 GHz / 0.5mW frequency divider using shunt peaking locking range enhancement technique to increase the frequency range. Another wide band frequency divider was proposed in [4], which uses a LC oscillator for wide band locking range but offers area penalty. Frequency divider circuit implemented for different biomedical applications is presented in [5], which covers a frequency range required for medical implant communication service (MICS) and the industrial, scientific and medical (ISM) frequency bands. Article [6] proposed architecture for Neutrino experiments at 4GHz. Since individual component in a system may have different operating frequency, the generation of different frequencies with lower cost of power is a point of concern. Hence, an attempt has been made in this paper to come up with an ultra-low power frequency divider circuit with lesser number of transistor and higher operating frequency.

The paper is organized as follows: Section 2 presents the proposed architecture and describes its operation in detail. This is followed by the simulation results and different performance analyses in section 3. Section 4 depicts the application of proposed divider in SerDes system. Finally, Section 5 concludes the work.

#### 2. Proposed Frequency Divider

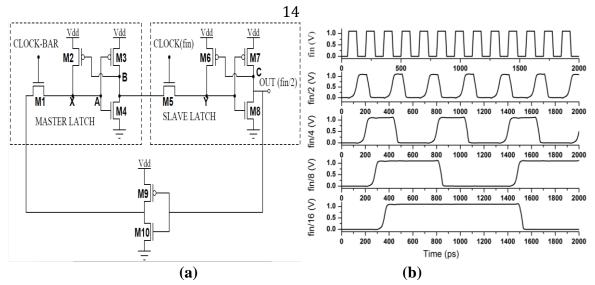

The proposed architecture of frequency divider comprising of 12 transistors, along with its transient response (up to frequency divided by 16) is shown in figure 1.

<sup>&</sup>lt;sup>1</sup>Department of ECE, NIT Arunachal Pradesh, Yupia-791112, India

<sup>&</sup>lt;sup>2</sup>Department of ECE, NIT Agartala, Tripura – 799055, India

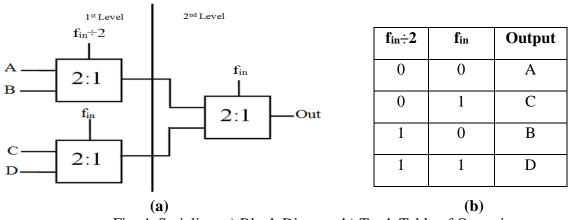

Fig. 1. Proposed Frequency Divider a) Schematic Diagram b) Transient Response

#### A. Working Principle

The gate terminal of NMOS transistor M1 is driven by a complementary clock which regulates the flow of current through the device. Input is fed to M1 and its output is directly connected to the gate terminals of PMOS M3 and NMOS M4, combination of which constitutes a CMOS inverter. Therefore, when the potential at node A (V<sub>A</sub>) is greater than the threshold voltage (V<sub>TH</sub>) of M4, the node capacitance at node B is discharged to ground. However, V<sub>A</sub> being higher than V<sub>TH</sub> of M3, charges up the node capacitance at B to V<sub>DD</sub>. This stable charging to V<sub>DD</sub> and discharging to ground is denoted as logic '1' and logic '0' respectively. So, if VA has logic '0', the potential at node B (V<sub>B</sub>) will be logic '1', which makes the PMOS M2 to be in cut-off, holding back the logic '0' at node A. Similarly, when V<sub>A</sub> is at logic '1', V<sub>B</sub> will have logic '0', letting the PMOS M2 to be ON, which holds back logic '1'. The beauty of this circuit is that, even if the logic level at node A degrades due to M1 (bad conductor of logic '1'), it will get uplifted by the power supply V<sub>DD</sub>. Here, the PMOS M2 acts as a voltage keeper, keeping a strict eye on the logic levels of node A. The architecture consisting of transistors M1, M2, M3 and M4 is working as a latch and may be considered as MASTER latch. A similar architecture is repeated as SLAVE latch comprising of M5, M6, M7 and M8, where the gate terminal of M5 is driven by clock. The complement of output of SLAVE latch (obtained by M9 and M10) is used to drive the M1 of MASTER Latch, which makes it to work as a T Flip-flop or as a frequency divider. The reason of having the two counterparts as MASTER and SLAVE, cascaded with each other, is to make the architecture work at the edge triggering of clock. Cascading of such proposed divider circuit for N times may help to generate multiple frequencies up to  $f_{in}/2^N$  (i.e.,  $f_{in}/2$ ,  $f_{in}/4$ ,  $f_{in}/8$  and so on).

#### B. Significance of Voltage Keeper circuits

The concept of voltage keeper came to rise, when there was a requirement of refreshing technique needed for every dynamic node within the integrated circuits. The job is to continuously hold the logic voltage level at a particular node with the help of power supply  $V_{DD}$ . However, if the transistor, acting as keeper, is left ON all the time, it will leak current from  $V_{DD}$  leading to huge power dissipation. Therefore, a control is must to make the keeper circuit ON, only when it is needed. On the other hand, ON resistance of the keeper transistor should be at an optimal value, so that the current flow through it is quick. Otherwise, there is a scope that the dynamic node may get contaminated with cross–talk during the refreshing of logic level.

In our proposed architecture, the voltage keepers M2 and M6 are appointed to tighten the logic voltage level at node X and Y and are controlled by the voltage at node B and C respectively.

#### 3. Results and Discussions

This proposed frequency divider circuit is designed and simulated using 90nm PTM technology [7] at 1.1 Volt supply voltage. The clock frequency used is 6.66 GHz with a rise time and fall time of 10ps each. The performance parameters of  $\div 2$  circuit is measured and shown in table I.

Table I: Performance Parameters of the proposed divider circuit

| Parameters                                   | Proposed Circuit |

|----------------------------------------------|------------------|

| Technology (nm)                              | 90               |

| Transistor Count                             | 12               |

| Supply Voltage (Volt)                        | 1.1              |

| Operating Frequency (GHz)                    | 6.6              |

| Delay (ps)                                   | 46.76            |

| Average Power (µW)                           | 28.27            |

| Static Power (µW)                            | 1.69             |

| Dynamic power (μW)                           | 3.95             |

| Output Noise Voltage (nV/Hz <sup>1/2</sup> ) | 4.899            |

To check the reliability and robustness of the proposed circuit, we have simulated it in 1000 runs of Monte-Carlo at three different process corners (Fast–Fast, Typical–Typical and Slow–Slow). The results are shown in table II. It is seen that even with the 5% process skew the circuit produces almost similar value of parameters just like when it was run under no skew. It clearly states that our proposed frequency divider is functioning correctly to process variation with less deviation in average power and a nominal for delay. This means that the circuit is a better choice at different temperatures and works better even if some skews are present in intermediate nodes of it.

Table II: Process Variation of Performance Parameters through Monte-Carlo

|           | No Skew   |        |       | 5% Process Skew   |           |           |           |          |           |

|-----------|-----------|--------|-------|-------------------|-----------|-----------|-----------|----------|-----------|

| Process   |           |        |       |                   |           |           |           |          |           |

| Corners   | Avg.      | Delay  | PDP   | P Avg. Power (μW) |           | D         | elay (ps) | PDP (fJ) |           |

|           | Power     | (ps)   | (fJ)  | Mean              | Mean Std. |           | Mean Std. |          | Std.      |

|           | $(\mu W)$ |        |       | Deviation         |           | Deviation |           |          | Deviation |

| FF (0°C)  | 23.826    | 22.462 | 0.535 | 29.43             | 0.498     | 21.64     | 0.637     | 0.636    | 0.0201    |

| TT (27°C) | 29.524    | 23.714 | 0.700 | 28.57             | 0.369     | 23.30     | 0.727     | 0.666    | 0.0200    |

| SS (90°C) | 29.040    | 29.350 | 0.852 | 29.91 0.119       |           | 28.77     | 0.514     | 0.860    | 0.0189    |

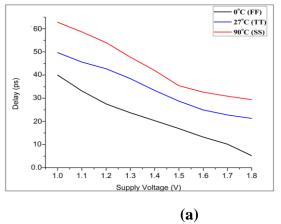

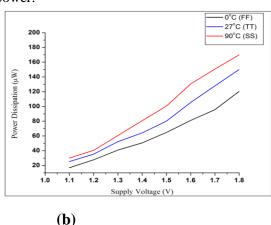

We have analyzed the delay and Average Power of the proposed circuit with a variation in  $V_{DD}$  at different process corners as shown in figure 2a and 2b. It is seen that the delay increases with the reduction of supply voltage and increment in temperature. However, we have observed the power reduction with scaling down of  $V_{DD}$  and temperature. So, at 0°C, the circuit is much reliable in terms of both power and delay. As the temperature increases from 27 °C to 90 °C, the performance of the circuit degrades, but with a very tiny margin. The power dissipation of the proposed circuit is compared with existing frequency divider architectures available in literature and is shown in figure 3. The Bar chart reveals that voltage keeper based proposed circuit consumes least power.

Fig. 2. Parametric Analysis at different temperatures a) Delay Vs Supply Voltage b) Avg. Power vs Supply Voltage

Fig. 3. Power Dissipation Comparison

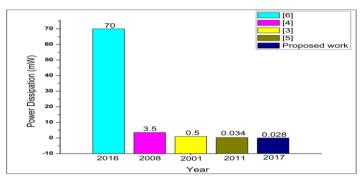

## 4. Application of Proposed Divider in Serializer

Though parallel communications are intrinsically faster than serial communications, serial data transfer is preferred in high speed data links such as chip-to-chip communications in backplane, computer networks and computer peripheral buses etc. SerDes (Serializer - Deserializer) is considered to be the heart of communication in high speed links. Such device is capable of converting data from parallel to serial and vice versa. Serializer is a circuit made of high speed 2:1 multiplexer, which serves parallel to serial data conversion. Each level of serializer works at a frequency which is double than the operating frequency at previous level. So, there lies the importance of frequency divider. The basic block diagram of a 4:1 serializer circuit and truth table of operation is given in figure 4.

Fig. 4. Serializer a) Block Diagram b) Truth Table of Operation

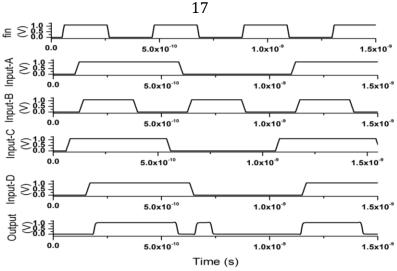

Figure 4a contains three 2:1 MUX at two levels, where if the second level works at a frequency of fin, the previous level will work at half the frequency of fin. The input to the select line of the second level of the serializer is driven from the output of the frequency divider. The multiplexer blocks of first level in figure 4a are given pulse inputs A, B, C and D. These inputs are serialized at the output of  $2^{nd}$  level following figure 4b as per the logic level of select lines available in both multiplexer levels.

Fig. 5. Transient Analysis of Serializer incorporating Proposed Frequency Divider

The 4:1 serializer based on proposed frequency divider is simulated using 90nm PTM. The divider circuit, driven by 6.66 GHz clock frequency (fin), outputs a frequency of 3.33 GHz to be used as fin/2. The transient of the serializer is plotted in figure 5. It is observed that the output follows the truth table given in figure 4b, depending on the logic at select lines. For the logic level 00 at  $f_{in}/2$  and  $f_{in}$  respectively, A is passed at the output. Similarly for 01, 10 and 11 logics C, B and D are passed respectively.

#### 5. Conclusion

In this paper, a novel frequency divider circuit is proposed in hybrid CMOS logic incorporating the voltage keeper principle, which holds the output logic level so as to obtain full swing at the output. The power dissipation reads  $28.27 \, \mu W$ , which is much lesser than the existing designs available in literature. The circuit is proved to be a resilient one as it offers definitive output in three different process corners simulated through monte-carlo. As the circuit runs at higher switching frequency, it is tested in a 4:1 serializer architecture to make it a better choice for high speed data link applications. The circuit may also be used in designing the programmable frequency divider of RF synthesizer circuit for wireless access.

#### References

- [1] W.D. Cornish, "Microwave frequency dividers: devices and applications", IEE Proceedings F Communications, Radar and Signal processing, Vol 129, Issue -3, pp: 208 212, June 1982.

- [2] A. Buonomo, A.L. Schiavo, "A Study of Injection Locking in Dual-Band CMOS Frequency Dividers" IEEE Transactions on Circuits and systems I: Regular Papers, Vol. PP, Issue: 99, 2017.

- [3] H. Wu, A. Hajimiri, "A 19GHz 0.5mW 0.35μm CMOS Frequency Divider with Shunt Peaking Locking Range Enhancement", IEEE International Solid State Circuit Conference 2001.

- [4] K.H. Tsai, L.C. Cho, J.H. Wu, S.I. Liu, "3.5mW W-band Frequency Divider with wide Locking range in 90nm CMOS Technology," IEEE International Solid State Circuit Conference 2008.

- [5] K. Zhu, S.K. Islam, J. Holleman, S. Yuan, "A Low-Power Dual-Modulus Injection-Locked Frequency Divider for Medical Implants," Radio and Wireless Symposium (RWS), 2011 IEEE.

- [6] N. Parkalian, M. Robens, C. Grewing, S.V. Waasen, "A 4GHz LC-Based Voltage Controlled Oscillator & Frequency Divider for use in Neutrino Experiments", ANALOG 2016; ITG/GMM-Symposium; Proceedings of.

- [7] http://ptm.asu.edu

# Power Efficient Test Pattern Generator Using Bit-Swapping LFSR Technique

Sandeep Kakde<sup>1</sup>, Yashika Gaidhani<sup>2</sup>, Tejas Thubrikar<sup>3</sup>, Shailesh Kamble<sup>4</sup>, Nikit Shah<sup>5</sup>

<sup>1,2,3</sup>Department of Electronics Engineering, Yeshwantrao Chavan College of Engineering, Nagpur, India.

**Abstract** – The testing of VLSI circuits enables many challenges in term of area, power, and latency. The Bit-swapping test pattern generation is a key technique for testing of a complex architecture of VLSI design. In this paper, 32-bit Bit-swapping test pattern generator has been proposed for testing the VLSI design. This 32-bit test pattern generator is implemented with efficient LFSR and with Multiplexer for swapping bit which achieved Low power consumption. The switching activities between the two consecutive tests vectors are reduced which results in low power consumption. The design of test pattern generation which yield a power of 32 mw with a latency of 4.713ns. The switching activity required for 32-bit test pattern generation has been improved and presented in this paper. It is observed that total power consumed in Bit-Swapping linear feedback shift register is 34.69% less than the conventional LFSR. The design is implemented using Xilinx 13.1 ISE design suite in Verilog HDL present in this paper.

#### Introduction

Testing of the digital circuit is a major challenge today with low power consumption. The development of microelectronics industry allows us to design a complex digital system on a single chip. To test such a complex VLSI design, Built-in-self-test (BIST) technique has been extensively studied and widely used nowadays. In BIST, the pattern is generated and applied to circuit-under test (CUT) by On-chip system, minimizing hardware overhead which is a major concern of BIST implementation. BIST technique is used with the LFSR to generate the test pattern which results in high power consumption. The switching activity between two consecutive patterns in BIST technique is on a higher side. As Power dissipation is a major problem in system-on-chip (SOCs) that contains a very large number of a transistor. In CMOS technology, there are three types of power dissipation occurs are as follows;

• Static Power Dissipation: - It occurs when the system is in steady state.

$$P_{static} = V_{DD} \bullet I_{leakage}$$

• Short Circuit Power Dissipation: - It occurs when the current flowing from power supply to ground. Also called short circuit path flowing from power supply to ground.

$$P_{short} = V_{DD} \bullet I_{short}$$

• Dynamic Power Dissipation: - It is superior Power dissipation in CMOS Devices. the 90% of Dynamic power dissipation occurs in overall power consumption in CMOS Devices. it occurs due to different input combination applied to the device for testing.

$$P_{dynamic} = \beta C V_{DD}^2 f$$

Where  $\beta$  is a Switching Activity, C is a Load Capacitance, f is a Switching frequency and VDD is a Supply voltage.

In terms of power consumption, the Short circuit and static power dissipation are less than the dynamic power dissipation. Therefore, dynamic power dissipation is a crucial source of power dissipation in CMOS. In test mode, power dissipation is more than the normal mode. In general, the power consumption of a system in testing mode is more than in normal modes. The four reasons for the increase of power dissipation during testing mode are: high switching activity caused by nature of test patterns, parallel activation of internal cores during testing, power consumed by extra design-fortest circuitry and low correlation among test vectors.

Some of the previous approaches have been discussed in this section which is used to reduced power consumption during testing of VLSI circuit. In [1], they introduced the test pattern generator model using Linear Feedback Shift Register which efficiently used for wireless communication application and also with this method of TPG can be used efficiently in secure transmission of codes and with low power consumption and also can be used for applications like

<sup>&</sup>lt;sup>4</sup>Department of Computer Technology, Yeshwantrao Chavan College of Engineering, Nagpur, India.

<sup>&</sup>lt;sup>5</sup>Department of Electrical Engineering, San Jose State University, California-95192.

Data compression, PN sequence generation. Another technique that reduces the power consumption during testing is low transition linear feedback shift register which gives the maximum correlation between the two test pattern as compared to that of linear feedback shift register which in turn reduces the switching activities i.e. number of transition in between the two test vectors as a result of this reduction, the power consumption is reduced during testing [2]. In [3-4], generation of the test pattern with high fault coverage Built-In-Self-test applications reduces the number of transitions that occurs at scan inputs during scan shift operations and therefore reduces switching activity in the circuit under test (CUT) which ultimately reduces test power with high target fault coverage without increasing test length sequences. In [5], the reduction in static power has been achieved using Dual threshold Bit-swapping LFSR and automatic test pattern generator is implemented with less cost. Two strategies are used LOC (Launch of Capture) and Bit-swapping with this testing of ISCAS' 89-S27 benchmark circuit is done with efficient area overhead and less power consumption [6]. In [7], a design of low power test pattern generator using low power linear feedback shift register presents a low power test pattern generator has been proposed which reduces the power consumption during testing mode with a minimum number if switching activities using LP-LFSR in place of conventional LFSR in the circuit used for test pattern generator. In [7] [6], they award the low correlation between the test vector. In [9], they proposed low Power LFSR architecture with high fault coverage design for BIST architecture which uses for security application

# **Design Approach**

This paper presents a test pattern generator using 32-bit linear feedback shift register and with 32-bit Bit-swapping linear feedback shift register. The ideology of this paper is to increase the correlation between the two test vectors and reduce the number of transition i.e., switching activities. The conventional linear feedback shift register (LFSR) and Bit-Swapping LFSR are discussed in 1 and 2 respectively.

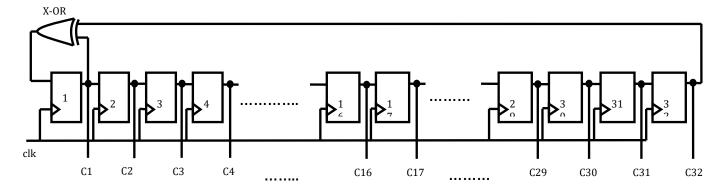

#### A. LINEAR FEEDBACK SHIFT REGISTER

The LFSR is a Linear Feedback Shift Register which generates the test pattern which is known as a pseudo random pattern. LFSR consist of a number of flip-flops connected in series with each other and exclusive-OR gate is used as a feedback. The 32-LFSR Structure as shown in fig.1 which generate the random test pattern. The fig.1 consists of an exclusive-OR gate as a feedback which having two input from last and first flip-flop output and output of exclusive-OR gate is provided to an input of the first flip-flop. The shift register is made from number of D-flip-flop arranged in series connection which provided with the same clock.

Fig. 1: 32-bit LFSR Structure

#### Limitation of LFSR:

Linear Feedback Shift Register is used to generate Pseudo Random Test Pattern. This Random pattern results in high switching activities i.e., the number of transition between two consecutive test pattern which in turn increases the power consumption during testing of any digital circuit. To reduce this limitation we introduced the technique name as Bitswapping Linear Feedback Shift Register discussed in section B.

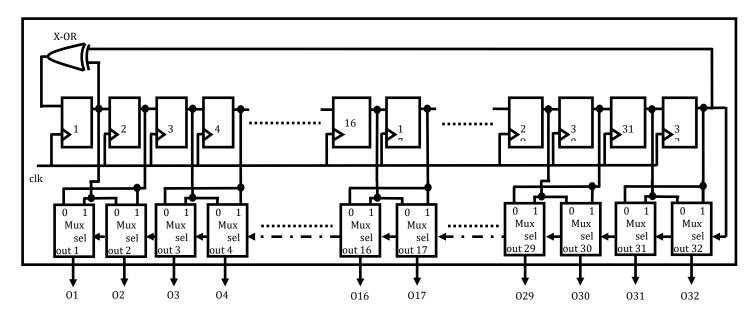

### B. BIT-SWAPPING LINEAR FEEDBACK SHIFT REGISTER

By adding some extra circuitry to Linear Feedback Shift Register we can create Bit-Swapping LFSR. Bit-swapping LFSR consists of LFSR and a 2x1 multiplexer. The Bit-swapping LFSR is a modified version of convection LFSR which

generates a pseudo random pattern. In BS-LFSR, the function of 2x1 Mux is to swap the bit of LFSR. With this swapping we can reduce the number of transition i.e., switching activity between consecutive test pattern. This reduction of transition or switching activity reduces the average power consumption. Fig.2 shows the 32-bit Bit-swapping LFSR structure.

Fig. 2: 32-bit Bit-swapping LFSR Structure

#### Design Steps:

- 1. Bit-swapping LFSR will generate the same number of bit pattern as conventional LFSR but the test pattern will be in a different manner.

- 2. Bit-swapping LFSR will create the same number of 0s and 1s through 2x1 multiplexer used to swap the bit of consecutive flip-flop.

- 3. The above fig. 2 is to generate 32-bit test pattern with the used of conventional LFSR and 2x1 Mux (32 numbers).

- 4. The function of Mux is to swap the output bit of flip-flop 1 with 2, 3 with 4 and so on till 31 with 32.

- 5. With this swapping, we reduce the transition between consecutive patterns.

- 6. For 32-bit LFSR which begin with initial seed and runs to generate test patterns for 2x32 clock cycles until it comes back to its initial seed.

In above table without applying bit swapping the number of transitions in C1 and C2 are 8 and 8.But after applying bit swapping technique the number of transitions in the same C1 and C2 are 8 and 4 respectively. So the total number of transitions is 16, without applying bit swapping and 12, after applying bit swapping technique. Hence the number of transitions is decreased results in the reduction of power consumption. Finally, the peak power is reduced by using this bit swapping technique. It is important to note that the overall savings of the number of transition is 25% between the outputs of the multiplexers. This is because the value of C1 in the present state will affect the value of C2 and its own value in the next state (C2 (Next) = C1 and C1 (Next) = "C1 Xor C32"). To see the effect of each register in transition savings.

Table 1 tells that O1 will save one transition when moving from state [0,0,1] to next state [1,0,0], from [0,1,1] to [1,0,0], from [1,0,1] to [0,1,0], or from [1,1,1] to [0,1,0] whereas at the same time, O1 will add one transition when moving from state [0,1,0] to next state [0,0,0], from [0,1,0] to [0,0,1], from [1,0,0] to [1,1,0], or from [1,0,0] to [1,1,1]. Therefore, O1 increases the four transitions and at the same time, o1 will save four transitions in other scene. Hence, within this sense the overall transition occurs in O1 will be neutral.. On the other hand, O2 will save one transition while moving from state [0,1,0] to next state [0,0,0], from [0,1,0] to [0,0,1], from [0,1,1] to [1,0,0], from [1,0,0] to [1,1,1], and from [1,0,1] to [0,1,0] whereas, in O2 two additional transition is experienced when moving from state [0,0,1] to [1,0,0] and from [1,1,1] to [0,1,0]. This result that O2 will save overall four possible transitions where the initial state has a probability of 1/8 and the final states of probability 1/2.

# NUMBER OF TRANSITION IN EACH REGISTER IN LFSR WITHOUT APPLYING BIT SWAPPING LFSR TECHNIQUE AND WITH BIT SWAPPING

| LFSR Output                   |        |     |    |         |     | Bit-Swapping LFSR output |         |                 |    |                   |    |    |            |    |   |

|-------------------------------|--------|-----|----|---------|-----|--------------------------|---------|-----------------|----|-------------------|----|----|------------|----|---|

|                               | States | 6   | N  | ext sta | te  | T                        | ransiti | ansition States |    | States Next state |    |    | Transition |    |   |

| C1                            | C2     | C32 | C1 | C2      | C32 | C1                       | C2      | $\sum$          | 01 | 02                | 01 | 02 | 01         | 02 | Σ |

|                               |        |     | 0  | 0       | 0   | 0                        | 0       | 0               |    |                   | 0  | 0  | 0          | 0  | 0 |

| 0                             | 0      | 0   | 0  | 0       | 1   | 0                        | 0       | 0               | 0  | 0                 | 0  | 0  | 0          | 0  | 0 |

|                               |        |     | 1  | 0       | 0   | 1                        | 0       | 1               |    |                   | 0  | 1  | 0          | 1  | 1 |

| 0                             | 0      | 1   | 1  | 0       | 1   | 1                        | 0       | 1               | 0  | 0                 | 1  | 0  | 1          | 0  | 1 |

|                               |        |     | 0  | 0       | 0   | 0                        | 1       | 1               |    |                   | 0  | 0  | 1          | 0  | 1 |

| 0                             | 1      | 0   | 0  | 0       | 1   | 0                        | 1       | 1               | 1  | 0                 | 0  | 0  | 1          | 0  | 1 |

|                               |        |     | 1  | 0       | 0   | 1                        | 1       | 2               |    |                   | 0  | 1  | 0          | 0  | 0 |

| 0                             | 1      | 1   | 1  | 0       | 1   | 1                        | 1       | 2               | 0  | 1                 | 1  | 0  | 1          | 1  | 2 |

|                               |        |     | 1  | 1       | 0   | 0                        | 1       | 1               |    |                   | 1  | 1  | 1          | 0  | 1 |

| 1                             | 0      | 0   | 1  | 1       | 1   | 0                        | 1       | 1               | 0  | 1                 | 1  | 1  | 1          | 0  | 1 |

|                               |        |     | 0  | 1       | 0   | 1                        | 1       | 2               |    |                   | 1  | 0  | 0          | 0  | 0 |

| 1                             | 0      | 1   | 0  | 1       | 1   | 1                        | 1       | 2               | 1  | 0                 | 0  | 1  | 1          | 1  | 2 |

|                               |        |     | 1  | 1       | 0   | 0                        | 0       | 0               | ,  |                   | 1  | 1  | 0          | 0  | 0 |

| 1                             | 1      | 0   | 1  | 1       | 1   | 0                        | 0       | 0               | 1  | 1                 | 1  | 1  | 0          | 0  | 0 |

|                               |        |     | 0  | 1       | 0   | 1                        | 0       | 1               |    |                   | 1  | 0  | 0          | 1  | 1 |

| 1                             | 1      | 1   | 0  | 1       | 1   | 1                        | 0       | 1               | 1  | 1                 | 0  | 1  | 1          | 0  | 1 |

| \( \sum_{\text{ransition}} \) |        | 1   | 1  | 8       | 8   | 16                       |         | 1               | 1  |                   | 8  | 4  | 12         |    |   |

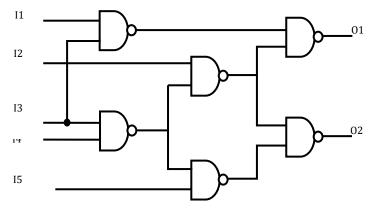

Fig. 3: C17 Benchmark circuit

# **Implementation Model**

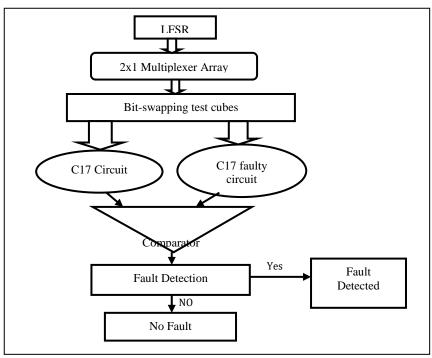

The implementation model is developed on Xilinx 13.1 ISE design suite with Verilog coding. The fig. 3 shows the one of the ISCAS'85 benchmark circuit named as C17. This circuit is designed with good and bad signature and test with both LFSR and Bit-swapping LFSR.

The testing of above circuit with LFSR and Bit-swapping is as shown in fig. 4. The test pattern for testing is generated through LFSR and Bit-swapping respectively. The generated test pattern is applied to the good circuit and bad circuit for fault detection. The comparator is used to compare the signature of the good and bad circuit and tells us for which test pattern the circuit will faulty.

Fig. 4: Flow Chart for Testing

## **Simulation Result:**

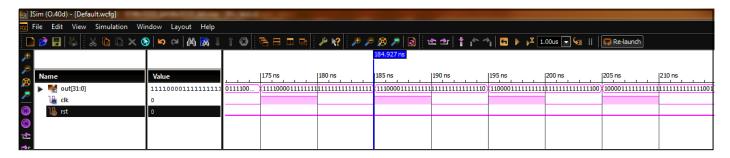

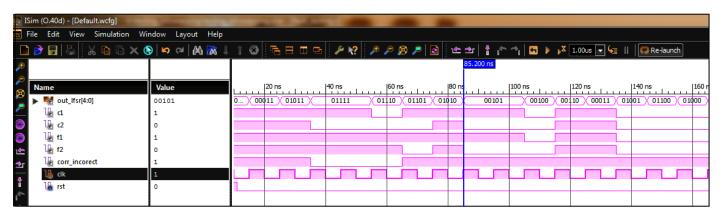

Fig.5: 32-bit Pattern generation using LFSR

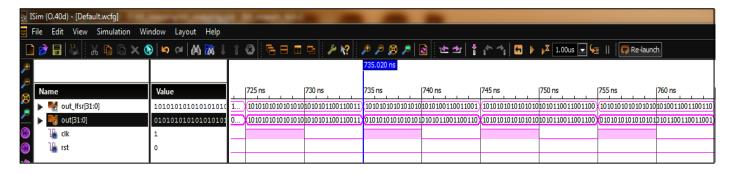

Fig. 6: 32-bit Pattern generation using Bit-swapping LFSR

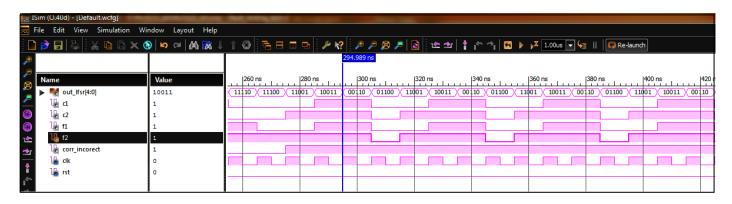

Fig. 7: Fault testing for C17 using LFSR

Fig.8: Fault testing forC17 using Bit-swapping LFSR

The simulation result obtained from the Xilinx 13.1 ISE design suite with the target device xc6slxl6-3csg324 in which, we have generated VCD file after the post-simulation. Xpower analyzer is used to determine dynamic as well as quiescent power. The result is obtained for each case and comparison is done on the basis of power, latency, and area overhead as shown in the following table.

$TABLE\ 2$  Comparison of Power Dissipation, Latency, No. of LUT's for Convectional LFSR and Bit-Swapping LFSR

| EDA Tool: Xilinx Product Version: ISE 13.1 Target Device: xc6slx16-3csg324 Type of Random Sequence generator |                   |              |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|-------------------|--------------|--|--|--|--|--|

| Parameter                                                                                                    | Conventional LFSR | Bit-Swapping |  |  |  |  |  |

| No. of Bits                                                                                                  | 32-bit            | 32-bit       |  |  |  |  |  |

| No. of Slices Register                                                                                       | 32                | 33           |  |  |  |  |  |

| No. of bounded IOBs                                                                                          | 34                | 66           |  |  |  |  |  |

| Total Power (mW)                                                                                             | 49.00             | 32.00        |  |  |  |  |  |

| Latency (ns)                                                                                                 | 3.668             | 4.713        |  |  |  |  |  |

| No. of LUT's 12 33                                                                                           |                   |              |  |  |  |  |  |

#### Conclusion

This paper shows an effective HDL Verilog implementation of Low Power Test Pattern Generator using Bit-Swapping LFSR technique. It also addresses a theory to express a test pattern generation greatly reduced as compared to the conventional LFSR technique. It shows that the total power consumed in low transition linear feedback shift register is 34.69% less than the conventional LFSR. It is concluded that low power Bit-Swapping LFSR is very much useful for power optimization techniques during testing mode.

#### Reference

- [1] Mohammad Feroz Khan, Devunoori Sandeep, Mohd Khaja Yakoob Hussaini, Vaddepally Ashok, and Lisbeth Priyadharshini, "TPG Applications using LFSR", Kakatiyaa Institute of Technology and Science, ELSEVIER 2013.

- [2] Moorthy, P., and S. Saranya Bharathy. "An efficient test pattern generator for high fault coverage in built-in-self-test applications." *In Computing, Communications and Networking Technologies* (ICCCNT), 2013 Fourth International Conference on, pp. 1-4. IEEE, 2013

- [3] Mehrdad Nourani, Mohammad Tehranipoor and Nisar Ahmed. "Low transition LFSR for BIST-based applications", *IEEE TRANSACTIONS ON COMPUTERS*, Vol. 57, NO. 3, MARCH 2008.

- [4] PrasadaRao, R. Vara, N. Anjaneya Varaprasad, G. Sudhakar Babu, and C. Murali Mohan. "Power optimization of Linear Feedback Shift Register (LFSR) for Low Power BIST implemented in HDL." *International Journal of Modern Engineering Research* (IJMER) Vol 3.

- [5] Dhanesh, P., and A. Jayanth Balaji. "Dual threshold bit-swapping LFSR for power reduction in BIST." *In Advanced Computing and Communication Systems*, 2015 International Conference on, pp. 1-3. IEEE, 2015.

- [6] Vignesh, M., and J. Jayaseelan. "Transition faults test pattern generation for minimizing power using BS-LFSR and LOC." *In Circuit, Power and Computing Technologies (ICCPCT), 2015 International Conference on*, pp. 1-6. IEEE, 2015.

- [7] Kavitha, A., G. Seetharaman, T. N. Prabakar, and S. Shrinithi. "Design of Low Power TPG Using LP-LFSR." In 2012 Third International Conference on Intelligent Systems Modelling and Simulation, pp. 334-338. IEEE, 2012.

- [8] Jamgade, R., Ambatkar, S., & Kakde, S. (2015, March). Design and implementation of PN sequence generator using Vedic multiplication. *In Computer Engineering and Applications* (ICACEA), 2015 *International Conference on Advances* in (pp. 84-87). IEEE.

- [9] Prathyusha Nayineni and S.K Masthan,"Power Optimization of BIST circuit using low power LFSR", *International Journal of Computer Trends and Technology* Vol 2 Issuse2-2011.

- [10] Y.Zorian, "Distributed BIST control scheme for complex VLSI device," Proc. VLSI test Symp., P.4-9,1993.

- [11] P.Girard,"Survey of low-power testing of VLSI circuits", *IEEE design and test of computers*, Vol. 19, No.3, PP 80-90, May-June 2002.

- [12] Jamgade, R., Ambatkar, S., & Kakde, S. (2015, April). HDL Implementation of PN Sequence Generator Using Vedic Multiplication and Add & Shift Multiplication. *In Communication Systems and Network Technologies* (CSNT), 2015 Fifth International Conference on (pp. 854-858). IEEE.

- [13] Ukey, Shashank, Shubhangi Rathkanthiwar, and Sandeep Kakde. "VLSI implementation of low power scan based testing." *In Communication and Signal Processing* (ICCSP), 2016 *International Conference on*, pp. 0866-0870. IEEE, 2016.

# Estimation of Stability and Performance metric for Inward Access Transistor based 6T SRAM Cell Design using n-type/p-type DMDG-GDOV TFET

Sunil Kumar and Balwinder Raj

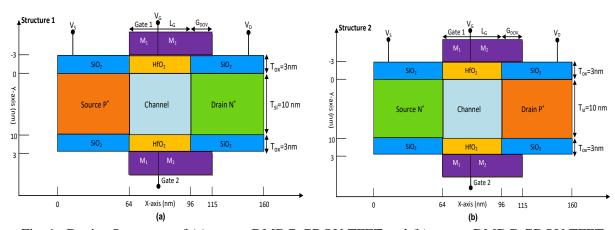

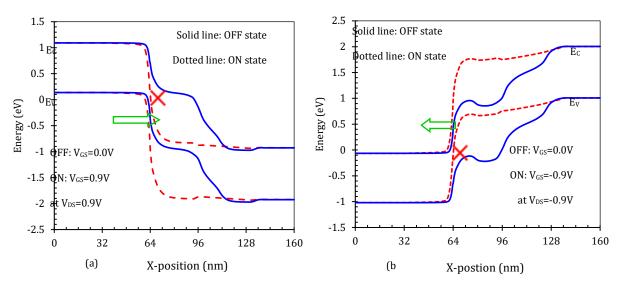

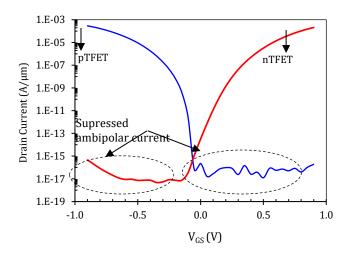

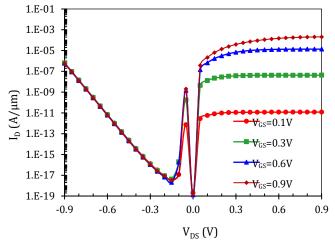

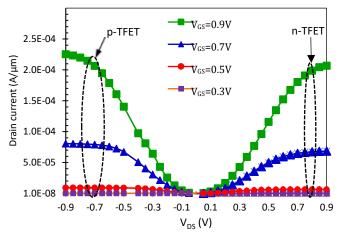

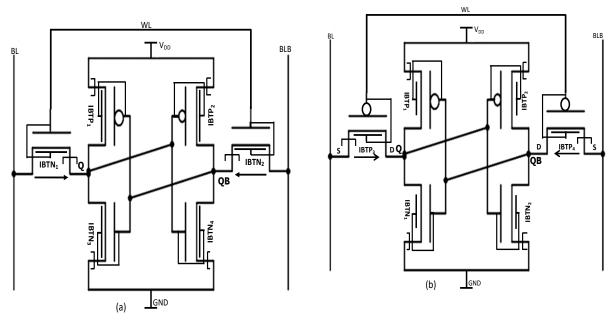

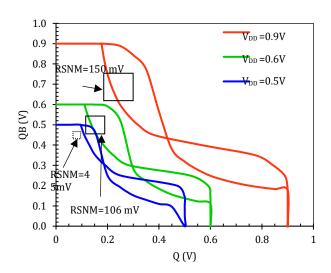

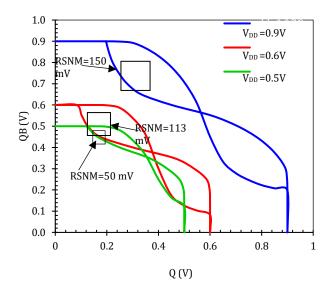

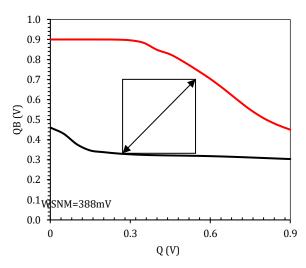

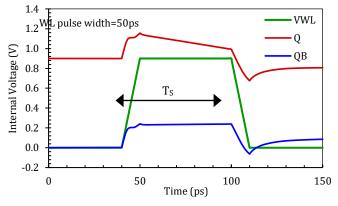

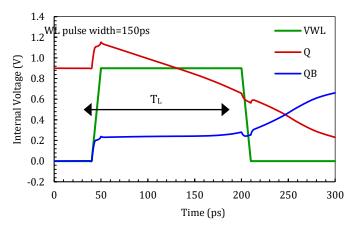

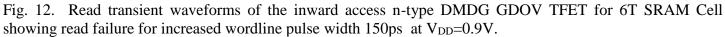

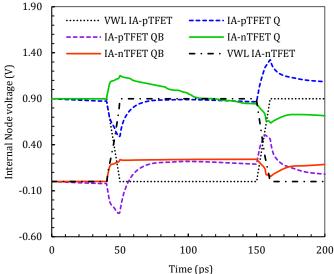

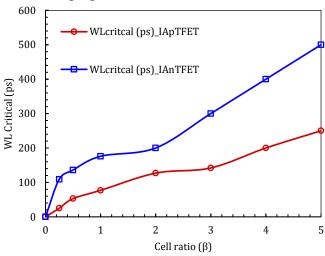

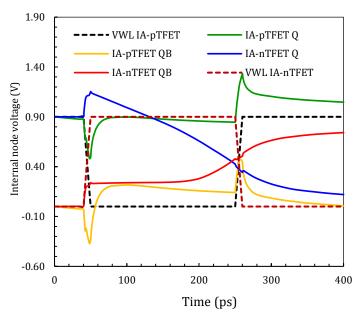

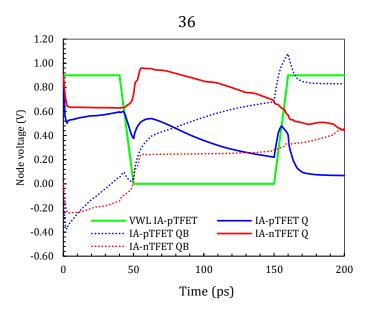

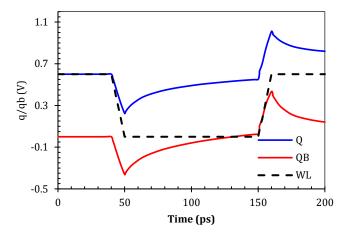

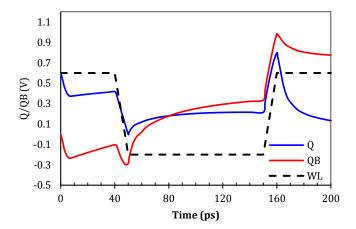

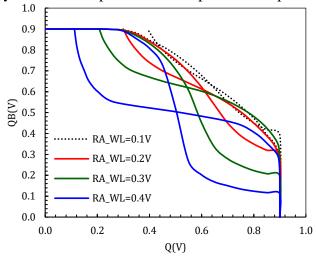

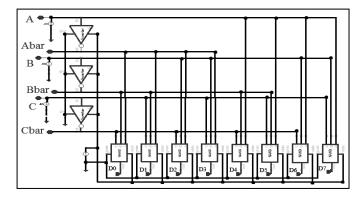

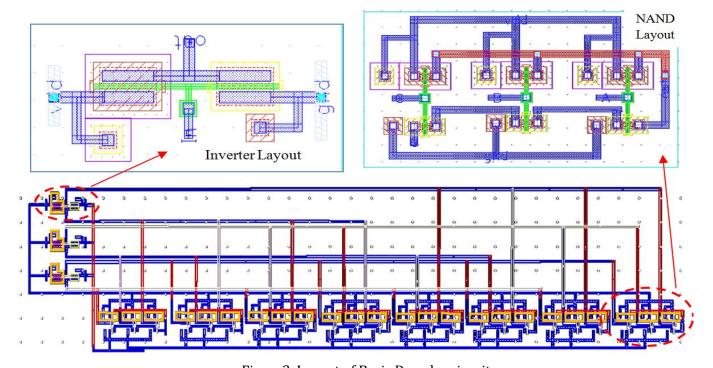

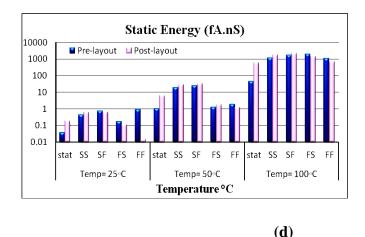

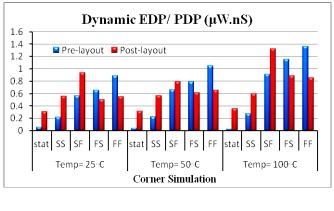

Department of Electronics and Communication Engineering, National Institute of Technology Jalandhar, India.