# VLSI Design Issues

Scaling/Moore's Law has limits due to the physics of material.

- Now L (L=20nm??) affects tx delays (speed), *noise*, heat (power consumption)

- Scaling increases density of txs and requires "more" interconnect (highways & buses)-more delays (lowering speed) and heat.

Possible Solutions:

- New fabrication solutions/material. E.g., Interconnect layers, new material (copper & low k-material)

- Improve physical Designs at the transistor level. Create better cell libraries (min Power, min-delay, max speed)

- Exploit transister analog/physics characteristics

- Invent new transistors

- Invent new architectures

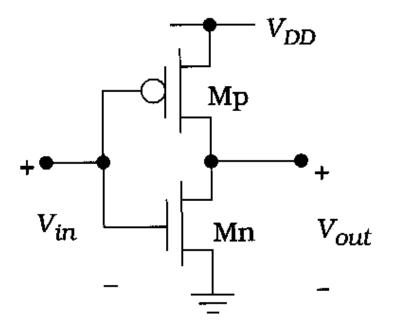

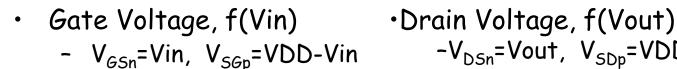

#### CMOS Inverter: DC Analysis

- Analyze DC Characteristics of CMOS Gates by studying an Inverter

- DC Analysis

- DC value of a signal in static conditions

- DC Analysis of CMOS Inverter

- Vin, input voltage

- Vout, output voltage

- single power supply, VDD

- Ground reference

- find Vout = f(Vin)

- Voltage Transfer Characteristic (VTC)

- plot of Vout as a function of Vin

- vary Vin from 0 to VDD (and in reverse!)

- find Vout at each value of Vin

pFET:  $V_{Tp} < 0$  $\beta_p = \kappa'_p \left(\frac{W}{L}\right)_p$

nFET:  $V_{Tn} > 0$  $\beta_n = k'_n \left(\frac{W}{L}\right)_n$

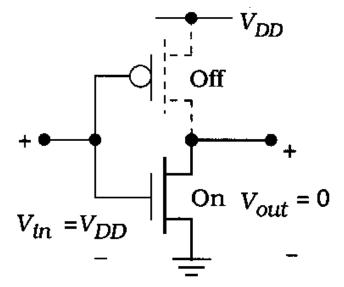

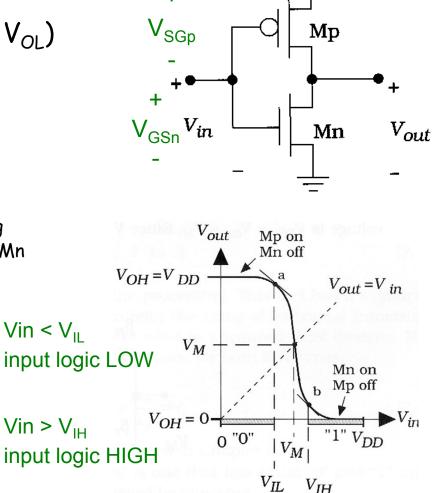

#### **Inverter Voltage Transfer Characteristics**

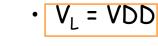

- Output High Voltage, V<sub>OH</sub>

- maximum output voltage

- occurs when input is low (Vin = OV)

- pMOS is ON, nMOS is OFF

- pMOS pulls Vout to VDD

- V<sub>OH</sub> = VDD

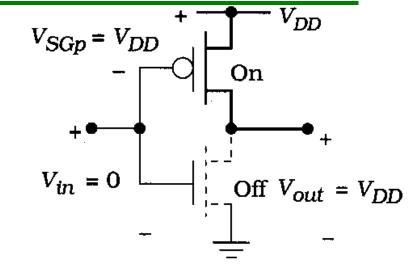

- Output Low Voltage, V<sub>OL</sub>

- minimum output voltage

- occurs when input is high (Vin = VDD)

- pMOS is OFF, nMOS is ON

- nMOS pulls Vout to Ground

- $-V_{OL} = 0V$

- Logic Swing

- Max swing of output signal

•

$$V_L = V_{OH} - V_{OH}$$

Lecture Notes 7.3

#### **Inverter Voltage Transfer Characteristics**

- -V<sub>DSn</sub>=Vout, V<sub>SDp</sub>=VDD-Vout

- Transition Region (between  $V_{OH}$  and  $V_{OL}$ ) •

- Vin low

- Vin < Vtn</li>

- Mn in Cutoff, OFF

- Mp in Triode, Vout pulled to VDD

- Vin > Vtn < ~Vout</li>

- Mn in Saturation, strong current

- Mp in Triode, V<sub>SG</sub> & current reducing

- Vout decreases via current through Mn

- Vin = Vout (mid point)  $\approx \frac{1}{2}$  VDD

- Mn and Mp both in Saturation

- maximum current at Vin = Vout

- Vin high

- Vin > ~Vout, Vin < VDD |Vtp|</li>

- Mn in Triode, Mp in Saturation

- Vin > VDD |Vtp|

- Mn in Triode, Mp in Cutoff

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

$V_{DD}$

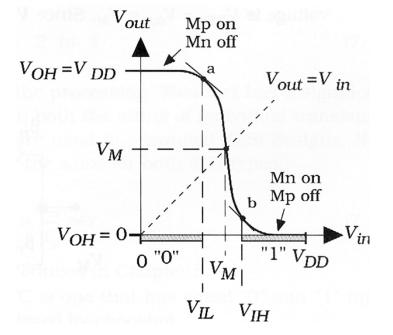

## Noise Margin

- Input Low Voltage, V<sub>TL</sub>

- Vin such that Vin  $\langle V_{IL} = logic 0$

- point 'a' on the plot

- where slope,  $\underline{\partial Vin} = -1$ ∂Vout

- Input High Voltage, V<sub>TH</sub>

- Vin such that Vin >  $V_{IH}$  = logic 1

- point 'b' on the plot

- where slope =-1

- Voltage Noise Margins •

- measure of how stable inputs are with respect to signal interference

-

$$VNM_{H} = V_{OH} - V_{IH}$$

=  $VDD - V_{IH}$

-  $VNM_{L} = V_{IL} - V_{OL}$  =  $V_{IL}$

-

$$VNM_L = V_{IL} - V_{OL}$$

desire large VNM<sub>H</sub> and VNM<sub>1</sub> for best noise immunity

# Switching Threshold

- Switching threshold = point on VTC where Vout = Vin

- also called midpoint voltage,  $V_M$

- here, Vin = Vout =  $V_M$

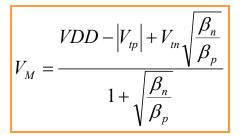

- Calculating  $V_M$

- at  $V_M$ , both nMOS and pMOS in Saturation

- in an inverter,  $I_{Dn} = I_{Dp}$ , always!

- solve equation for  $V_M$

$$I_{Dn} = \frac{\mu_n C_{OX}}{2} \frac{W}{L} (V_{GSn} - V_{tn})^2 = \frac{\beta_n}{2} (V_{GSn} - V_{tn})^2 = \frac{\beta_p}{2} (V_{SGp} - |V_{tp}|)^2 = I_{Dp}$$

- express in terms of  $V_{\rm M}$

$$\frac{\beta_n}{2}(V_M - V_{tn})^2 = \frac{\beta_p}{2}(V_{DD} - V_M - |V_{tp}|)^2 \implies \sqrt{\frac{\beta_n}{\beta_p}}(V_M - V_{tn}) = V_{DD} - V_M - |V_{tp}|$$

$$- \text{ solve for } V_M = \frac{V_{DD} - |V_{tp}| + V_{tn}\sqrt{\frac{\beta_n}{\beta_p}}}{1 + \sqrt{\frac{\beta_n}{\beta_p}}}$$

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

Vout

$V_M$

0 "0"

$V_{OH} = 0$

$V_{OH} = V_{DD}$

Mp on Mn off

$|V_M|$

VIH

$V_{IL}$

$V_{out} = V_{in}$

Mn on

Mp off

"1" V<sub>חת</sub>

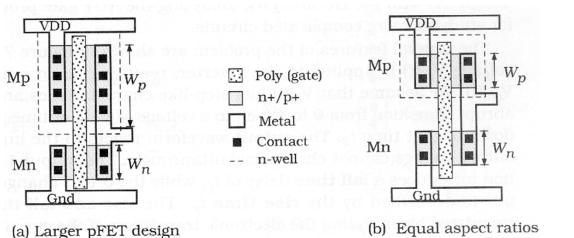

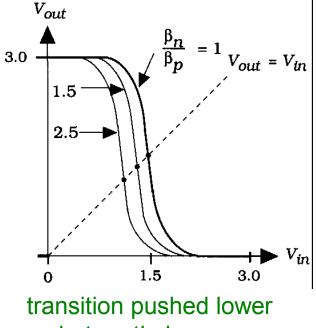

# Effect of Transistor Size on VTC

• **Recall**

$$\beta_n = k'_n \frac{W}{L}$$

$\frac{\beta_n}{\beta_p} = \frac{k'_n \left(\frac{W}{L}\right)_n}{k'_p \left(\frac{W}{L}\right)_p}$

- If nMOS and pMOS are same size

- (W/L)n = (W/L)p

- Coxn = Coxp (always)

$$\frac{\beta_n}{\beta_p} = \frac{\mu_n C_{oxn} \left(\frac{W}{L}\right)_n}{\mu_p C_{oxp} \left(\frac{W}{L}\right)_p} = \frac{\mu_n}{\mu_p} \cong 2or3$$

• If  $\frac{\left(\frac{W}{L}\right)_p}{\left(\frac{W}{L}\right)} = \frac{\mu_n}{\mu_p}$ , then  $\frac{\beta_n}{\beta_p} = 1$  since L normally min. size for all tx, can get betas equal by making Wp larger than Wn

- Effect on switching threshold

- if  $\beta_n \approx \beta_p$  and Vtn = |Vtp|,  $V_M$  = VDD/2, exactly in the middle

- Effect on noise margin

- if  $\beta_n \approx \beta_p$ ,  $V_{IH}$  and  $V_{IL}$  both close to  $V_M$  and <u>noise margin is good</u>

## Example

- Given

- $k'n = 140uA/V^2$ , Vtn = 0.7V, VDD = 3V

- $k'p = 60uA/V^2$ , Vtp = -0.7V

- Find

- a) tx size ratio so that  $V_{M}$  = 1.5V

- b)  $V_{M}$  if tx are same size

as beta ratio increases

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

Lecture Notes 7.8

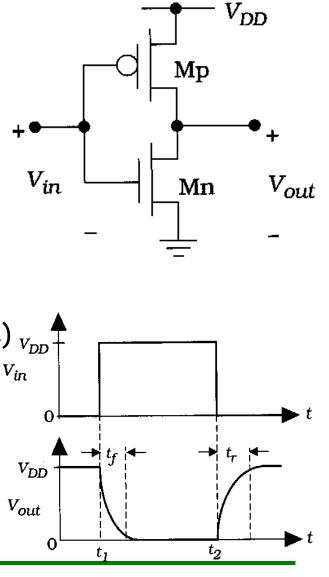

#### **CMOS Inverter:** Transient Analysis

- Analyze Transient Characteristics of CMOS Gates by studying an Inverter

- Transient Analysis

- signal value as a function of time

- Transient Analysis of CMOS Inverter

- Vin(t), input voltage, function of time

- Vout(t), output voltage, function of time

- VDD and Ground, DC (not function of time)  $_{V_{DD}}$

- find Vout(t) = f(Vin(t))

- Transient Parameters

- output signal rise and fall time

- propagation delay

Lecture Notes 7.9

#### **Transient Response**

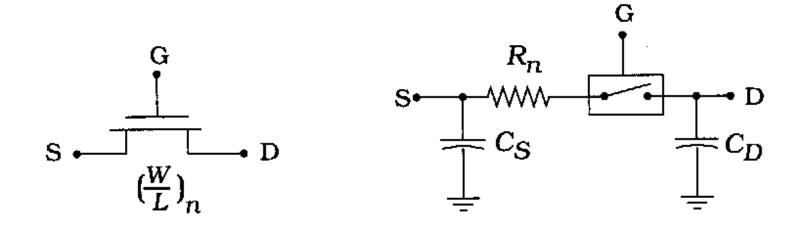

• Recall: the RC nMOS Transistor Model

Lecture Notes 7.10

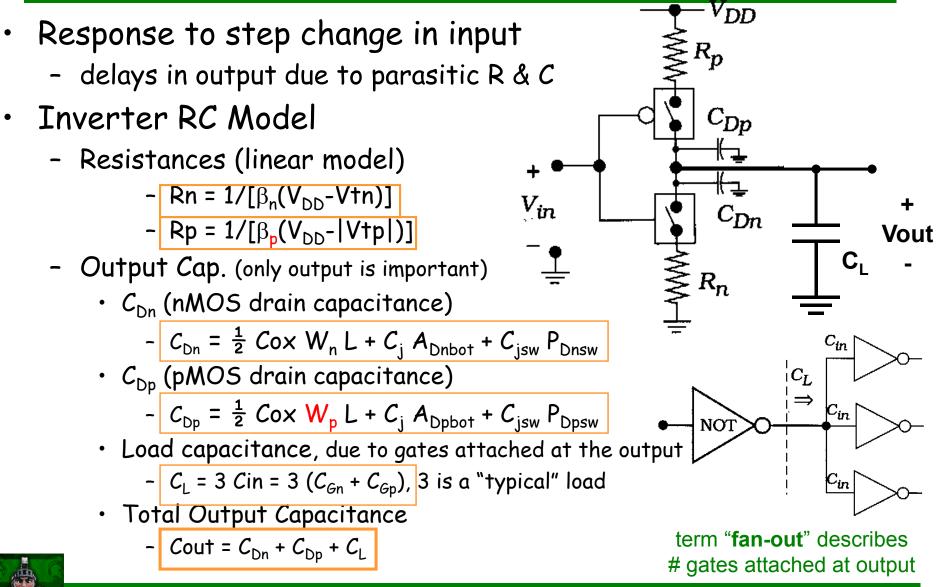

## **Transient Response**

STATE

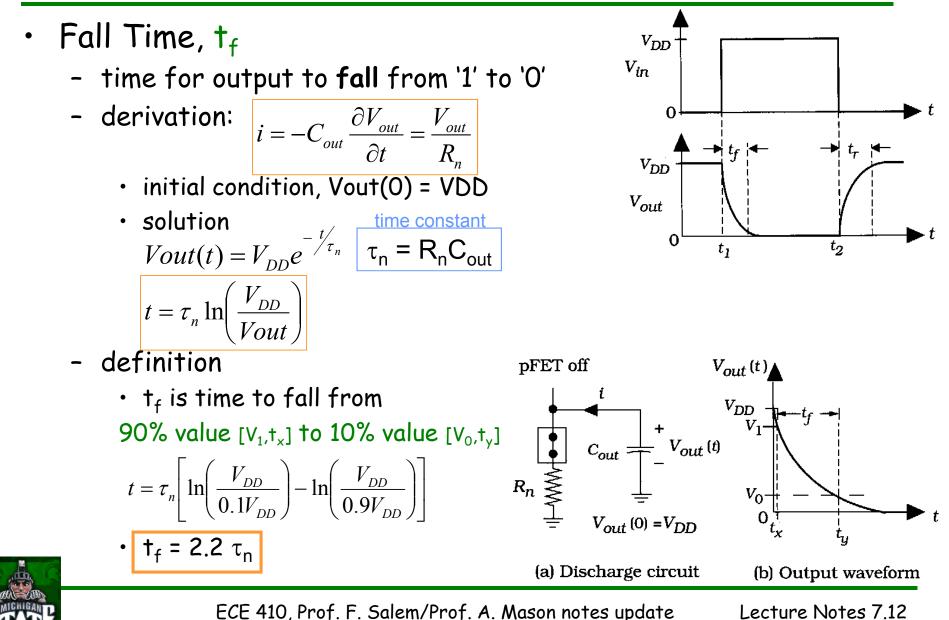

## Fall Time

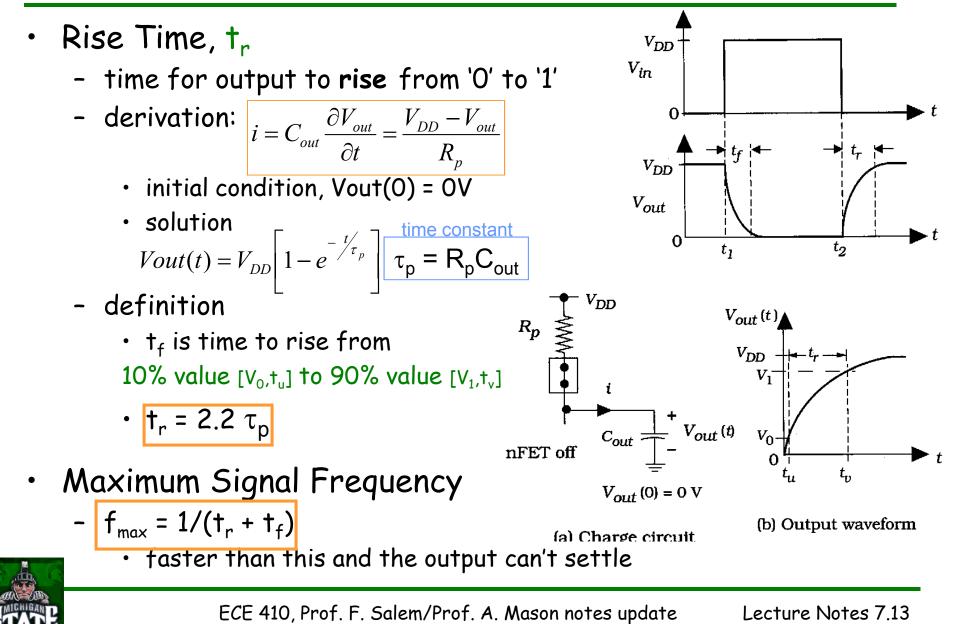

#### **Rise Time**

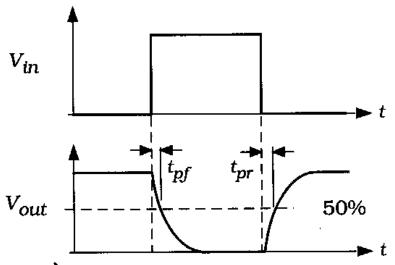

# **Propagation Delay**

- Propagation Delay, t<sub>p</sub>

- measures speed of output reaction to input change

- $t_{p} = \frac{1}{2} (t_{pf} + t_{pr})$

- Fall propagation delay, t<sub>pf</sub>

- time for output to fall by 50%

- reference to input switch

- Rise propagation delay,  $t_{pr}$

- time for output to rise by 50%

- reference to input switch

- Ideal expression (if input is step change)

- $t_{pf} = ln(2) \tau_n$

- $t_{pr} = \ln(2) \tau_p$

- Total Propagation Delay

- $t_p = 0.35(\tau_n + \tau_p)$

Propagation delay measurement:

- from time input reaches 50% value

- to time output reaches 50% value

Add rise and fall propagation delays for total value

# Switching Speed -Resistance

- Rise & Fall Time -  $t_f = 2.2 \tau_n, t_r = 2.2 \tau_p$ ,

- Propagation Delay

- $t_p = 0.35(\tau_n + \tau_p)$

- In General

- delay  $\propto \tau_n + \tau_p$ -  $\tau_n + \tau_p = Cout (Rn+Rp)$

- Define delay in terms of design parameters

- Rn+Rp =  $(V_{DD}-Vt)(\beta_n + \beta_p)$  $\beta_n \beta_p (V_{DD}-Vt)^2$

- Rn+Rp =  $\frac{\beta_n + \beta_p}{\beta_n \beta_p (V_{DD} Vt)}$

$$\tau_{n} = R_{n}C_{out} \qquad \tau_{p} = R_{p}C_{out}$$

$$Rn = 1/[\beta_{n}(V_{DD}-Vtn)] \qquad \beta = \mu Cox (W/L)$$

$$Rp = 1/[\beta_{p}(V_{DD}-|Vtp|)]$$

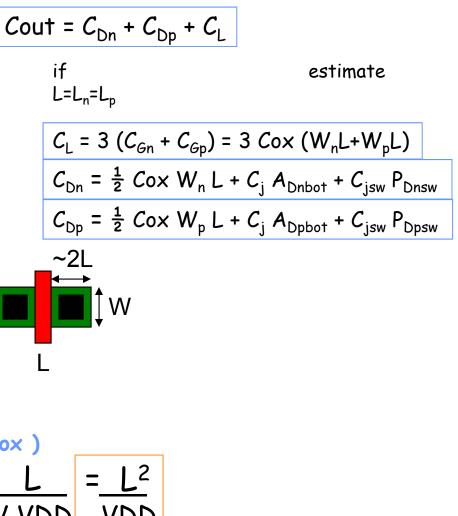

$$Cout = C_{Dn} + C_{Dp} + C_{L}$$

Beta Matched if

$$\beta_n = \beta_p = \beta$$

,

$Rn+Rp = \frac{2}{\beta(V_{DD}-Vt)} = \frac{2L}{\mu Cox W(V_{DD}-Vt)}$

Width Matched if  $W_n = W_p = W$ , and  $L = L_n = L_p$

$Rn+Rp = \frac{L(\mu_n + \mu_p)}{(\mu_n \ \mu_p) Cox W(V_{DD}-Vt)}$

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

• if Vt = Vtn = |Vtp| To decrease R's,  $\bigcup L$ ,  $(MV, (MVDD, (M\mu_{p}, MCox))$

# Switching Speed -Capacitance

- From Resistance we have

- UL,  $(MW, MVDD, (M\mu_p, MCox))$

- but 1 VDD increases power

- Image: Window Cout

- Cout

- Cout =  $\frac{1}{2}$  Cox L ( $W_n + W_p$ ) + C<sub>j</sub> 2L ( $W_n + W_p$ ) + 3 Cox L ( $W_n + W_p$ )

- assuming junction area ~W·2L

- neglecting sidewall capacitance

- Cout  $\approx$  L (W<sub>n</sub>+W<sub>p</sub>) [3 $\frac{1}{2}$  Cox +2 C<sub>j</sub>]

- Cout  $\propto$  L (W<sub>n</sub>+W<sub>p</sub>)

- To decrease Cout,  $\Downarrow L$ ,  $\Downarrow W$ , ( $\Downarrow Cj$ ,  $\Downarrow Cox$ )

- Delay  $\propto$  Cout(Rn+Rp)  $\propto$  L W <u>L</u> = <u>L</u><sup>2</sup> W VDD VDD

Decreasing L (reducing feature size) is best way to improve speed!

## Switching Speed -Local Modification

- Previous analysis applies to the overall design

- shows that reducing feature size is critical for higher speed

- general result useful for creating cell libraries

- How do you improve speed within a specific gate?

- increasing W in one gate will not increase  $C_G$  of the load gates

- Cout =  $C_{\text{Dn}} + C_{\text{Dp}} + C_{\text{L}}$

- increasing W in one logic gate will increase  $C_{\text{Dn/p}}$  but not  $C_{\text{L}}$

- $C_L$  depends on the size of the tx gates at the output

- as long as they keep minimum  $W, C_L$  will be constant

- thus, increasing W is a good way to improve the speed within a local point

- But, increasing W increases chip area needed, which is bad

- fast circuits need more chip area (chip "real estate")

- Increasing VDD is not a good choice because it increases

power consumption

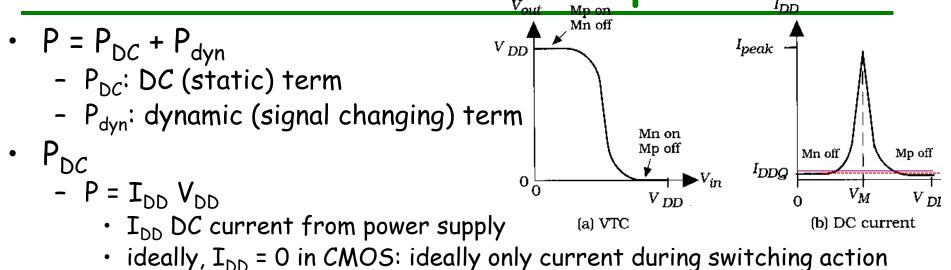

## CMOS Power Consumption

leakage currents cause I<sub>DD</sub> > 0, define quiescent leakage current, I<sub>DDQ</sub> (due largely to leakage at substrate junctions)

$$- \mathsf{P}_{\mathsf{DC}} = \mathbf{I}_{\mathsf{DDQ}} \mathsf{V}_{\mathsf{DD}}$$

- Pdyn, power required to switch the state of a gate

- charge transferred during transition, Qe = Cout VDD

- assume each gate must transfer this charge 1x/clock cycle

- Paverage =  $V_{DD}$  Qe f = Cout  $V_{DD}^2$  f, f = frequency of signal change

- Total Power, P = I<sub>DDQ</sub> V<sub>DD</sub> + Cout V<sub>DD</sub><sup>2</sup> f

Power increases with Cout and frequency, and **strongly** with VDD (second order).

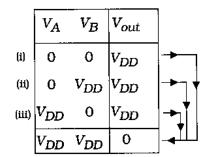

# Multi-Input Gate Signal Transitions

- In multi-input gates multiple signal transitions produce output changes

- What signal transitions need to be analyzed?

- for a general N-input gate with  $M_0$  low output states and  $M_1$  high output states

- # high-to-low output transitions =  $M_0 \cdot M_1$

- # low-to-high output transitions =  $M_1 \cdot M_0$

- total transitions to be characterized =  $2 \cdot M_0 \cdot M_1$

- example: NAND has  $M_0 = 1$ ,  $M_1 = 3$

- don't test/characterize cases without output transition table

- Worst-case delay is the slowest of all possible cases

- worst-case high-to-low

- worst-case low-to-high

- often different input transitions for each of these cases

Lecture Notes 7.19

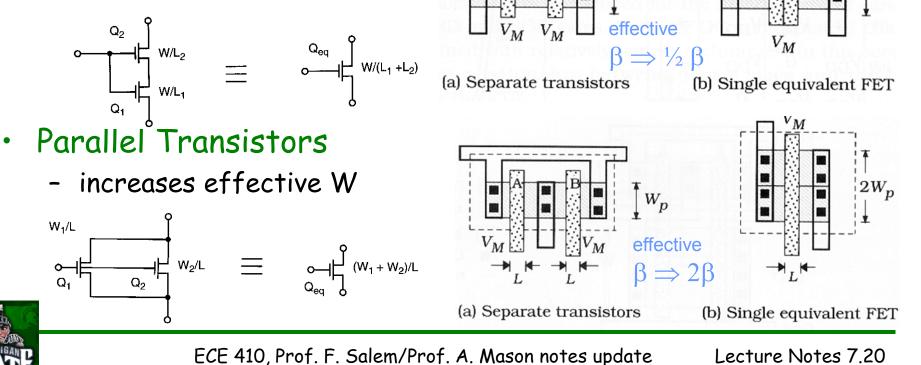

## Series/Parallel Equivalent Circuits

W/L

n+

• (KW)/(KL) for any K

2L

$W_n$

$\beta = \mu Cox (W/L)$

$W_n$

- Scale both W and L

- no effective change in W/L

- increases gate capacitance

#### inputs must be at same value/voltage

- Series Transistors

- increases effective L

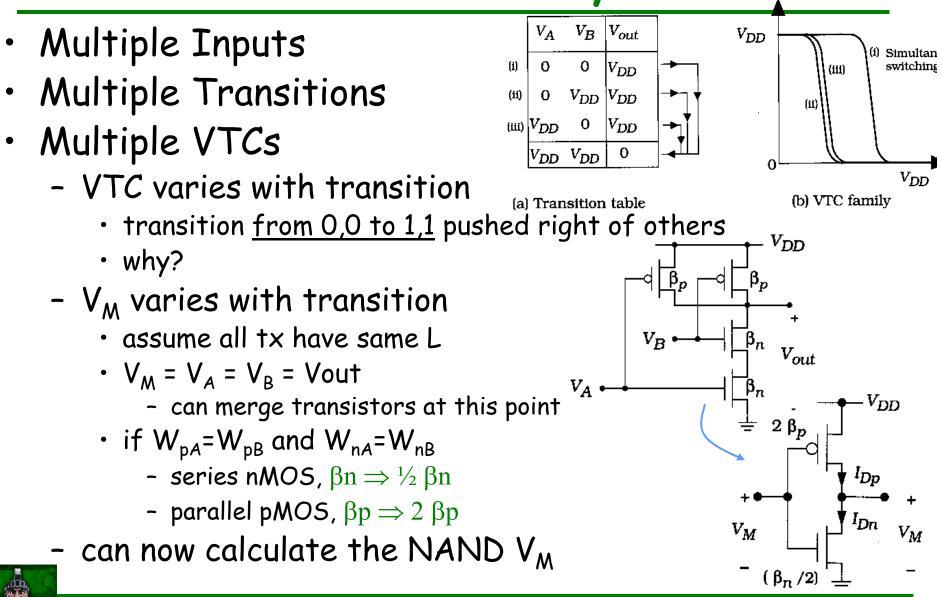

# NAND: DC Analysis

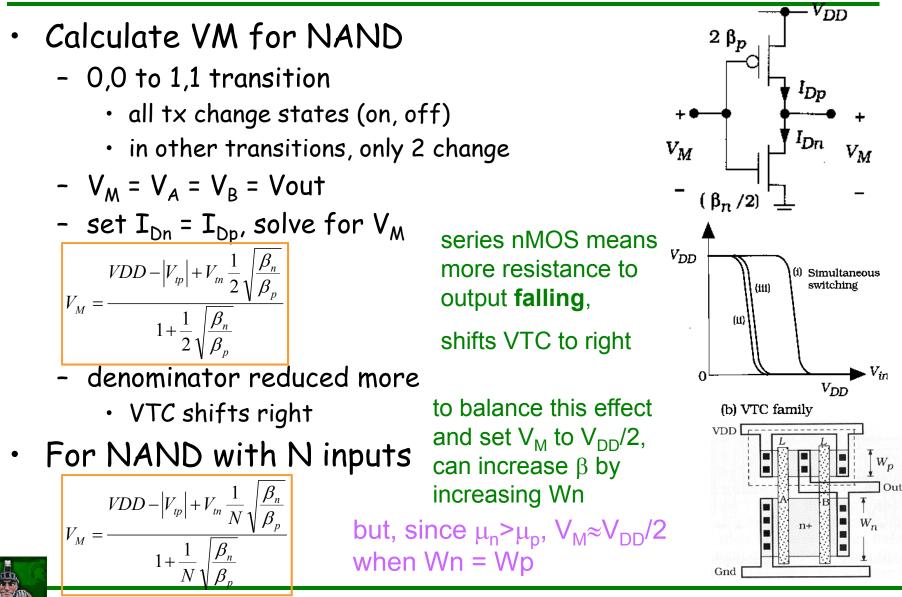

## NAND Switching Point

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

Lecture Notes 7.22

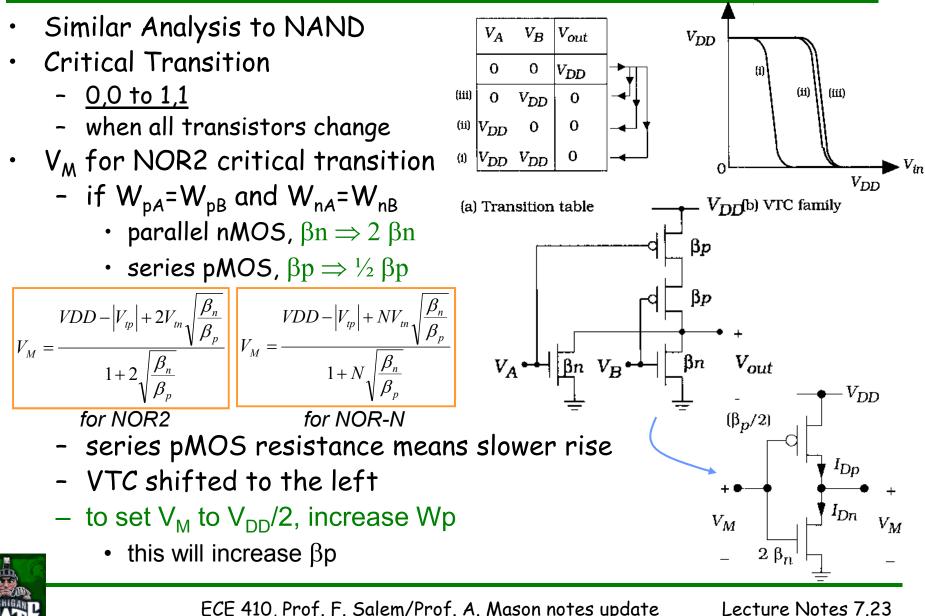

# NOR: DC Analysis

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

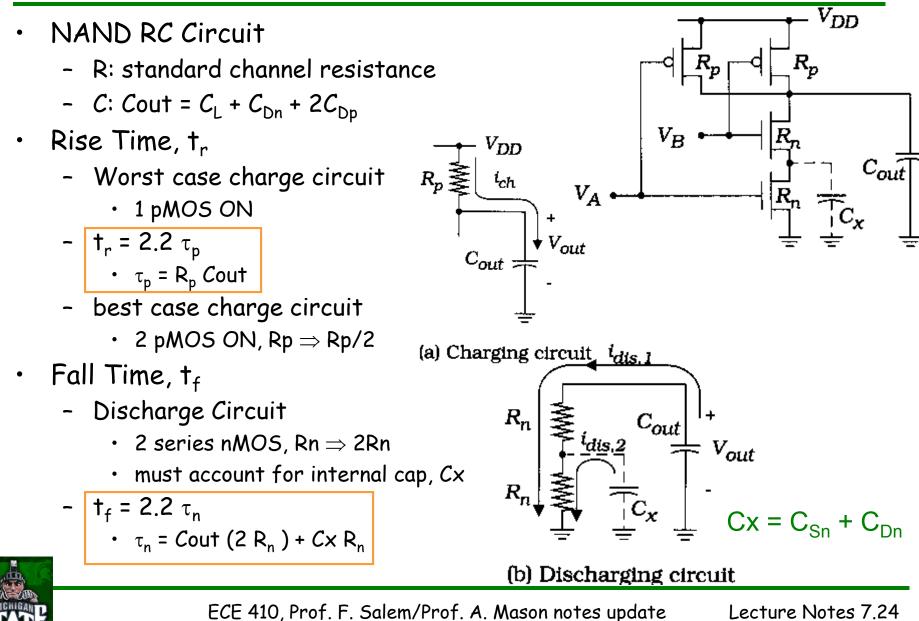

#### NAND: Transient Analysis

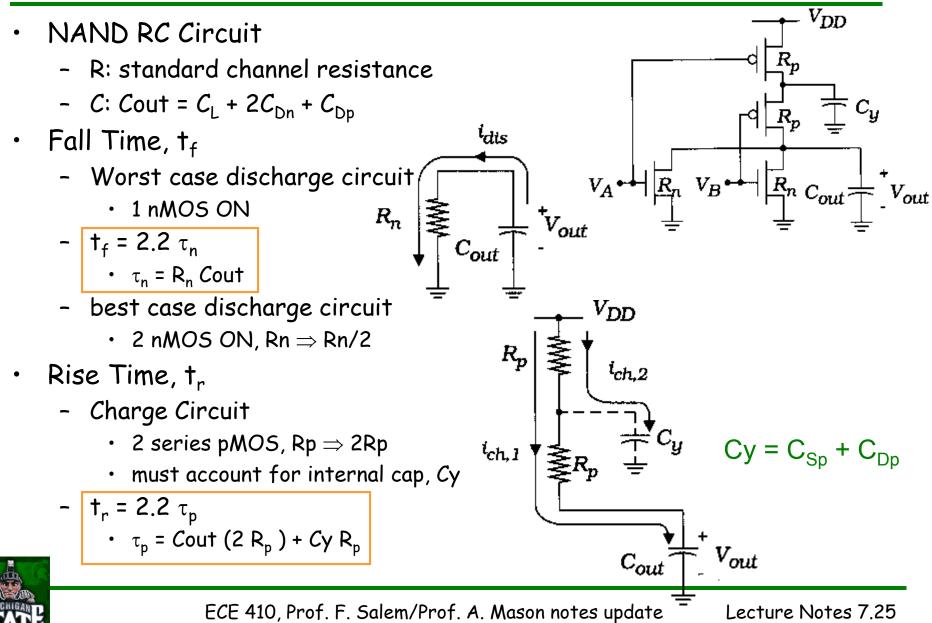

#### NOR: Transient Analysis

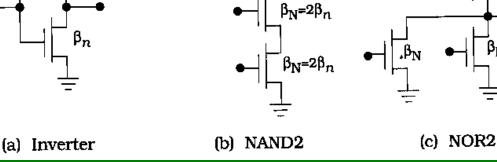

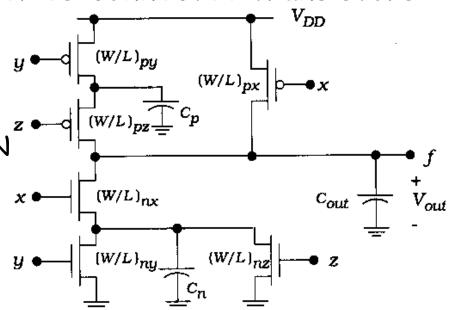

## NAND/NOR Performance

- Inverter: symmetry ( $V_M = V_{DD}/2$ ),  $\beta n = \beta p$

- $(W/L)_p = \mu_n/\mu_p (W/L)_n$

- Match INV performance with NAND

- pMOS,  $\beta_P = \beta p$ , same as inverter

- nMOS,  $\beta_N = 2\beta n$ , to balance for 2 series nMOS

- Match INV performance with NOR

- pMOS,  $\beta_P$  = 2  $\beta_P$ , to balance for 2 series pMOS

- nMOS,  $\beta_N = \beta n$ , same as inverter

- NAND and NOR will still be slower due to larger Cout  $d \beta_p$ •  $d \beta_p = \beta_p$ •  $d \beta_p = \beta_p$ •  $d \beta_p = \beta_p$

- This can be extended to

- 3, 4, ... N input NAND/NOR

gates

$\beta$  is adjusted by

changing transistor

size (width)

$V_{DD}$

ECE 410, Prof. F. Salem/Prof. A. Mason notes update

Lecture Notes 7.26

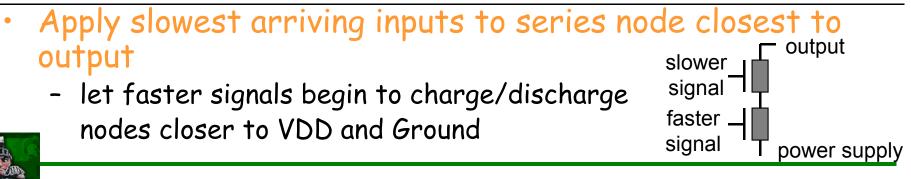

# NAND/NOR Transient Summary

- Critical Delay Path

- paths through series transistors will be slower

- more series transistors means worse delays

- Tx Sizing Considerations

- increase W in series transistors

- balance  $\beta_n/\beta_p$  for each cell

- Worst Case Transition

- when all series transistor go from OFF to ON

- and all internal caps have to be

- charged (NOR)

- discharged (NAND)

## Performance Considerations

- Speed based on  $\beta n,\,\beta p$  and parasitic caps

- DC performance (V<sub>M</sub>, noise) based on  $\beta n/\beta p$

- Design for speed not necessarily provide good DC performance

- Generally set tx size to <u>optimize speed</u> and then test DC characteristics to ensure adequate noise immunity

- Review Inverter: Our performance reference point

- for symmetry ( $V_M = V_{DD}/2$ ),  $\beta n = \beta p$

- which requires  $(W/L)_p = \mu_n/\mu_p (W/L)_n$

- Use inverter as reference point for more complex gates

Lecture Notes 7.28

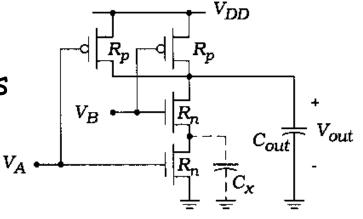

## **Timing in Complex Logic Gates**

Critical delay path is due to series-connected transistors

• Example:

$$f = \overline{x(y+z)}$$

- assume all tx are same size

- Fall time critical delay

- worst case, x ON, and y or z ON

-

$$t_f = 2.2 \tau_n$$

•

$$\tau_n = Rn Cn + 2 Rn C_{out}$$

-

$$C_{out} = 2C_{Dp} + C_{Dn} + C$$

-  $Cn = 2C_{Dn} + C_{cn}$

- worst case, y and z ON, x OFF

•

$$t_r = 2.2 \tau_p$$

•  $\tau_p = Rp Cp + 2 Rp C_{out}$

-  $C_{out} = 2C_{Dp} + C_{Dn} + C_l$

-  $Cp = C_{Dn} + C_{Sn}$

size vs. tx speed considerations  $\|Wnx \Rightarrow \Downarrow Rn$  but  $\|Cout$  and  $\|Cn$  $\Downarrow Wny \Rightarrow \Downarrow Cn$  but  $\|Rn$

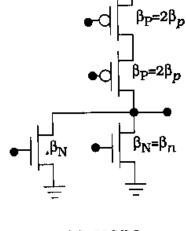

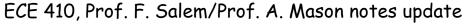

# Sizing in Complex Logic Gates

- Improving speed within a single logic gate  $\beta_{p=2\beta_{p}}$

- An Example: f=(a b+c d) x

- nMOS

- discharge through 3 series nMOS

- set  $\beta_N = 3\beta n$

- pMOS

- charge through 2 series pMOS

- set  $\beta_P = 2\beta p$

- but, Mxp is alone so  $\beta_{P1}$  =  $\beta p$

- but setting  $\beta_{P1}$  = 2 $\beta$ p might make layout easier

- These large transistors will <u>increase capacitance</u> and <u>layout area</u> and may only give a small increase in speed

Advanced logic structures are best way to improve speed

$\beta_N$

$V_{DD}$

β<sub>P1</sub>

$\beta_{N1}=3\beta_n$

$\beta_N = 3\beta_n$

$\beta_N = 3\beta_n$

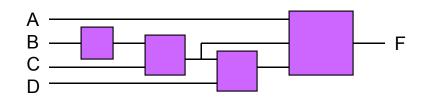

# Timing in Multi-Gate Circuits

• What is the worst-case delay in multi-gate circuits?

- too many transitions to test manually

- Critical Path

- longest delay through a circuit block

- largest sum of delays, from input to output

- intuitive analysis: signal that passes through most gates

- not always true. can be slower path through fewer gates

0 0 1

1 1 0 0

1 1 1 1

1 0 0 0 | 0 - B<sup>1</sup>

#### Power in Multi-Input Logic Gates

Inverter Power Consumption

$$-P = P_{DC} + P_{dyn} = V_{DD}I_{DDQ} + C_{out}V_{DD}^2f$$

- assumes gates switch output state once per clock cycle, f

- Multi-Input Gates

•  $a = p_0 p_1$

- same DC component as inverter,  $P_{DC} = V_{DD}I_{DDQ}$

- for dynamic power, need to estimate "activity" of the gate, how often will the output be switching

-

$$P_{dyn} = aC_{out}V_{DD}^2f$$

, a = activity coefficient

- estimate activity from truth table

-  $p_0$  = prob. output is at 0

-  $p_1$  = prob. of transition to 1

NOR NAND

| 1           | 1           |

|-------------|-------------|

| 0<br>0<br>0 | 1<br>1<br>0 |

|             | 0 75        |

p0=0.75 p0=0.25 p1=0.25 p1=0.75 a=3/16 a=3/16

Lecture Notes 7.32

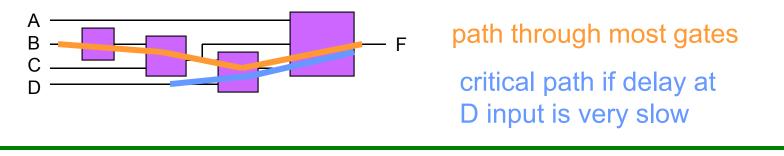

Note: no connections to VDD-Ground. Input signal, Vin, must drive TG output; TG just adds extra delay

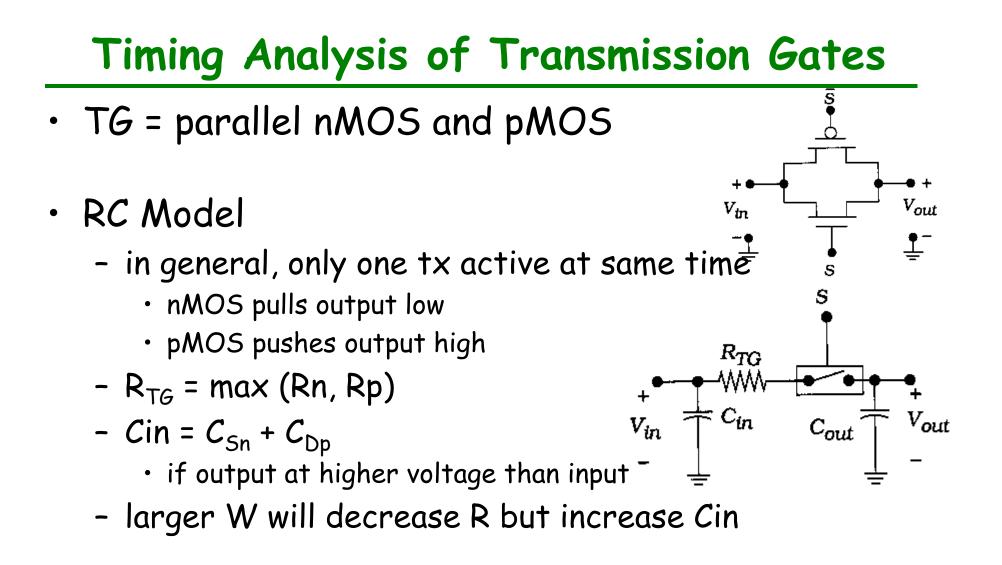

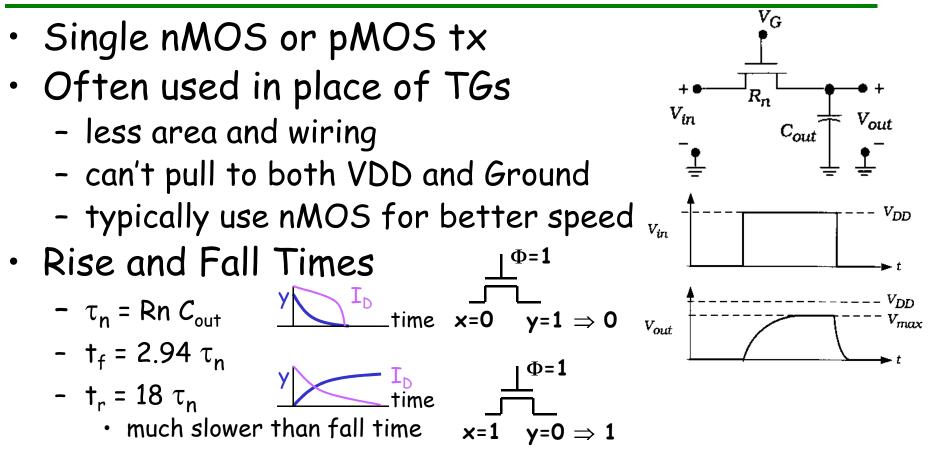

#### Pass Transistor

- nMOS can't pull output to VDD

- rise time suffers from threshold loss in nMOS