# Xilinx Products, Solutions and Technology for ADAS/AD

Paul Zoratti Xilinx Director: Automotive Solutions & Architects

January 2021

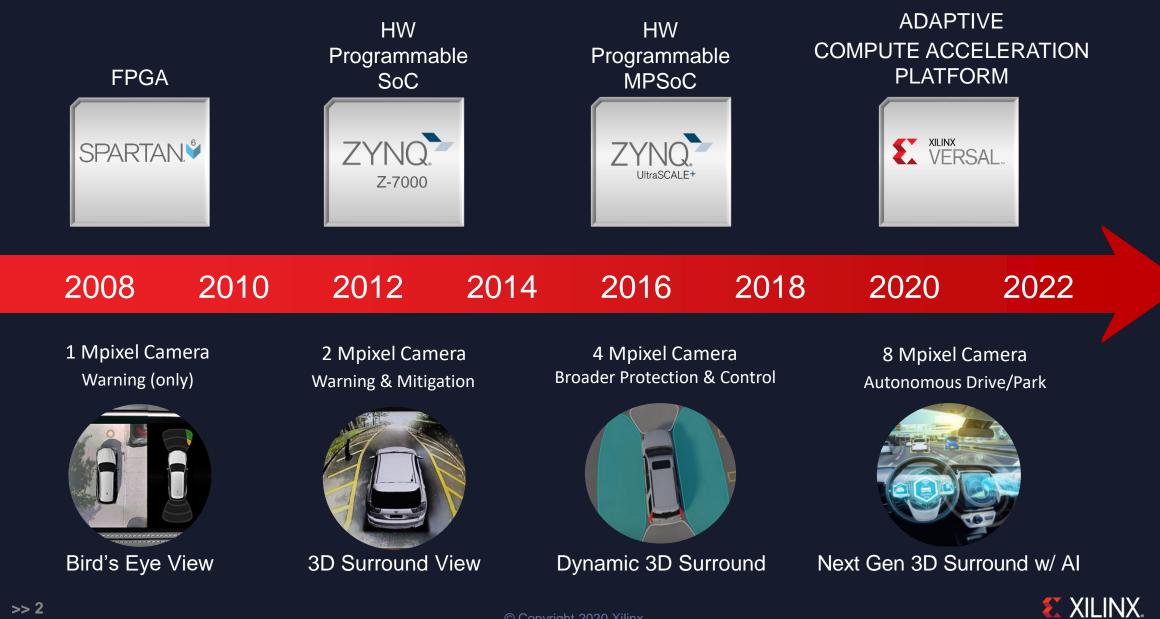

## **Xilinx Product Evolution in Automotive**

© Copyright 2020 Xilinx

### Xilinx All Programmable SoC and MPSoC A Game Changing Technology in Automotive

ELANDIA AZANZZA H 44 11 ZZ ZYNQ. 16FF+ UltraSCALE+

FRGL

Vider Graphic

Real Time

Os

ARAA

Software Programmable Hardware

Programmable

21/15

SoC: System on Chip MPSoC: Multi-Processor System on Chip **E** XILINX.

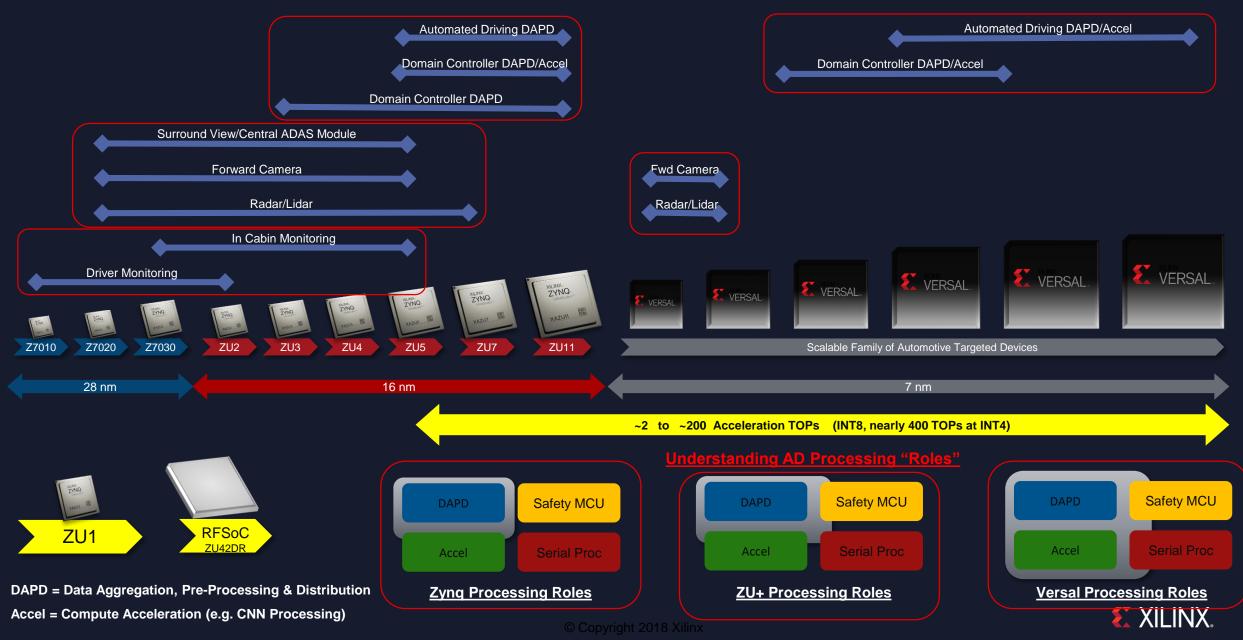

# Xilinx Automotive SoC & ACAP Applications

## Field Programmable Gate Array Based SoC's

## Field Programmable Gate Array Based SoC's

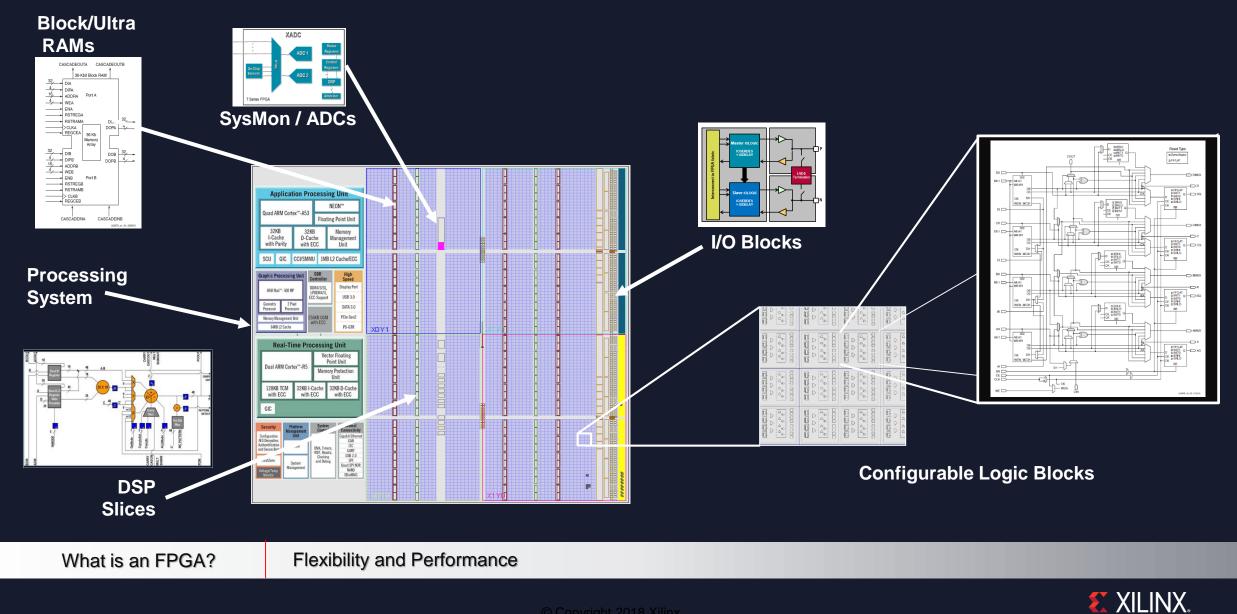

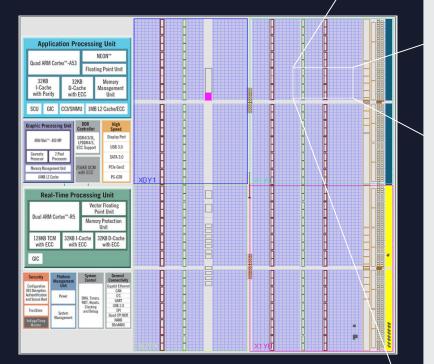

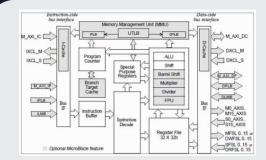

#### FPGA Fabric = Programmable Logic

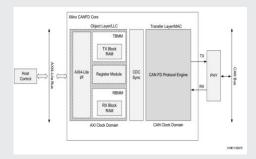

Common Processor Peripherals (e.g. CAN / CAN-FD)

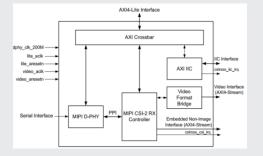

Application Focused Connectivity (e.g. MIPI CSI-2 Controller and D-PHY)

> Inference DNN Processing Engines

> MicroBlaze 32-bit Soft Processor

Highly Parallelized and Customized

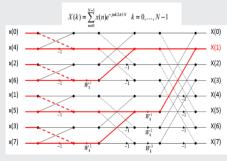

DSP Acceleration (e.g. FFT)

Unique, Differentiating User-Defined Functions or Pipelines of Functions

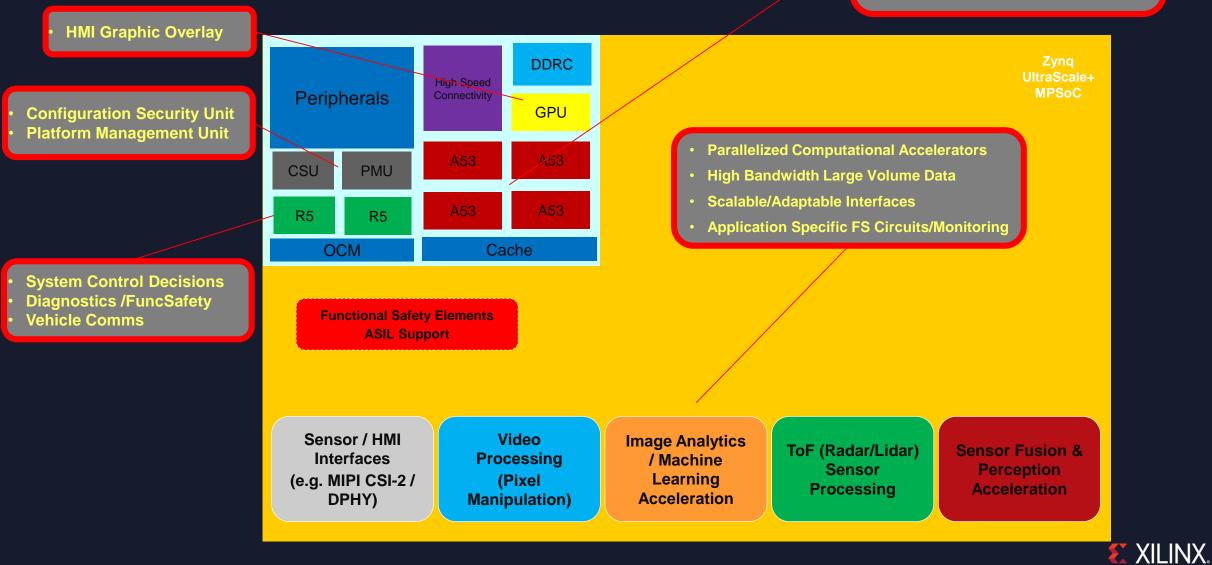

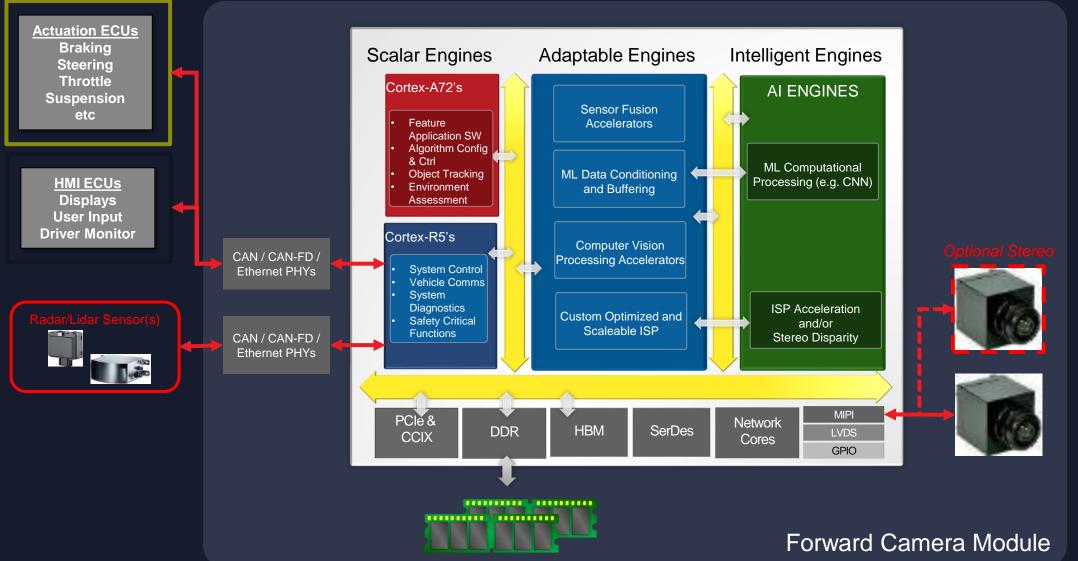

#### Functional Partitioning for Zynq UltraScale+ A Heterogenous Processing Platform

- Feature Application SW

- Algorithm Configuration & Control

- Object Tracking

- Environment Assessment

- Feature State Control

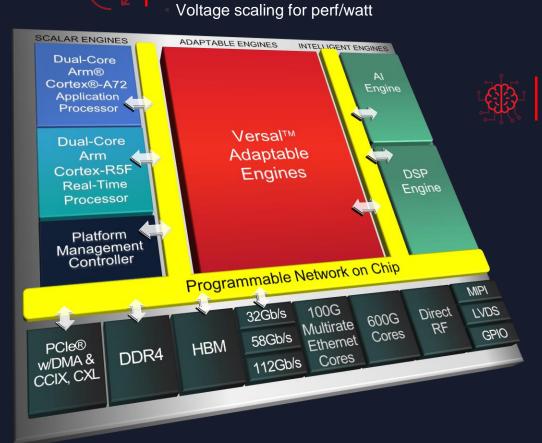

# **Versal Architecture Overview**

Scalar Engines Platform Control Embedded Edge Compute

PCIe Gen4/5 & CCIX 2X PCIe & DMA bandwidth Cache-coherency

2000005

DDR4 Memory 3200-DDR4, 4266-LPDDR4 2X bandwidth/pin

Transceiver Leadership Broad range, 1G →112G 58G in mainstream devices (32G in XA)

Adaptable Engines 2X compute density

> Intelligent Engines (DSP) Al Compute Diverse DSP Workloads

Programmable NoC Guaranteed Bandwidth Enables SW Programmability

Programmable I/O Any interface or sensor Includes 3.2Gb/s MIPI

### Forward-Looking Camera Partitioning Example

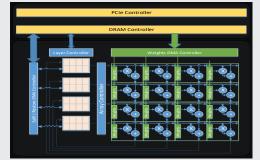

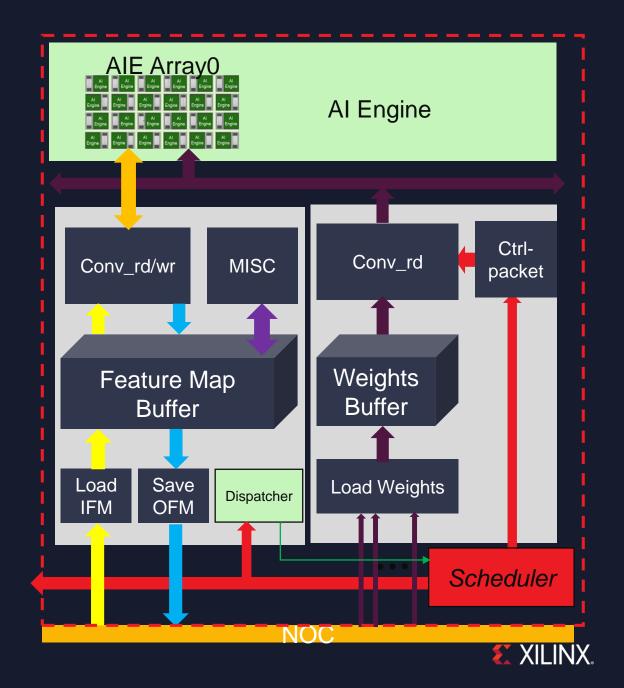

#### ML Processing on Versal DPU Architecture Design

- > Target: Configurable/Scalable DPU

- > DPU = Deep-learning Processing Unit

- A powerful combination of PL and AIE resources to realize optimized ML Processing

- > AIE: Conv engine

- PL: Depthwise Conv, Elementwise, Pooling, softmax and Instruction scheduler

- Instruction: Control the data flow between AIE and PL. Control different engines in MISC.

# **Xilinx Solutions Slides**

From horizontal IP to partner application specific solutions

© Copyright 2018 Xilinx

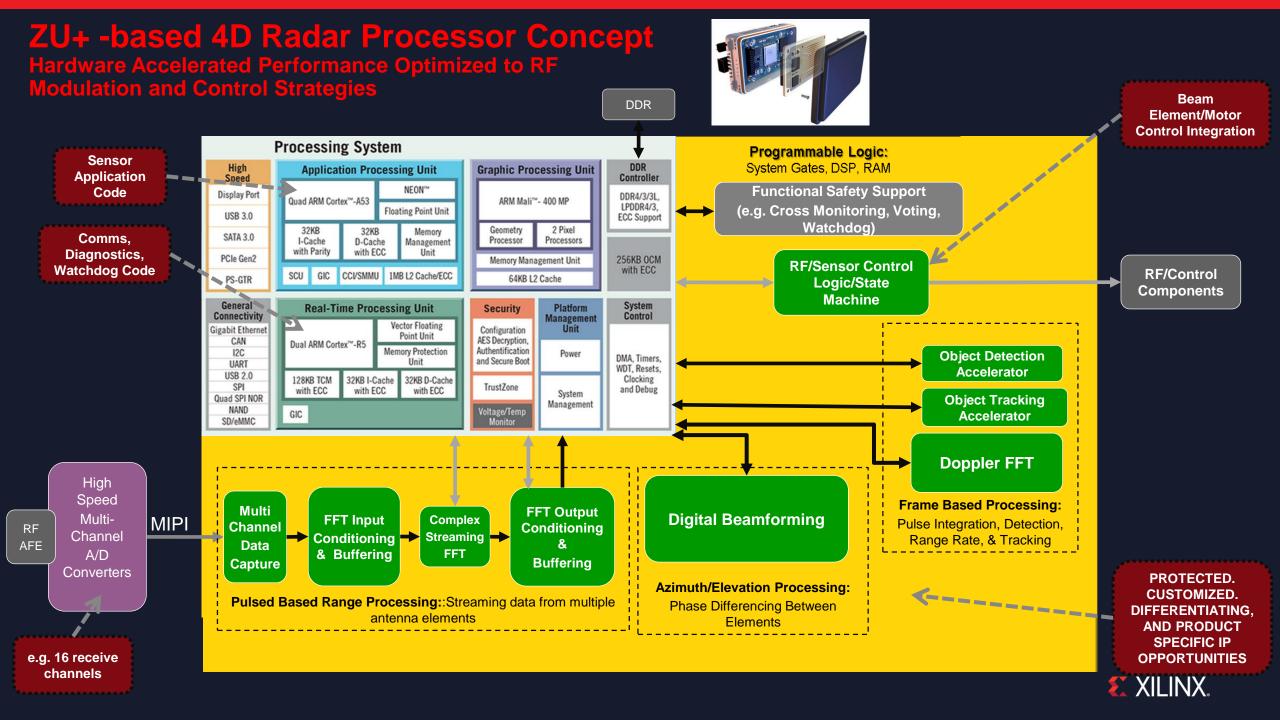

### Xilinx Radar/Lidar ML Processing Pointpillars on Lidar Data Example

#### **Demo specification**

- > Model: Pointpillars

- > Framework: Pytorch

- > Dataset: Kitti, 64-channel, 1~2Mpoints/sec

- > 25fps (40ms latency), 1x DPU B4096 @ 300MHz on ZCU102

- > General access in Vitis AI 1.3

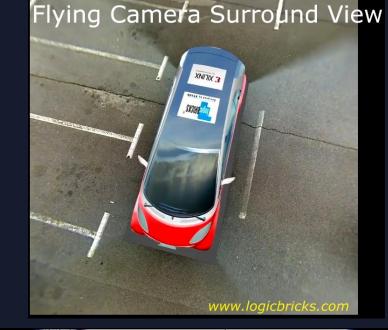

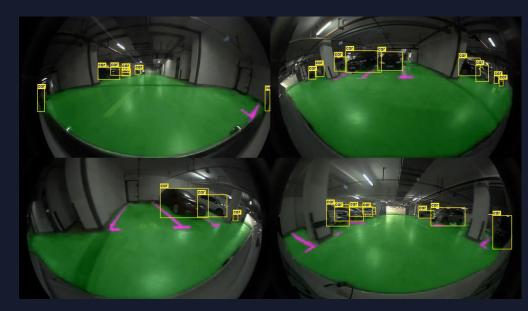

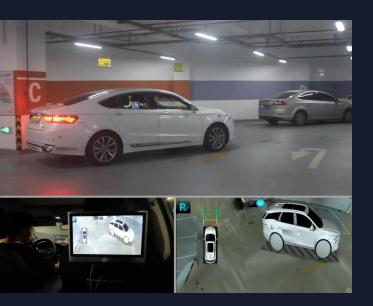

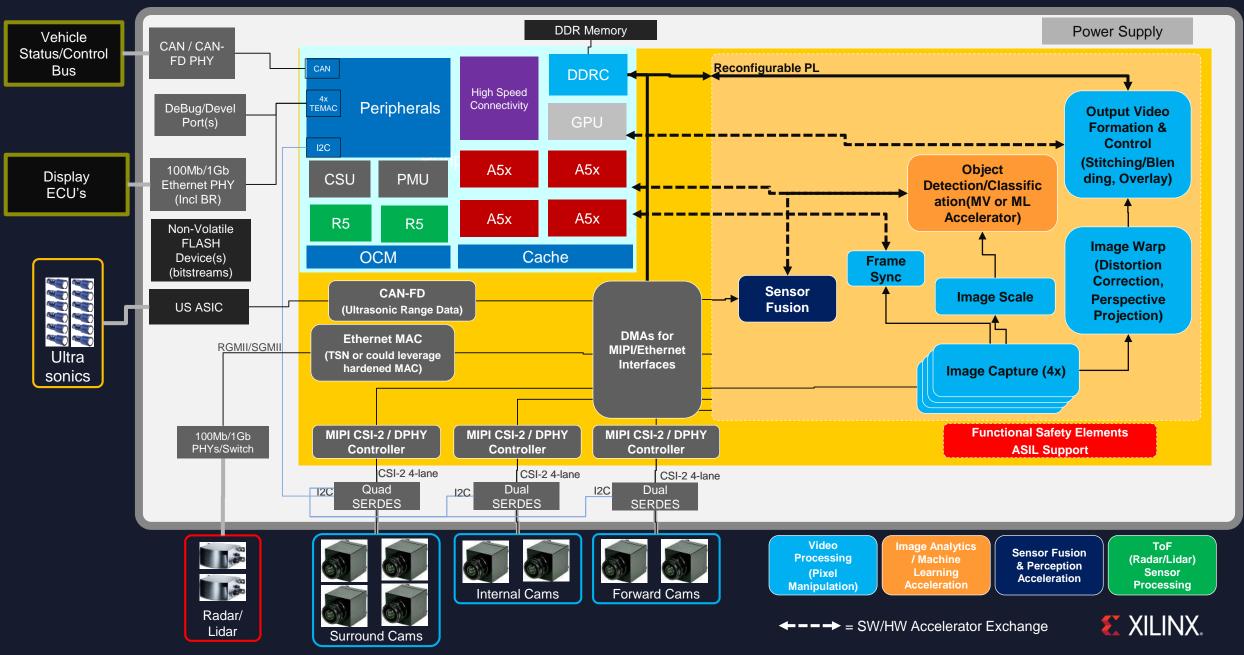

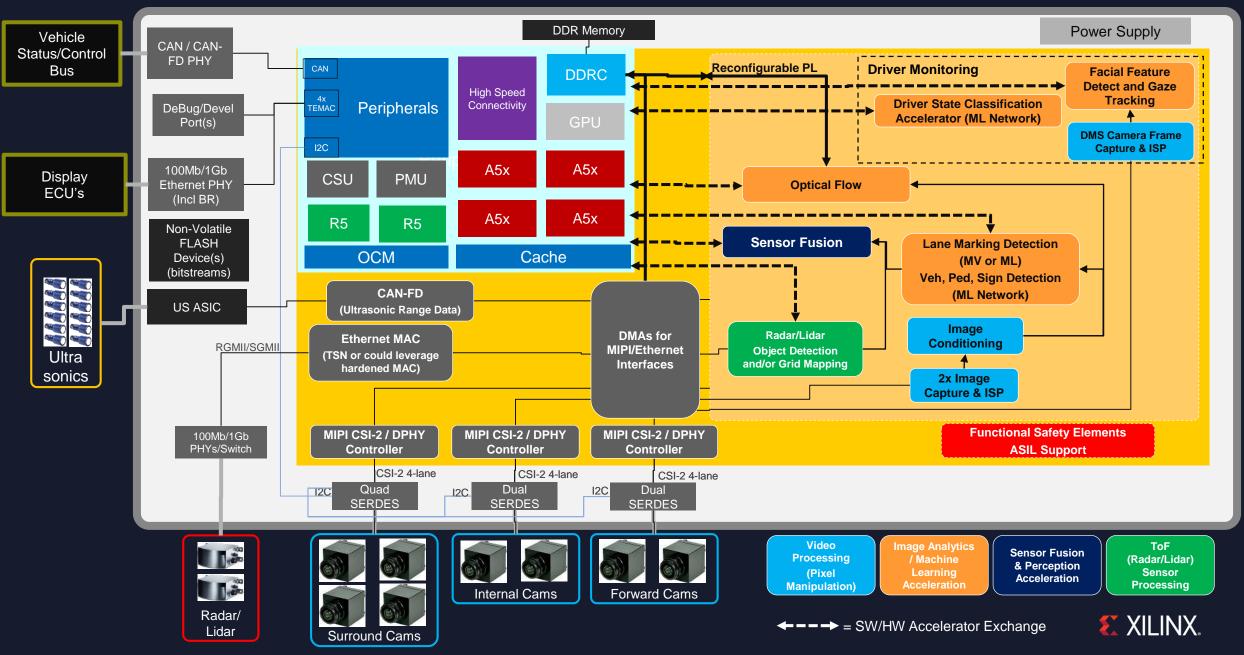

## **Viewable System Processing**

- From simple rear view camera to mirror enhancement and replacement to 3D surround view with flying camera

- Image Warping, Stitching (Panoramic, Bowl, other), and View Transformation in a scalable product family to cost effectively meet sensor and system performance needs

- Full development platform available from Xilinx Ecosystem Partner Xylon

Resulting Image - 360deg Panoramic View

www.logicbricks.com

© Copyright 2018 Xilinx

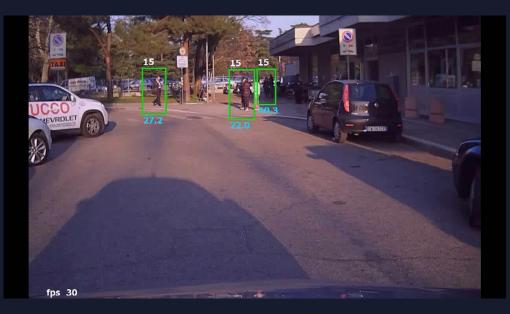

# **Vision Analytics Processing**

From traditional machine vision to the latest and innovative ML vision processing

A new breed of Xilinx Ecosystem Partner

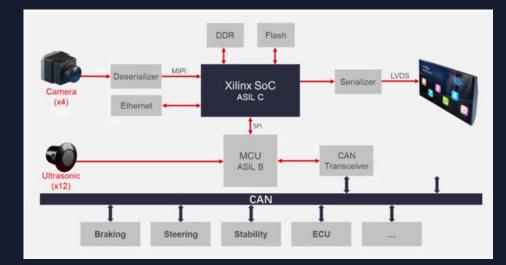

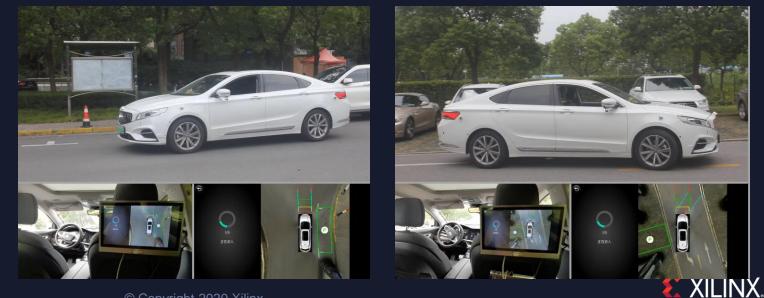

#### **Automated Parking Functionality as Foundation for Domain Controller and other AD initiatives**

**Combining Surround View, ML Processing** and Vehicle Control into an automated parking feature

© Copyright 2020 Xilinx

## **Some Xilinx Sourced Relevant IP**

- Connectivity

- MIPI CSI, MIPI DSI, HDMI, Display Port

- Ethernet TSN, SLVS

- Video Processing

- Mixer, Scaler, Framebuffer, Video Controller

- ISP DPC, Demosaic, Gamma Correction, AWB/AE, HDR, Color Correction, Noise Reduction, etc.

- Transformation, Image Warping and Stitching

- Image Processing

- OpenCV Libraries e.g. Harris Corner, Optical Flow, Stereo Disparity, , HoG/SVM, Hough Transform

- General

- Windowing, FFT, Kalman Filter, SVD, FIR Filter, etc.

# Xilinx Unique Technology Advantages

OTA HW Dynamic Function Exchange Functional Safety

© Copyright 2018 Xilinx

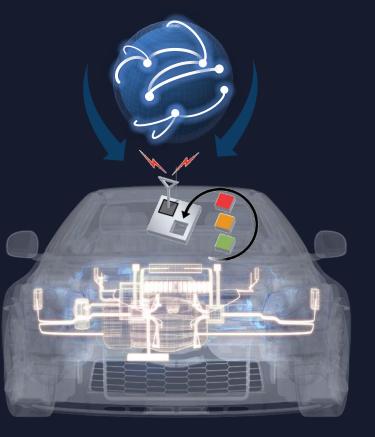

# **Over-the-Air Silicon Updates (OTA)**

- Over-The-Air update to enable modifications for Software AND Hardware

- Evolve neural network implementations over time

- Add new features or update mission critical functions

- Future proof for emerging security threats

- Update safety algorithms

- Perform remediation or corrective action

Upgrade Hardware of Deployed Systems

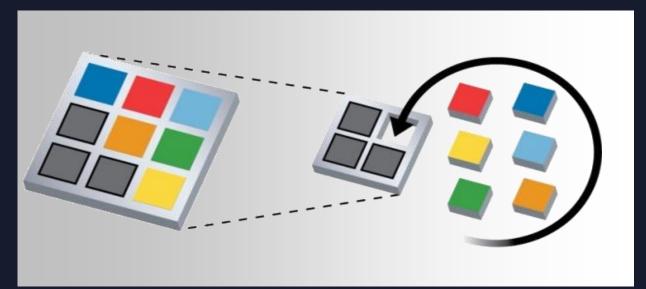

#### Dynamic Function eXchange (DFX) Efficient, Low Latency Exchange of Functions

Leverages the ability to reprogram portions of Xilinx Programmable Logic (PL) fabric while the remainder of the fabric remains fully functional

Result is "silicon re-use" for uniquely efficient, cost-effective implementation of mutually exclusive applications

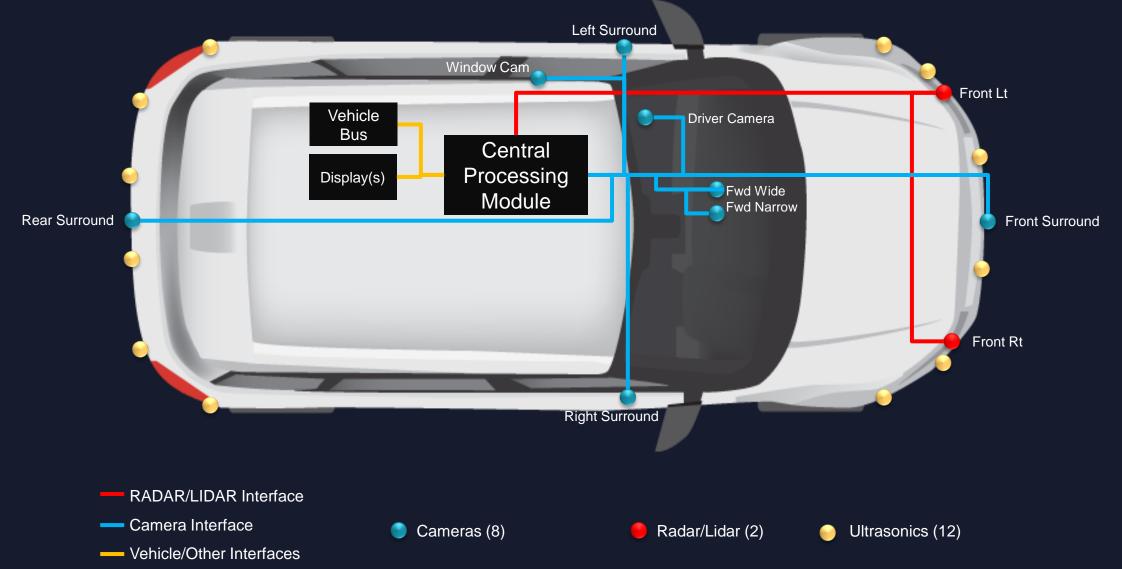

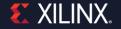

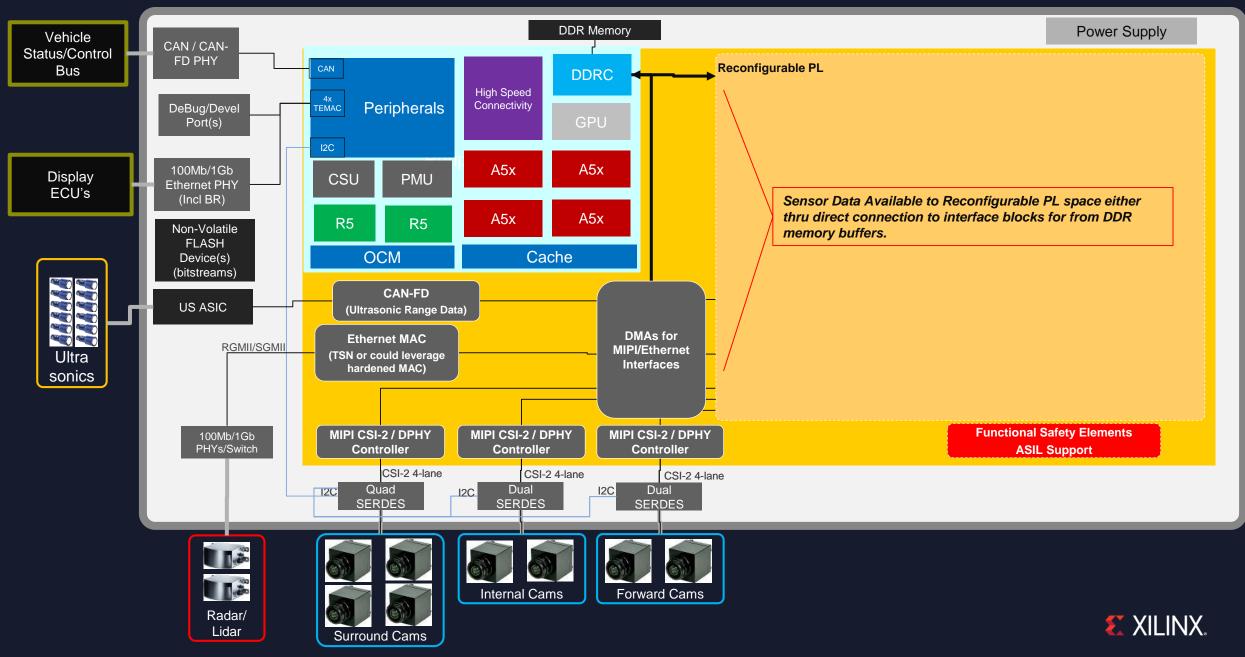

# **Example Multi-Feature Sensor Configuration**

# **Mutually Exclusive Feature Bundles**

#### **PreDrive Security**

Low Speed/Parking

**Highway Driving**

#### Dynamic Function eXchange (DFX) Efficient, Low Latency Exchange of Functions

Leverages the ability to reprogram portions of Xilinx Programmable Logic (PL) fabric while the remainder of the fabric remains fully functional

Result is "silicon re-use" for uniquely efficient, cost-effective implementation of mutually exclusive applications

Silicon Re-Use = Lower Density Device = Lower Cost & Power

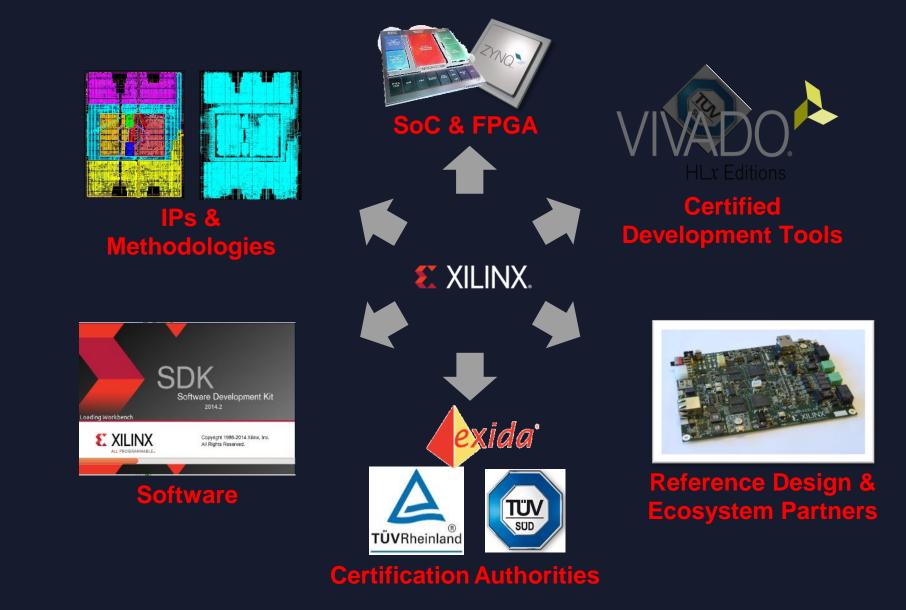

## **Xilinx Functional Safety Solutions**

**XILINX**.

© Copyright 2018 Xilinx

# Summary

#### Cost-effective & Scalable Device Families

Platform design for BoM scaling to various ADAS / AD Sensor and Feature Bundles

#### Unique IP portability

IP designs migrate to / from Distributed Sensors to Centralized Modules

- Optimal Partitioning Between System Software and Hardware Accelerators

- Integrated Sensor Data Aggregation, Compute Acceleration, and Scalar Processing

- Power Efficient, High Utilization AI / ML Inference

- >> More effective use of TOPs

- Customer-owned (Proprietary) or Xilinx / Partner Licensable IP / Accelerators

- Market Differentiation / Leadership and Fast Time to Market

Independent (Isolated), Simultaneous, and Optimized Processing Pipelines

- Lowest latency sensor data paths and sensor fusion

- In-field SW and HW upgradability (Unique OTA-HW)

- Unparalleled ability to update system capabilities / performance

Efficiently address multi-feature systems requirements with minimized cost & power

# **XILINX**.

# **Thank You**

© Copyright 2018 Xilinx